屏蔽ADC网络可以帮助避免噪声耦合 有助于提高性能

描述

逐次逼近寄存器(SAR)模数转换器(ADC)通常用于需要中到高分辨率的应用中。 SAR ADC的主要优点是高性能,低功耗和小芯片面积。

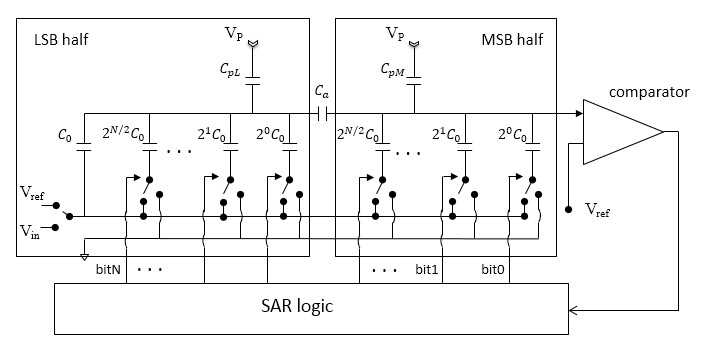

为了减小芯片面积,使用分离电容DAC阵列。该架构如图1所示。分离电容阵列既可用作DAC,也可用作采样保持电路。衰减器电容器C a用于将阵列分成两个子阵列。在采样阶段之后,阵列输出端的输出电压为V in - V ref ,其中V in是ADC输入电压,V ref 是参考电压。在近似阶段期间,输出电压达到V ref + V qe 的值,其中V qe 是量化误差。导致该值的DAC输入是转换结果。但是有一些误差源必须最小化。

图1:分离电容SAR ADC

2。误差来源

2.1寄生电容

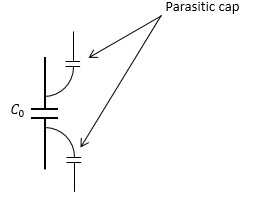

在DAC的每个电容上阵列,上板和下板都有一些寄生帽。下板上的寄生电容对于SNR计算并不重要,因为它在逐次逼近过程中不参与电荷共享。寄生帽的价值取决于各种因素,如布局,制造工艺等;加上它随着死亡而变化。

图2:寄生帽

2.2电容不匹配

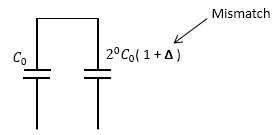

不可能在芯片上制作精确值的电容。与Parasitics一样,不匹配也取决于布局和制造过程。图3显示了两个电容,第二个电容应具有第一个双倍值,但其值随delta变化。通过适当的布局,可以实现低至0.1%的delta值。

图3:不匹配

2.3来自附近网络的耦合

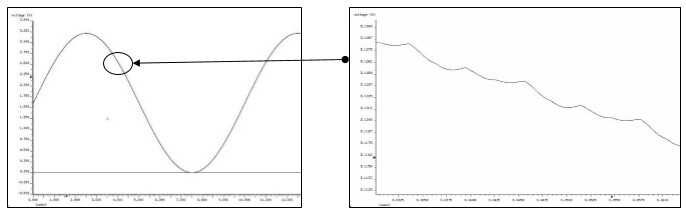

如果输入或参考电压的相邻网络正在切换,那么它们可以耦合噪声。图4显示了输入正弦波;在放大的快照中可以看到与附近网络的正弦波耦合的噪声。

图4:输入噪声

3。分析

为了研究各种因素对ADC信噪比的影响,采用了行为模型[2]。在每次模拟中,取出1024个正弦波样本并将其转换为12位数字值,然后计算SNR。进行了1000次这些模拟,最后得到了所有SNR值的RMS值。

DAC的输出电压可按如下方式计算:

其中C sumL是阵列的LSB一半的总电容,C sumM是MSB一半阵列的总电容。 N是DAC使用的位数, C 0是单位电容值, 等于阵列MSB一半的相应DAC位。

等于阵列MSB一半的相应DAC位。

运行SAR算法进行转换,上面的方程用于通过切换找到V out 从MSB到LSB的逐位比特。

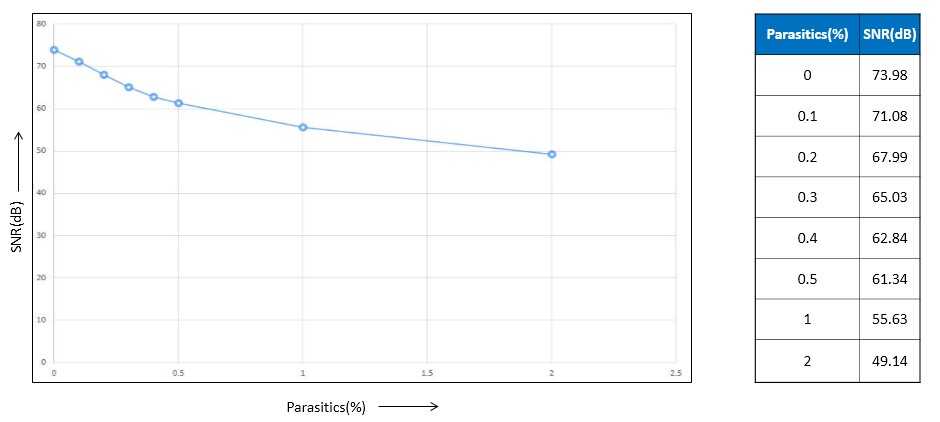

3.1寄生电容对SNR的影响

随机值(介于0之间)在每次模拟中产生每个电容器的寄生电容的最大值(%)。进行1000次这样的模拟,最后计算SNR的RMS值。图5显示了SNR随寄生效应的变化,表中寄生值是寄生电容的最大可能值。我们可以看到只有0.2%的寄生电容可以导致6dB的SNR下降。

图5:SNR与寄生效应

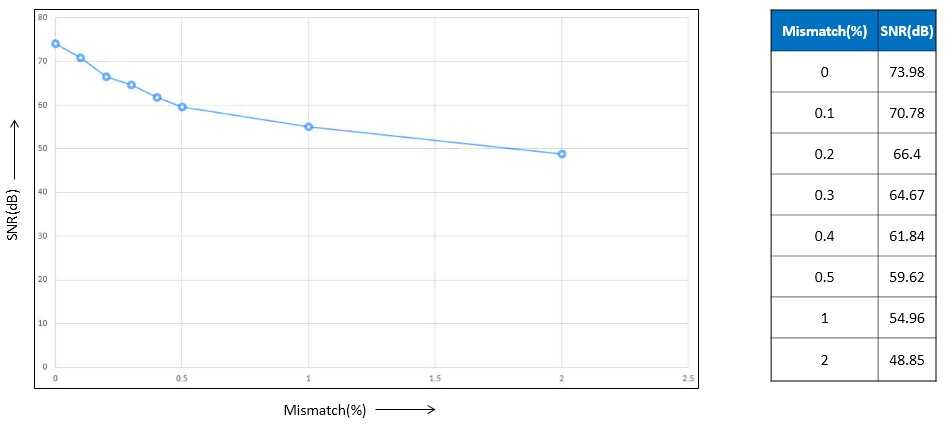

3.2不匹配的影响

这里也针对不同的最大不匹配值,为每个电容器生成随机值,然后转换完成。完成1000次这样的转换,最后计算SNR的RMS值。电容之间0.1%的不匹配会使SNR降低3.2 dB。

图6:SNR与失配

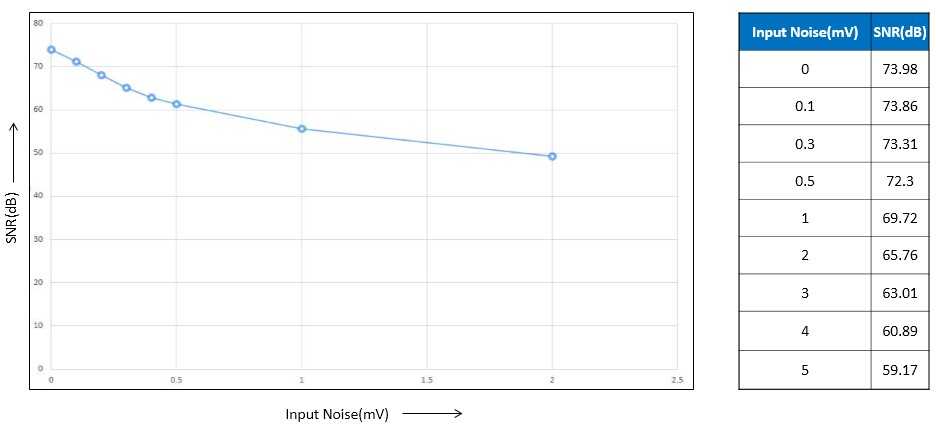

3.3耦合的影响

这里我们得到噪声的随机值(从0到最大值),它被加到输入信号值上。对于每次转换,有1024个样本,因此每次转换都会添加1024个不同的噪声值,并完成1000次转换,然后计算SNR的RMS值。

图7:SNR与输入噪声

4。结论

上述分析表明,附近网络耦合的电容,寄生电容或噪声之间的小的不匹配会如何降低SAR ADC的性能。这种高灵敏度使得必须在布局阶段正确匹配电容器,并在片上SAR算法中使用各种校准技术来提高其性能。屏蔽ADC网络可以帮助避免噪声耦合,这将再次有助于提高性能。

-

面向电路的噪声耦合抑制技术2023-11-29 248

-

请问AD2S1210外围电路中,更改哪些元件有助于提高抗干扰能力?2018-08-01 0

-

提高ADC分辨率并降低噪声的方法2019-02-26 0

-

LTC1436-PLL低噪声开关稳压器有助于控制EMI2019-07-19 0

-

如何使用LTspice模拟 SAR ADC 模拟输入?2022-04-12 0

-

ADC性能提高的建议2012-03-22 1964

-

高性能ZVS降压稳压器有助于消除提高宽输入电压范围负载点应用功率吞吐量的障碍2016-01-07 573

-

现代DAC和DAC缓冲器有助于提升系统性能、简化设计2016-01-04 761

-

有助于提高FPGA调试效率的技术与问题分析2018-11-28 2143

-

可减少负载点转换器模块的噪声耦合的PCB布局2019-02-11 1794

-

燃料电池技术获新突破 铂钴颗粒将有助于提高性能2019-07-26 1161

-

质子传导膜效率提高有助于氢燃料电池性能提高2020-03-27 2942

-

有助于检测心率的设备2022-11-17 344

-

相位噪声曲线有助于系统测试2023-03-08 839

-

ADC噪声:有关模拟输入的更多信息2023-06-30 470

全部0条评论

快来发表一下你的评论吧 !