FPGA配置状态字寄存器失败的解决方法

可编程逻辑

描述

去年第一次跟着师父去做产品的EMC实验的时候,颇有收获在此整理分享给大家。

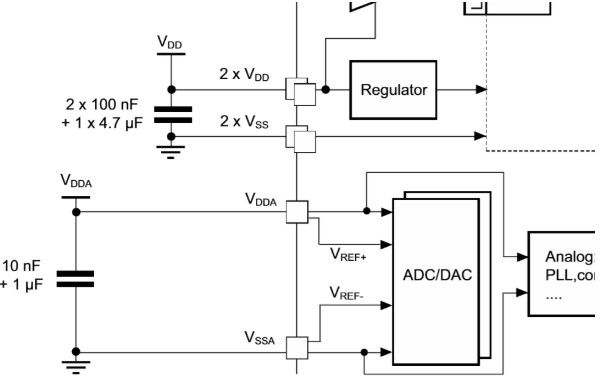

以前在学生时代的时候对于MCU退耦电容的作用理解的并不是很透彻,导致不是很关心退耦电容的放置位置,退耦电容在芯片的手册中是如下声明的:

手册上说明: Each power supply pair (VDD/VSS, VDDA/VSSA etc.) must be decoupled with filtering ceramic capacitors as shown above. These capacitors must be placed as close as possible to, or below, the appropriate pins on the underside of the PCB to ensure the good functionality of the device.

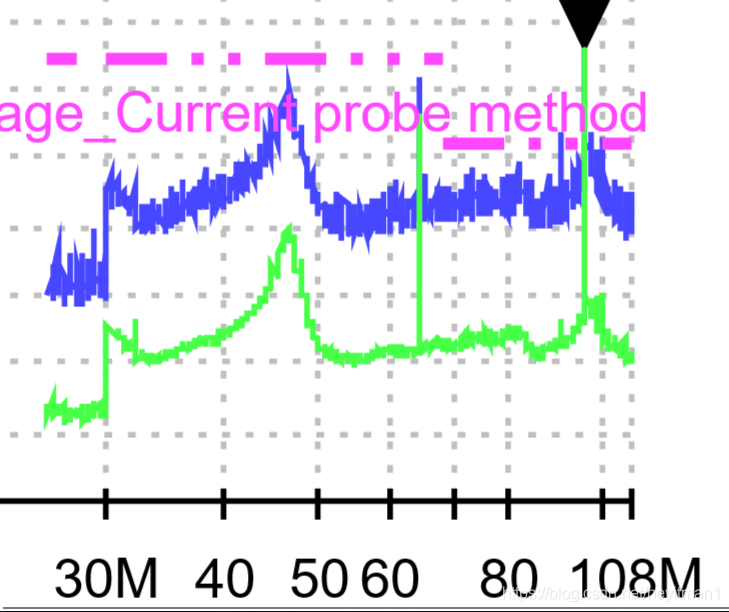

意思是为了给MCU提供更好的工作环境,退耦电容必须尽可能靠近MCU。而当时设计的PCBA因布板区域等限制,忽略了此规定,退耦电容放置的离MCU供电引脚相对较远。导致在做CE02 电流法时在 32M,64M,96M产生了尖峰下图所示,楼主用的MCU是8M的主频很明显这是晶振的倍频:

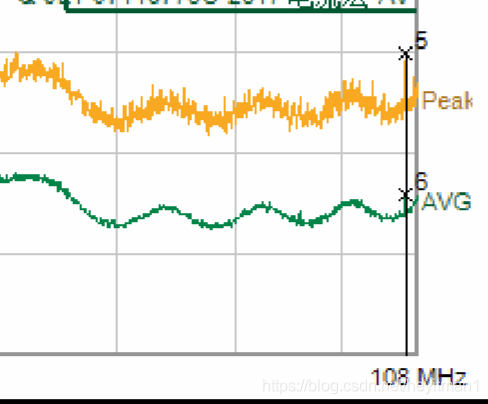

楼主和师傅加了Π型滤波,L型滤波都没有左右,后来在导线上加了一个大磁环将48M附近的鼓包压了下去(48M的鼓包后来发现是由背景噪声引起来的),各种共模和差模并没有任何的明显作用。后续将MCU引脚上强行焊上100nF和10uF的电容后,尖峰下降。随即重新进行layout删去一些不必要的器件,终于为退耦电容腾出了一些位置,最终正式实验的时候余量竟然有20db(优秀)!

自此实验之后,正式了MCU退耦电容的作用,既可以给MCU提供更好的工作环境,又可以将MCU产生的噪声滤去。所以MCU退耦电容一定要离引脚足够近啊!

-

MAX2112寄存器配置问题2016-03-09 0

-

浅谈FPGA配置状态字寄存器Status Register的调试2020-12-01 8196

-

大神们是怎样处理一个芯片的多个寄存器配置的?2017-11-10 0

-

AD7710读数据寄存器的结果始终为0,有解决方法吗?2019-06-06 0

-

状态字配置对PIC的重要性2021-11-24 0

-

P33指令指针寄存器简析2021-12-10 0

-

FPGA 调试 – 外设寄存器视图2012-05-15 3007

-

51单片机寄存器寻址的方法2018-11-22 3455

-

单片机实现寄存器寻址的方法解析2019-09-17 2966

-

STM32 I/O口配置和寄存器2021-11-15 770

-

IO口配置常用的8个寄存器 1.62021-11-29 1542

-

GPIO寄存器2021-12-08 699

-

ARM通用寄存器及状态寄存器详解2023-01-06 4760

-

如何理解FPGA的配置状态字寄存器2023-02-16 1510

-

如何根据自己设计中的寄存器配置总线定义来生成一套寄存器配置模版2024-03-04 362

全部0条评论

快来发表一下你的评论吧 !