LVDS器件工作原理浅析

电子说

描述

LVDS是一种小振幅差分信号技术,使用这种技术传输速率可以达到数百兆,甚至更高; LVDS具有更低的功耗、更好的噪声性能和更可靠的稳定性。简要地介绍了LVDS的原理及优势,分析了LVDS接口设计要注意的问题,着重研究了LVDS与LVPECL、CML间的接口设计;同时给出了不同耦合方式下的电路设计图

引 言

对于高速电路,尤其是高速数据总线,常用的器件一般有ECL、BTL和GTL等。这些器件的工艺成熟,应用也较为广泛,但都存在一个共同的弱点,即功耗大。

此外, 采用单端信号的BTL 和GTL器件,电磁辐射也较强。目前, NS公司率先推出的CMOS工艺的低电压差分信号器件, 即LVDS给了人们另一种选择。

LVDS技术简介

LVDS(Low Voltage Differential Signaling)是一种小振幅差分信号技术,使用非常低的幅度信号(约350 mV)通过一对差分PCB走线或平衡电缆传输数据。它允许单个信道传输速率达到每秒数百兆比特,其特有的低振幅及恒流源模式驱动只产生极低的噪声,消耗非常小的功率。

LVDS定义在2个国际标准中: IEEE P1596.3 (1996 年3 月通过) , 主要面向SC I ( ScalableCoherent Interface) ,定义了LVDS的电特性,还定义了SC I协议中包交换时的编码; ANSI /EIA -644 (1995年11月通过) ,主要定义了LVDS的电特性,并建议了655 Mb / s的最大速率和1. 823Gb / s的无失真媒质上的理论极限速率。在2个标准中都指定了与物理媒质无关的特性,这保证了LVDS能成为多用途的接口标准。

LVDS器件的工作原理

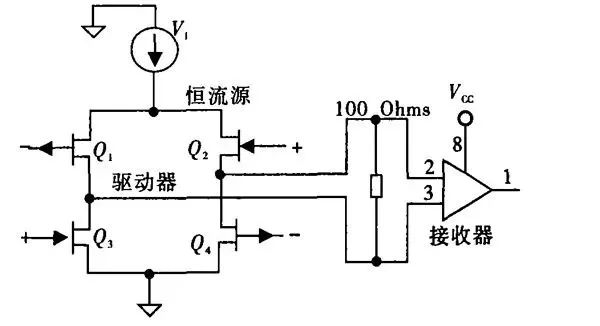

LVDS器件的工作原理如图1所示。

图1 LVDS的工作原理图

LVDS驱动器由一个驱动差分线对的电流源组成,通常为3. 5 mA.LVDS接收器具有很高的输入阻抗,因此驱动器输出的电流大部分都流过100Ω的匹配电阻,并在接收器的输入端产生大约350 mV的电压。当驱动器翻转时,它改变流经电阻的电流方向,产生有效的逻辑“1”和逻辑“0”状态。

驱动器只有一个恒流源,这个差分驱动器采用奇模(Odd - mode)的传输方式,即等量的方向相反的电流分别在传输线路上传送。电流会重新回流到双绞线内,加上电流环路面积较小,因此产生最少电磁干扰。

电源将供电加以限制,以免转变时产生突变电流。由于并无突变电流出现,因此数据传输速度高达1. 5 Gb / s,但又不会大幅增加功耗。此外,恒流驱动器的输出可以容许传输线路出现短路情况或接地,而且即使这样也不会产生散热上的问题。

差分接收器是一款高阻抗芯片,可以检测小至20 mV的差分信号,然后将这些信号放大,以至达到标准逻辑电位。由于差分信号具有1. 2 V的典型驱动器补偿电压,而接收器可以接受由接地至2. 4 V的输入电压,因此可以抑制高达±1 V来自传输线路的共模噪声。

由于逻辑状态之间只有300 mV 的电压差别,因此电压变化极快, 但转换速率不会加快。

又由于转变速度减慢,使得辐射场的强度也大幅减弱。同样,传输路线阻抗不连续性的反射也不会成为大问题,有助减低电波辐射量及信号的串扰。

总结

随着信息化的发展, LVDS的高性能、低功耗、低噪声的优点,使得LVDS将成为很多设计适合的方案。LVDS不仅能够以数百兆的速率传输数据而且驱动距离可达10 m,远胜于其他标准。

这些优点可能使LVDS成为高速数据传输的标准。

-

半导体存储元器件工作原理2017-02-05 0

-

MATLAB中simulink仿真图中几个元器件是什么工作原理2019-03-05 0

-

Kubernetes NetworkPolicy在Calico上的工作原理介绍2019-06-11 0

-

SERDES工作原理和器件特点是什么?2021-05-25 0

-

介绍一些光电器件的工作原理2021-06-08 0

-

基于深亚微米MOS器件沟道的热噪声浅析2009-12-15 469

-

LVDS信号的PCB设计2008-10-16 3380

-

感光器件工作原理2009-12-21 8258

-

二相CCD器件的工作原理2010-11-10 5108

-

浅析三极管三极管工作原理2017-04-17 1017

-

浅析压控振荡器的工作原理2023-07-14 1205

-

浅析智能家居照明系统工作原理及应用2023-11-02 297

-

浅析板框压滤机类型构造和工作原理2023-11-03 166

-

浅析干式变压器的工作原理、应用和选型2024-02-18 1013

-

IGBT器件的结构和工作原理2024-02-21 616

全部0条评论

快来发表一下你的评论吧 !