TSV与μbumps技术是量产关键

电子说

1.2w人已加入

描述

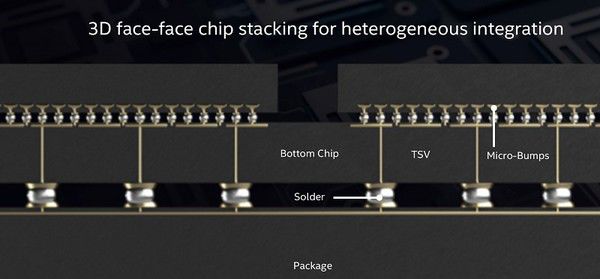

从英特尔所揭露的技术资料可看出,Foveros本身就是一种3D IC技术,透过硅穿孔(Through-Silicon Via, TSV)技术与微凸块(micro-bumps)搭配,把不同的逻辑芯片堆叠起来。

其架构概念就是在一块基础的运算微芯片(compute chiplet)上,以TSV加上微凸块的方式,堆叠其他的运算晶粒(die)和微芯片(chiplets),例如GPU和记忆体,甚至是RF元件等,最后再把整个结构打包封装。

而英特尔目前所使用的制程已达到10纳米,预计也可以顺利推进至7纳米,也此透过此3D封装技术,将可在单一芯片中达成绝佳的运算效能,并持续推进摩尔定律。

英特尔更特别把此技术称为「脸贴脸(Face-to-Face)」的封装,强调它芯片对芯片封装的特点。而要达成此技术,TSV与微凸块(μbumps)的先进制程技术就是关键,尤其是凸块接点的间距(pitch)仅有约36微米(micron),如何透过优异的打线流程来达成,就非常考验英特尔的生产技术了。

图六: Foveros的TSV与微凸块叠合示意(source: intel)

但是英特尔也指出,Foveros技术仍存在三个挑战,分别为散热、供电、以及良率。由于多芯片的堆叠,势必会大幅加大热源密度;而上下层逻辑芯片的供电性能也会受到挑战;而如何克服上述的问题,并在合理的成本内进行量产供货,则是最后的一道关卡。

依照英特尔先前发布的时程,「Lakefield」处理器应该会在今年稍晚推出,但由于英特尔没有在COMPUTEX更新此一产品的进度,是否能顺利推出仍有待观察。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

请问有TSV6390AIDT和/或TSV6290AIDT的SPICE型号吗?2019-08-06 0

-

硅通孔(TSV)电镀2021-01-09 0

-

电接枝技术助力高深宽比TSV2011-01-14 1752

-

3D封装TSV技术仍面临三个难题2011-10-14 2343

-

3D封装与硅通孔(TSV)工艺技术2011-12-07 2313

-

赶搭3D IC热潮 联电TSV制程明年量产2012-09-12 809

-

详解TSV(硅通孔技术)封装技术2016-10-12 14911

-

通用输入/输出轨到轨低功耗操作放大器TSV321/TSV358/TSV324/TSV321A/TSV358A/TSV324A2017-09-05 844

-

深度解读TSV 的工艺流程和关键技术2017-11-24 60006

-

什么是TSV封装?TSV封装有哪些应用领域?2018-08-14 89494

-

应用于后蚀刻TSV晶圆的表面等离子体清洗技术2022-04-12 980

-

TSV关键工艺设备及特点2023-02-17 1117

-

TSV的工艺流程和关键技术综述2023-02-17 7028

-

硅通孔TSV-Through-Silicon Via2023-07-03 2395

-

一文详解硅通孔技术(TSV)2024-01-09 5847

全部0条评论

快来发表一下你的评论吧 !