晶圆对晶圆的3D IC技术

电子说

描述

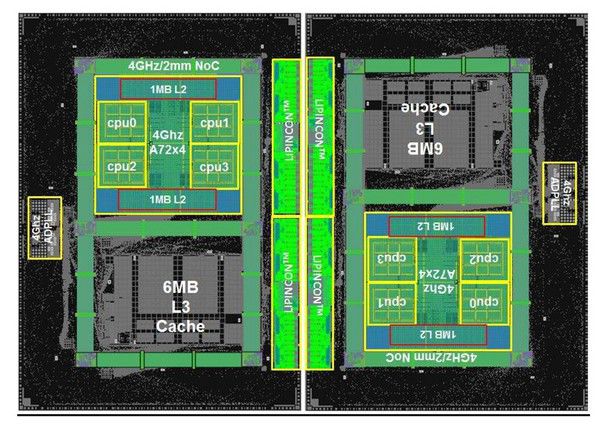

根据台积电在第二十四届年度技术研讨会中的说明,SoIC是一种创新的多芯片堆叠技术,是一种晶圆对晶圆(Wafer-on-wafer)的键合(Bonding)技术,这是一种3D IC制程技术,可以让台积电具备直接为客户生产3D IC的能力。

让外界大感惊艳的是,SoIC技术是采用硅穿孔(TSV)技术,可以达到无凸起的键合结构,可以把很多不同性质的临近芯片整合在一起,而且当中最关键、最神秘之处,就在于接合的材料,号称是价值高达十亿美元的机密材料,因此能直接透过微小的孔隙沟通多层的芯片,达成在相同的体积增加多倍以上的性能,简言之,可以持续维持摩尔定律的优势。

据了解,SoIC是基于台积电的CoWoS(Chip on wafer on Substrate)与多晶圆堆叠(WoW)封装技术开发的新一代创新封装技术,未来将应用于十纳米及以下的先进制程进行晶圆级的键合技术,被视为进一步强化台积电先进纳米制程竞争力的利器。2018年10月,台积电在第三季法说会上,已针对万众瞩目的SoIC技术给出明确量产时间,预期2020年开始挹注台积电的营收贡献,至2021年将会大量生产,挹注台积电更加显著的营收贡献。

六月,台积电赴日本参加VLSI技术及电路研讨会发表技术论文时,也针对SoIC技术揭露论文,论文中表示SoIC解决方案将不同尺寸、制程技术及材料的裸晶堆叠在一起。相较于传统使用微凸块的三维积体电路解决方案,台积电的SoIC的凸块密度与速度高出数倍,同时大幅减少功耗。此外,SoIC能够利用台积电的InFO或CoWoS的后端先进封装至技术来整合其他芯片,打造强大的3D×3D系统级解决方案。

外界咸认,从台积电最初提出的2.5版CoWoS技术,至独吃苹果的武器InFO(整合型扇型封装)技术,下一个称霸晶圆代工产业的,就是SoIC技术。

摊开台积电公布的2019年第一季财报,10纳米及以下纳米制程的营收贡献,已大大超越16纳米制程的营收贡献,凸显出未来十纳米及以下先进制程已势不可当。

也因此,2019年,电子设计自动化(EDA)大厂,如益华电脑(Cadence)、明导国际(Mentor)、ANSYS皆已相继推出支援台积电SoIC的解决方案,并已通过台积电认证,准备迎接SoIC辉煌时代的来临。

全部0条评论

快来发表一下你的评论吧 !