pci 引脚定义及信号中文说明

接口定义

描述

|

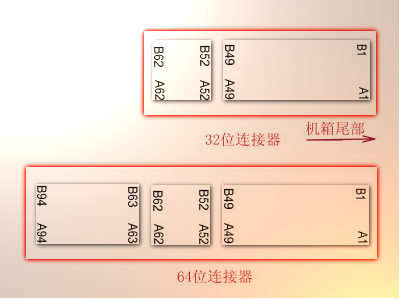

标准5V 32位/64位PCI插槽引脚信号一览表 |

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

表3-6 标准5V 32位/64位PCI插槽引脚信号一览表

|

PCI信号定义说明(中文版)

1. AD[31:0] (PCI ADDRESS / DATA BUS)

地址与数据总线讯号,在FRAME#启动后地址才有效,在

PCLK第一个CLOCK 动作初始化时,FRAME#动作后,输出

为地址与数据,写入周期,输入为数据,读取周期 TRDY# 与

IRDY#会动作,高阻抗时,为数据转换周期或RESET#动作

2. C/BE[3:0]# (PCI COMMAND /BYTE ENABLES)

FRAME#启动后,CLOCK第一个CLOCK,周期为PCI命令,

再下一个周期为允许命令,命令在FRAME#后有效,数据在

TRDY#与IRDY#后有效

3. DEVSEL# (PCI DEVSEL SELECT)

确定外部外围连结之响应讯号,高阻抗时,为停止周期或RE

SET#动作时

4. FRAME# (PCI CYCLE FRAME)

PCI 总线起始讯号

5. GNT[4:0]# (PCI BUS GRANT)

PCI 总线控制认可讯号

6. IRDY# (INITIATOR READY)

数据读取写入讯号

7. LOCK# (PCI BUS LOCK)

总线锁住讯号

8. PAR (PCI BUS PARITY)

地址与位传送之同位检错讯号

9. PCLK (PCI CLOCK)

PCI 时脉讯号

10.PGNT# (PCI GRANT TO PERIPHERAL BUS CONTROLLER)

PCI 总线对外部外围装置之需求同意认可讯号

11. PERQ# (PCI REQUEST FROM PERIPHERAL BUS CONTROLLER)

外围处理器对PCI总线要求讯号

12. REQ[4:0]# (PCI BUS REQUEST)

PCI 总线需求讯号

13. RESET# (RESET)

系统重置讯号

14. SERR# (SYSTEM ERROR)

系统错误侦测讯号 可产生NMI 不可屏蔽中断

15. STOP# (PCI BUS STOP)

PCI 总线放弃或重试数据传送之讯号

16. TRDY# (TARGET READY)

PCI 总线数据读取传送讯号

17.WSC# (WRITE SNOOP COMPLETE)

I /O APIC 芯片有上时之中断讯息传送讯号

- 相关推荐

- 引脚

-

labview视觉模块中文说明书!2012-05-30 0

-

Zigbee协议栈中文说明2012-08-03 0

-

Keil C51中文说明2012-08-17 0

-

cadence菜单使用中文说明2012-09-21 0

-

LABVIEW-IMAQ模块中文说明书2012-10-04 0

-

C51中文说明书2013-03-06 0

-

lspcad的分频设计中文说明书2013-08-30 0

-

LABVIEW-机器视觉模块中文说明书2015-05-28 0

-

求DAC7311中文说明与代码2015-10-29 0

-

转:STM32固件库函数中文说明2016-08-04 0

-

Jlink转接板中文说明文档最新2013版2016-08-17 0

-

七彩钟中文说明书2009-09-21 426

-

pci引脚定义 pci 接口定义2008-04-27 7207

-

三星_i8510中文说明书2015-12-31 792

-

LCDHome论坛_150种IC引脚中文说明资料2017-02-14 1083

全部0条评论

快来发表一下你的评论吧 !