基于Cadence的信号和电源完整性设计与分析

描述

在Cadence信号和电源完整性三天活动的第二天,只有100多名与会者听取了会议,Robert Hanson解释了与DDR3和PCI Express 3.0相关的高速接口设计挑战。罗伯特在设计时序合规性以及如何满足多吉比特接口上的误码率规范时,揭开了神秘面纱。

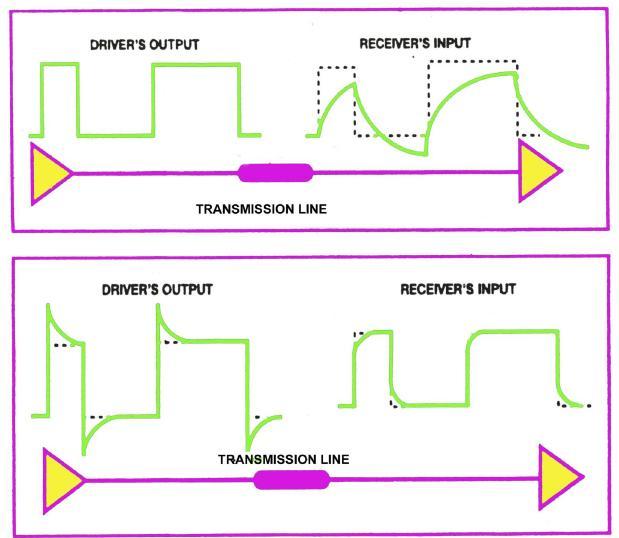

罗伯特关于多千兆位接口的材料包括关于趋肤效应,介电损耗和需要预先强调。

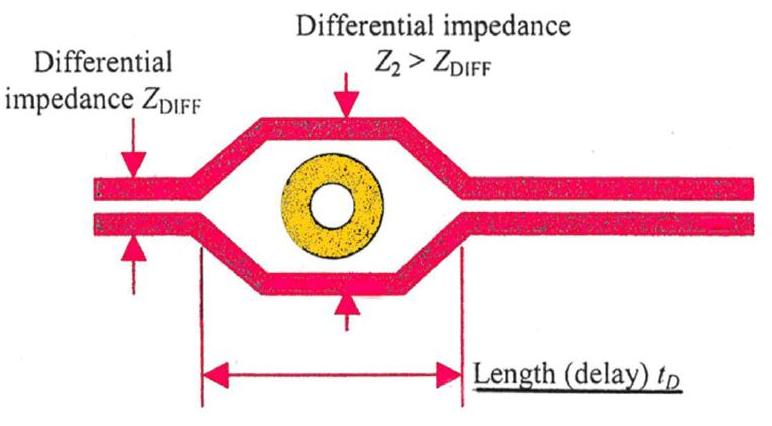

此外,由于多千兆位串行链路总是以差分对形式实现,因此罗伯特讨论了一些风险。管理差分阻抗很差。

许多与会者都能参加下午的研讨会,这些研讨会让人们可以亲身体验分析DDR3的Cadence工具。 PCB上的PCI Express互连。

此次高级信号完整性日为与会者提供了学习理论,熟悉工具,然后再使用工具的独特机会将这种经验带回他们的工作场所并立即应用于过程中的设计。第三天返回的与会者将有机会了解电力传输网络(PDN)的设计和分析,并再次有机会获得执行PDN分析的Cadence工具的实际操作经验。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

信号完整性分析与设计2009-09-12 0

-

信号与电源完整性分析和设计培训2010-05-29 0

-

2011信号及电源完整性分析与设计2010-12-16 0

-

高速信号的电源完整性分析2012-08-02 0

-

信号完整性与电源完整性的仿真分析与设计2015-01-07 0

-

电源完整性分析与设计2015-01-15 0

-

【下载】《Cadence高速电路板设计与仿真:信号与电源完整性分析》——学习allegro/orcad的桌面参考书2017-07-18 0

-

【下载】《信号完整性分析》2017-09-19 0

-

信号完整性与电源完整性的仿真分析与设计,不看肯定后悔2021-05-12 0

-

电源完整性分析2021-10-29 0

-

信号完整性与电源完整性的相关资料分享2021-11-15 0

-

信号完整性为什么写电源完整性?2021-11-15 0

-

详解信号完整性与电源完整性2021-11-15 0

-

什么是电源和信号完整性?2021-12-30 0

-

信号完整性与电源完整性的仿真2021-09-29 1145

全部0条评论

快来发表一下你的评论吧 !