FPGA+CPU的单片集成相较于传统应用的优势明显

可编程逻辑

描述

(文章来源:EEPW)

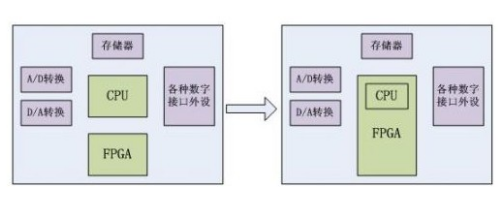

基于FPGA的CPU集成将带来的一些潜在优势包括:更易于满足大多数系统的功能性需求;潜在的改善了系统的性能;在某些应用中的灵活性和可升级性大大提高;处理器到外设的接口能够得到优化;软硬件互联的接口性能获得极大的提升;有利于设计的重用和新设计的快速成型;简化单芯片甚至整板的PCB布局布线。

FPGA+CPU的单片集成相较于传统应用的优势由此可见一斑,但从另一个角度看,正如CPU从单核到多核演进在延续着摩尔定律的“魔咒”,FPGA+CPU的强势出击更像是并行处理在嵌入式应用中的大行其道。

延续一贯的作风,Xilinx和Altera在其嵌入CPU的FPGA器件上都不约而同地选择了性能出色的ARM Cortex-A9内核,可见他们目前瞄准的市场趋向于中高端应用客户。而在低端应用方面,即便是网络爆炸的时代,默默无闻的Capital-Micro公司依然不为广大工程师们所熟知,但他们开发的可重构系统芯片CsoC(Configurable SoC)却悄然无声地在中低端市场应用中杀出了一片血路。值得一提的是,这是一家地地道道的中国本土FPGA厂商。

从1971年Intel的第一片4位处理器问世至今恰好已有40个年头,虽然嵌入式行业经历了翻天覆地的巨变,但即便你认为它是“土得掉牙”却简单实用的8位MCS-51单片机却依然独树一帜,尤其是在国内的整个工控行业中还是有着很强的生命力。

从05年成立至今,Capital-Micro先后推出了Astro和AstroII两代CSoC。其内嵌的8051在两代器件上分别可以稳定地运行到100MHz和150MHz。虽然由于FPGA制造工艺还处于0.13um,大大制约了逻辑性能,但目前的这两代产品至少可以满足包括步进电机控制、LCD驱动控制、接口扩展、LED控制卡、微型打印机在内的工业应用需求。

从器件的内部架构上来看,如图2所示,AstroII中不仅有同类产品中堪称性能“卓越”的8051硬核,也集成了一些常见的外设如定时器、看门狗、UART、IIC和SPI等。当然,8051的程序启动也完全采取了类似很多ARM的直接映射(Fully Shadowed)方式,确保读写缓慢的ROM不再成为制约CPU性能的瓶颈。而8051与FPGA的互联方面,不仅可以使用8051的EMIF寻址(23位宽可寻址地址总线),4K×8bit的DPRAM也是高速数据传输的不错选择,并且在这些互联接口上都已经固化好了同步逻辑,无需设计者浪费精力。此外,从最廉价的晶体时钟支持,到I/O数量的最大化,再到其平易近人的价格,无不向我们展示着这款国产芯片的“经济适用”。

-

FPGA/CPLD与单片机相比有哪些优势?2012-02-27 0

-

FPGA较传统CPU强在哪里?2017-03-11 0

-

伺服电机相较于其他电机有什么优点?2018-11-16 0

-

软件定义的PXI RF仪器和传统仪器相比有什么优势?2019-08-15 0

-

你知道Actel的nano FPGA技术具备哪些优势吗?2021-04-08 0

-

与传统模式的芯片设计进行对比FPGA芯片有哪些优势2021-09-14 0

-

相较于x86架构,华为鲲鹏处理器的优势有哪些2021-10-25 0

-

嵌入式相较于传统开发有什么优点2021-10-27 0

-

zynq这种FPGA器件相对以往传统FPGA有哪些优势和劣势2022-11-07 0

-

FPGA+CPU将会是未来基于大数据的人工智能的主要架构2016-07-28 3372

-

万能的FPGA真的能取代CPU和GPU吗2019-09-06 2147

-

FPGA相对于CPU和GPU而言有着比较明显的优势2019-12-20 2439

-

在数据中心部署FPGA+CPU图像处理的解决方案2020-05-04 723

-

医疗放射在线监管系统相较于传统监管的优势2023-09-18 231

-

FPGA协处理的优势有哪些?如何去使用FPGA协处理?2023-10-21 1550

全部0条评论

快来发表一下你的评论吧 !