资料下载

使用FPGA设计数字幅频均衡功率放大器的论文免费下载

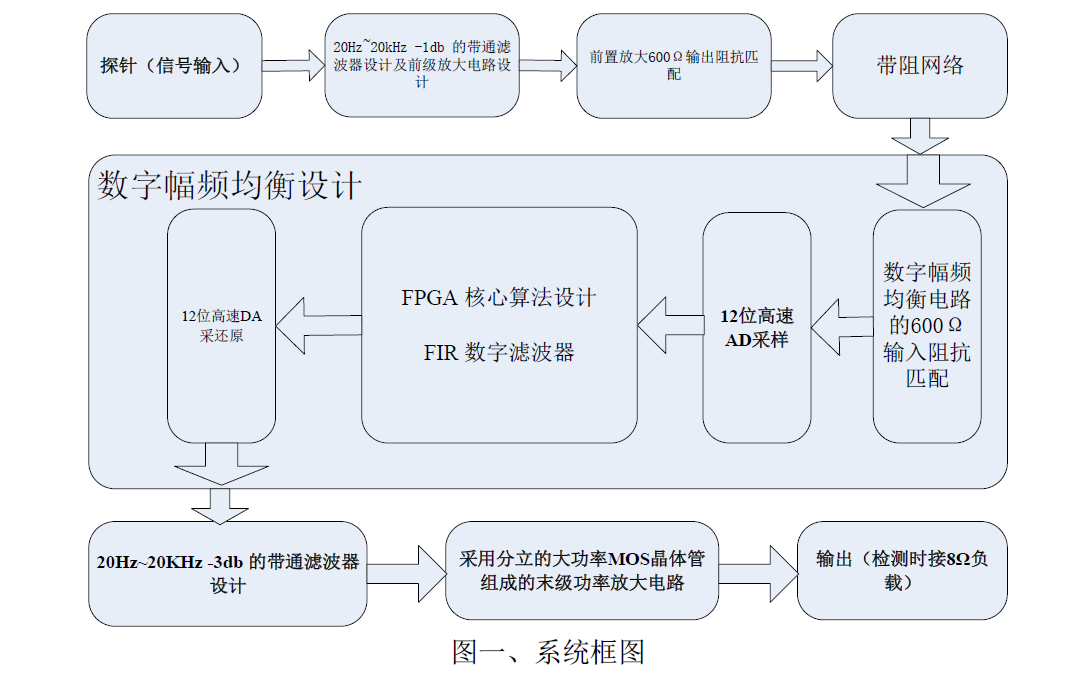

本系统采用FPGA作为数据处理和控制核心,将设计任务划分为前置放大电路设计、功率放大电路设计、数字幅频均衡电路设计、数字处理算法设计。并认真设计硬软件,同时精心设计了FIR处理,以实现对幅频特性的均衡;采取OCL电路实现了低频功率放大设计;为了实现对通频带的精确定位,选用Butterworth滤波器,精确确定系统的频带。本系统较好的完成了基本部分和发挥部分的要求。

仔细分析题目要求,以实现对设定的带阻网络带来的幅频特性变化进行数字幅频均衡,是本题的最大难点,也是设计的重点之一。同时供分立元件组成的功率放大器对8Ω负载提供的10W的功率输出也是设计的重点。对此,我们考虑了以下几种方案:

(1)核心芯片和算法的确定:

方案一:纯单片机方式。由单片机来完成信号调理、采集和信号处理等底层的核心计算。

方案二:纯 FPGA 方式。即完全来完成采集和信号处理等底层的核心计算。

方案二的最大优点是 FPGA 来完成采集和信号处理等底层的核心计算,使得编程简化,仿真效果明显,更容易实现题设要求。并同时精心设计了FIR 处理,以实现对幅频特性的均衡。

(2)低频功率放大设计:

方案一:采取 OCL 电路。

方案一:采取 OC 电路。

低频功率放大器要求使用大功率 MOS 晶体管作为末级放大,而且要求提供10W的功率,这就要求在8Ohm 的电阻下能提供9V 左右的电压,峰峰值应在12 伏以上。这就要求有2~3 级的放大电路才能组成这个放大电路。又因为通频带控制在一个确定的值,故采用有源带通滤波器以实现要求。为满足偶和要求,CL 要远大于1/WR 的值,又1/wr=397.89uf,这样C 的值会非常大,不好选择,故最终采取OCL 电路。综合考虑,我们选择了方案一,并精心设计了实现电路,最终很好的完成了题目的要求。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章