ModelSim仿真器的主要特点以及用法解析

EDA/IC设计

描述

ModelSim是工业界最优秀的语言仿真器,它提供最友好的调试环境,是作FPGA、ASIC设计的RTL级和门级电路仿真的首选。它支持PC和UNIX、LINUX平台,是单一内核支持VHDL和Verilog混合仿真的仿真器。它采用直接优化的编译技术、Tcl/Tk技术、和单一内核仿真,编译仿真速度业界最快,编译的代码与平台无关,便于保护IP核,具有个性化的图形界面和用户接口,为用户加快调试提供强有力的手段。全面支持VHDL和Verilog语言的IEEE 标准,以及IEEE VITAL 1076.4-95 标准,支持C语言功能调用, C的模型,基于SWIFT的SmartModel逻辑模型和硬件模型。

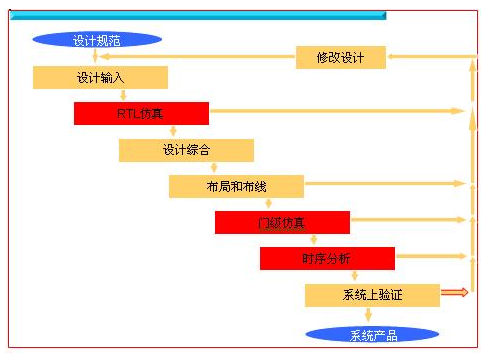

ModelSim支持RTL仿真,门级仿真,时序仿真:

主要特点:

*采用直接编译结构,编译仿真速度最快;

*单一内核无缝地进行VHDL和Verilog混合仿真;

*与机器和版本无关,便于数据移植和库维护;

*与机器无关的编译代码编于保护和利用IP;

*简单易用和丰富的图形用户界面,快速全面调试;

*Tcl/Tk用户可定制仿真器;

*完全支持VHDL/Verilog国际标准,完全支持Verilog 2001;

*支持众多的ASIC和FPGA厂家库;

*集成的Performance Analyzer帮助分析性能瓶颈,加速仿真;

*灵活的执行模式,Debug模式可以进行高效的调试,效率模式大幅度提高仿真速度。

*加强的代码覆盖率功能Code Coverage,能报告出Statement 、Branch、Condition、

* Expression、Toggle、Fsm等多种覆盖率情况,进一步提高了测试的完整性;

*同一波形窗口可以显示多组波形,并且能进行多种模式的波形比较(Wave Compare);

*先进的Signal Spy功能,可以方便地访问VHDL 或者 VHDL 和Verilog 混合设计中的下层模块的信号,便于设计调试;

*支持加密IP;

*集成的 C调试器,支持 用C 语言完成测试平台和模块;支持64位的OS;

ModelSim用户界面:

ModelSim设计流程:

ModelSim Coverage验证:

ModelSim Dataflow窗口:

QuestaSim是第一个基于标准的单核验证引擎,集成了一个HDL模拟器,一个约束求解器,一个判断引擎,功能覆盖,以及一个通用的用户界面。

主要特点:

*内建单内核仿真器支持SystemVerilog、Verilog、VHDL、PSL以及SystemC。

*内建约束解释器支持Constrained-Random激励生成,以实现Testbench-Automation;

*支持基于PSL,SystemVerilog语言断言的功能验证,支持业界最著名的0-In Checkware 断言库功能验证

*集成化支持功能覆盖率检查与分析

*高性能的RTL和Gate-Level仿真速度

*支持用SystemVerilog和SystemC实现高层次Testbench设计与调试

*高性能集成化的混合语言调试环境加速对混合验证语言;(SystemVerilog,SystemC,PSL,VHDL,Verilog)的交叉调试与分析

*基于标准的解决方案能支持所有的流程,便于保护验证上的投资

*提供最高性价比的功能验证解决方案

Questa AFV提供真正的混合语言验证

Questa AFV是以混合语言流程 (Mixed Language Flow) 为目标的单核心验证解决方案,

它同时支持SystemVerilog、VHDL、PSL和SystemC,使设计人员能够选择最合适的语言。

除此之外,与SystemVerilog验证能力的紧密连结,并将其用于受限随机

(Constrainedrandom)测试平台的产生以及功能覆盖率的验证也对VHDL使用者大有好处。

QuestaSim用户界面与ModelSim类似,命令也完全兼容。

QuestaSim Coverage检查:

QuestaSim DPI Use Flow:

责任编辑;zl

-

Linux的主要特点 发展 安装2012-08-13 0

-

如何仿真IP核(建立modelsim仿真库完整解析)2012-08-15 0

-

无铅焊接和焊点的主要特点2013-10-10 0

-

贴片头的分类和主要特点2018-09-03 0

-

基于Modelsim FLI接口的仿真系统2019-06-06 0

-

NI Multisim 10的主要特点2021-07-14 0

-

什么是Lora?LoRa的主要特点?2021-07-26 0

-

STM32CubeIDE的主要特点有哪些2021-09-28 0

-

RISC的主要特点和优点讲解2023-02-27 0

-

使用vivado的仿真器仿真时,modelsim的transcript界面无法输出C程序的printf语句是为什么?2023-08-11 0

-

将vivado的仿真器改成modelsim,仿真时modelsim的transcript没法打印出e203实时运行的信息怎么解决?2023-08-11 0

-

modelsim仿真详细过程(功能仿真与时序仿真)2017-12-19 64289

-

仿真软件ModelSim及其应用,ModelSim的仿真流程2018-12-29 9247

-

Modelsim仿真教程Modelsim的基础入门基础教程免费下载2019-04-30 1047

全部0条评论

快来发表一下你的评论吧 !