资料下载

设计应用于射频SOC芯片的低噪声高PSRR的LDO详细资料说明

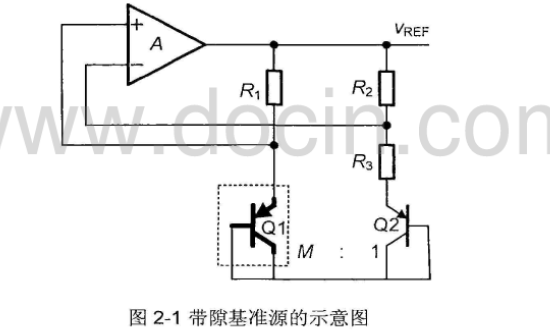

随着SOC无线通讯芯片的发展,全集成的低压差线性稳压器成为了近年来国际上的一个研究热点。这种应用的线性稳压器需要为整个射频收发机系统提供一个低噪声的电源;同时相较于传统的低压差线性稳压器有比较少的片外元器件,从而能够实现射频收发机芯片的全集成。本文正是基于这样的应用考虑而做的设计。 本文首先介绍了带隙基准源和低压差线性稳压器的基本理论知识,然后介绍了它们的主要性能指标,并介绍了一些传统的设计方法。 然后,文章着眼于射频无线接收机系统,针对射频无线收发机系统中对LDO要求比较高的两个电路模块PLL和DCXO做了具体的分析,提出了LDO的系统要求,根据系统要对LDO的噪声性能,电源抑制比,AC稳定性,瞬态响应以及负载线性度等性能分别做了优化。同时针对目前射频无线接收机集成度越来越高的趋势,分析了全片内LDO设计的主要思想和设计方法,然后考虑了系统集成的时候各个电路模块之间相互串扰的问题,优化了LDO的负载线性度。 接着,文章提出了一款应用于数字电视调谐接收机中,具有全片内,低噪声,高电源抑制比,快速瞬态响应等特点的线性稳压器。文中根据系统要求针对带隙基准源的噪声做了优化,提出了通过提高PNP的比值,以及噪声抵消等方法实现了比较好的噪声性能;并提出了数字控制型的带隙基准源,该电路通过控制PNP晶体管个数来得到精确可调的基准电压。接着提出了全片内线性稳压器的设计,具体分析了线性稳压器在无片外补偿电容的情况下,随着负载电流变化以及负载电容变化等情况下的AC稳定性和瞬态响应的性能。然后针对系统集成的要求,分析了线性稳压器的瞬态响应时间,同时针对接收机系统相互之间的串扰问题优化了线性稳压器的带宽。 最后,给出了版图设计的考虑以及PCB板的设计,并给出了电路的流片测试结果,验证了设计理论和设计方法的正确性,达到了系统要求。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章