基于FPGA的在临空环境下实现数据采集系统的设计

可编程逻辑

描述

0 引言

目前已经有多种成熟的数据采集系统,主要用于工业生产、环境监测、航空航天和科学研究领域中。大部分实时数据采集系统选用DSP(Digital Signal Processing)控制器和微控制器作为控制核心,比较容易实现复杂的算法[1],但是它们受到信息吞吐量和带宽的限制,不能实现并行化处理,在高速大批量数据采集时有些乏力。而有极强并行处理数据能力的现场可编程门阵列器件(Field Programmable Gate Array,FPGA)备受青睐,以FPGA为控制核心的数据采集系统也日渐兴盛。FPGA具有灵活性高、可扩展性强和资源丰富的特点[2-3],而且能够应对各种形式的接口协议,使其在数据采集系统中得到广泛应用。有些FPGA是反熔丝的,可靠性能和稳定性能非常高,这类FPGA在特定宇航应用中是必选项。

地球临近空间低温、低压、高辐射,环境极端恶劣,数据采集系统的传感器和控制部件很容易受到影响而工作异常,甚至出现系统崩溃的现象。此环境下设计数据采集系统需要考虑稳定性。FPGA能够实现复杂电路,能减小电路板上因布线产生的电磁干扰。与DSP控制器和其他CPU微控制器相比,FPGA生成硬件电路的特性更具有抗干扰性。前人进行可靠性处理的方法有冗余结构设计和配置存储器的回读校验与重配置[4]。同时数据采集系统可靠性也有合理的评估指标,例如运行环境、系统集成、人机耦合、方案成熟性及安全性[5]。

需设计一个数据采集系统,使其运行在临空的特定环境下,不仅实现数据采集任务,还需要实时将数据传回地面,并能完成部分控制功能。从运行成本和环境考虑,需提高系统的可靠性和稳定性。从硬件和软件两方面入手进行设计,在硬件方面,FPGA抗干扰性能强,所以选取FPGA作为本系统的主控制器。采用冗余策略,设计两路连接主控制器的传感器电路,使得数据采集系统可靠性提高。对软件部分,进行模块化编程,利用有限状态机和看门狗策略来提高系统稳健性。

1 系统硬件设计

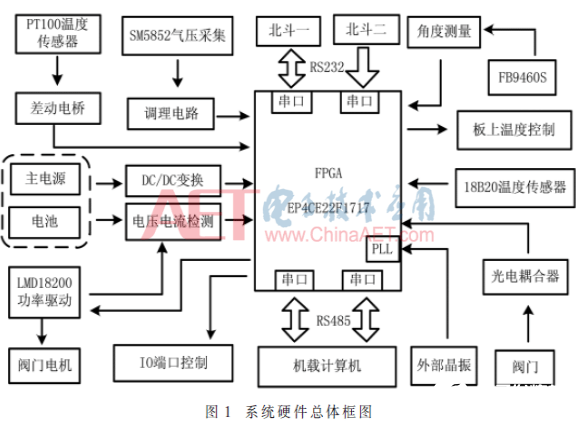

临空数据采集系统主要包括了以FPGA为控制器的最小系统模块、传感器模块、UART串口通信模块和控制模块。如图1所示,最小系统是维持FPGA控制器正常运行的外围电路;传感器模块涉及温度、角度、电流电压等信号的采集与调理,因为硬件的冗余,信号被分为主板信号和从板信号;UART串口通信模块包括2个RS232串口(与北斗模块相连)、2个RS422串口(与临空机载计算机连接);控制模块主要包括阀门控制模块和温度控制模块,温度控制模块用于控制加热电阻,来维持电路板上的元器件正常运行。

1.1 最小系统模块

本设计选用Altera公司的Cyclone IV E系列的EP4CE22F1717作为采集系统的控制器。它有22 320个逻辑单元、154个用户输出输出口、132个乘法器、4个PLL(“Phase Locked Loop”锁相环)。芯片的外部提供晶振频率为50 MHz。

1.2 温度采集模块

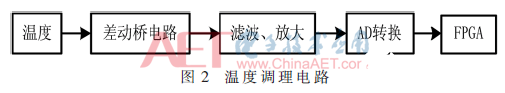

数据系统采用PT100温度传感器来测量10路温度。PT100温度传感器将温度变量转换成可以传送的标准化电信号。此传感器精度高,稳定性好,测温范围在-200 ℃~650 ℃之间,符合临空测温范围要求。如图2所示,将PT100传感器连接到差动电路中,测量差分电压,将此电压信号进行整形调理,经过模数转换芯片得到数字值暂存到FPGA中的内存中。滤波电路采用阻容滤波。仪表放大器采用TI公司的仪表放大器INA333,该放大器具有低功耗、高精度的特性。AD转换芯片应用5 V供电电压的TLC2543IN,允许11路外部模拟信号并行输入,串口输出转换数据,具有12位的分辨率。

1.3 气压采集模块

本设计选用SMI公司的SM5852系列气压传感器来采集气压信号。SM5852传感器的工作温度为-40 ℃~125 ℃,能够满足临空的恶劣环境,芯片内部有温度补偿算法,实现气压的精准测量。本文选用SM5852-003传感器,其可测压力范围是0~0.3 PSI(Pounds per Square Inch)。气压传感器既可以输出数字信号,又可以输出模拟信号。为了使系统设计简单而且信号获取精确高,这里直接采集传感器的数字信号。数字信号是通过IIC协议传输的,并利用74LVC4245电平转换芯片将电压的控制器与传感器连接在一起,将5 V的数字信号转换为3.3 V数字信号,同时对控制模块起到保护作用。

1.4 通信模块

这一模块在本系统中非常关键,它是连接采集器与地面监控系统的纽带。它负责将临空采集平台上获取的信息实时地传送给机载计算机或者北斗模块,同时实时接收来自两个模块的指令。采集平台上的重要数据信息通过事先拟定的协议被组合成不同长度的帧发送给地面指挥站。为了保证数据的安全性和准确性,增加数据帧校验环节,将求异或和作为帧校验的方法。

本系统的FPGA控制板放置在数据采集系统的平台上,与地面指挥站通信交互信息主要有两类:一类是下发采集器收集到的数据信息,另一类接收地面指挥系统的指令信息。为了保证数据安全和采集系统的可靠性,对通信模块冗余设计。通过两个RS422接口与机载计算机相连,机载计算机再通过无线通信与地面指挥站交互信息。另外,还通过两个RS232接口与机载北斗相连,通过北斗卫星服务与地面指挥站联系。同时,采集器的定位信息一同下发到地面。RS422接口芯片选用ADI公司ADM2587E,RS232接口芯片采用ADI公司的ADM3251E。两个RS422接口分为主板串口、从板串口,主板串口处理的是与主板相关的数据信息,从板串口处理与从板相关的数据信息。

2 系统软件设计

软件代码开发基于Altera公司的Quartus II 13.0平台,利用Verilog HDL语言实现代码块的设计与仿真。临空数据采集系统中,FPGA控制器内信号的性质和来源各式各样,有直接来自传感器的数字信号,有模拟信号转换后的数字信号,有程序内部的标志信号,有来自机载计算机的控制信号,有来自北斗模块发来的控制信号和定位信号,有FPGA控制器发出的数据信号、电机控制信号、电路板控温信号等。为了提高有效数据稳定地接收、存储和发送,需要对全体信号细致分类,这对程序代码模块划分有指导作用。系统软件设计要求代码可读性高、可靠性高、易维护、有可扩展的余地。系统设计的思路是先做总体架构,再逐个完成子模块的编写,最后在顶层模块完成信号连接。模块化的设计思路使得系统仿真测试更容易,代码维护性更强。

2.1 程序顶层架构

程序顶层模块的设计影响全局,关系到系统的稳定性和可靠性。系统结构的设计是根据模块的功能划分,每一个模块实现一个具体的功能,数据信息的交互通过各模块的输入输出接口连接。

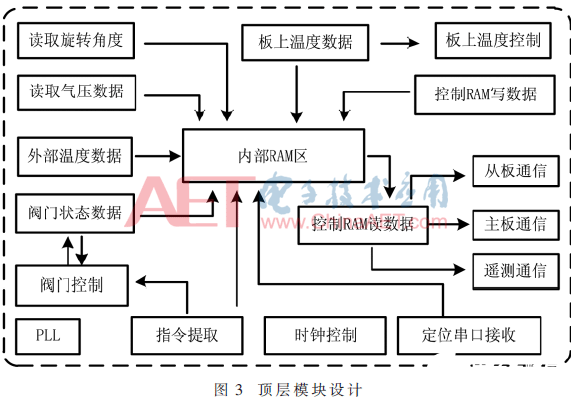

数据采集系统信号比较多,而且FPGA与机载计算机、北斗模块的通信按照既定协议交互数据,即定时发送采集系统的数据,不定时接收外部指令和状态信息,为了便于管理数据,在FPGA内开辟一块随机存储器(Random Access Memory,RAM),专门针对各种信号存储和读取,这种数据结构使FPGA内部数据共享更容易,也不易产生读写数据紊乱现象[6-7]。引用Altera公司提供的IP核配置RAM,经过事先估计并留有足够的余地,将RAM大小设置为512 B,读写地址线各9根,并设置读写使能控制端口。图3为系统的顶层模块架构,核心模块是RAM区的读写模块,温度、压力、电压、电流信号,以及来自机载计算机或北斗的指令、位置和状态等信号流入RAM区,而存储的数据需要从RAM区被读取,通过UART串口模块发送给机载计算机和北斗模块。

2.2 通信模块程序设计

通信模块借助UART串口实现双向通信。FPGA控制器向机载计算机和北斗模块发送数据帧,同时实时接收它们的指令与状态数据。控制器向两个RS422串口发送定位、主从板信息、状态等数据帧,定位数据帧包含来自北斗模块的定位信息,主从板数据帧囊括采集系统采集到的各类信息,状态数据帧含有北斗模块的状态信息。此外,控制器向两个RS232串口发送遥测数据帧和自检数据帧,遥测数据帧由遥测帧头、定位信息、主板或从板信息和遥测数据帧尾组成,自检数据帧包括自检信息的请求。同时,有3个UART串口实时接收来自机载计算机和北斗模块的指令和状态信息。程序运行时需要对各种数据帧频繁读写操作,如果程序设计不合理,很容易造成程序死锁或崩溃。鉴于串口数据的接收和发送没有紧密地耦合,程序内部将数据接收和发送分成两个子模块来设计,然后在顶层模块通过wire型变量连接。为了有效解决数据读写不紊乱的问题,设计状态机来合理使用RAM区资源,增强程序的稳定性。状态机的空闲任务会出现连接两个always块的使能信号,设计watchdog程序增强程序的鲁棒性。

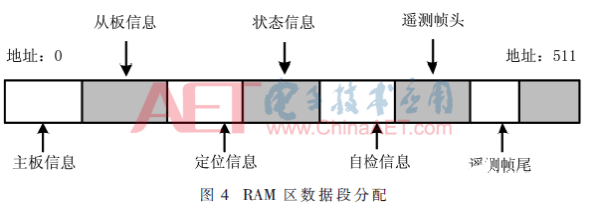

2.2.1 RAM数据段划分

本文设计了双端口RAM数据结构,承载采集控制系统的重要数据。依据通信协议,针对512 B的RAM区,细致地进行了数据段的划分,如图4所示。按照发送频次以及组帧要求,合理分配数据帧的存储顺序。这样设计会使控制器读写更可靠安全,也使代码编写调试更简捷。

2.2.2 数据发送状态机设计

信息传送模块是连接地面指挥系统和数据采集系统的纽带。在临空恶劣环境下,为了将采集到的数据和系统状况相关信息实时准确地传送到地面指挥站,在软件上进行了可靠性研究和处理。

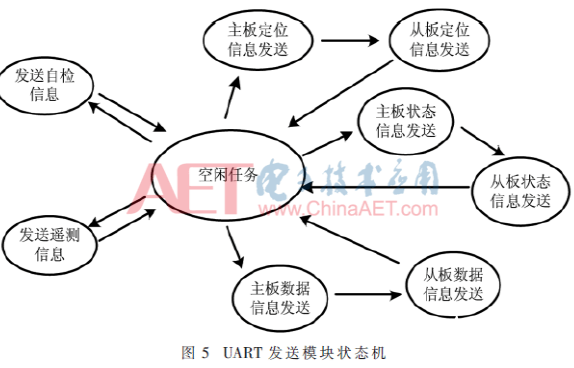

首先对传送的数据做了校验处理,可通过上位机软件测试传输数据帧是否正确,如果校验失败,可丢弃此帧。本系统的发送模块既要发送主板信息又要发送从板信息,既要传送给机载计算机又要传送给北斗卫星,发送帧的类型也有差异,因此,设计三段式状态机稳定地传送数据,以免数据发送紊乱。在状态机的空闲任务中,FPGA等待各种数据类型帧的触发信号,一旦接收到启动发送信号,进入到相应的发送状态中,将对应的数据帧发送到UART串口上,串口的触发信号也因数据信息的差异而不同。在空闲任务中,接收到触发信号后,需要实时对RAM区执行写操作,写操作完成后再进入发送状态,不免会引起程序死锁。为了解决这个问题,提高程序的鲁棒性,在等待写操作的部分加入看门狗程序,一旦死锁,可以强行将程序拉回到原始等待状态。图5为UART串口发送模块的状态机示意图。

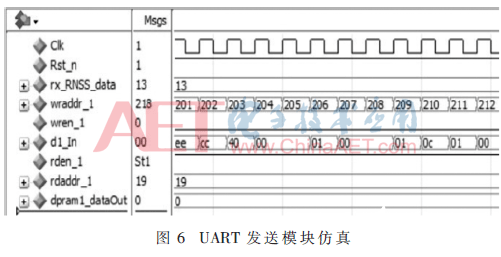

3 系统仿真与调试

数据系统的测试主要通过两种手段:软件仿真和借助上位机联调。本系统用到的仿真工具有Quartus II开发环境提供的在线逻辑分析仪、信号探针、逻辑分析仪接口等,还有外部安装性能强大的Modelsim仿真工具。例如,在调试具有读写应答的IIC通信的传感器和基于SPI通信的传感器时,使用在线逻辑分析仪直接观察数据波形特征,能够快速诊断并排查错误。利用Modelsim仿真工具时,需要先编写对应模块的testbench代码,并添加到仿真工具中,运行仿真软件。图6为调试UART通信模块波形图,可观察RAM的读写地址值与数据值的对应关系,验证代码的逻辑。尤其在调试状态机的运行情况时,能够很直观地查看状态时序逻辑的正确性。

当集中测试所有的模块时,为了提高调试效率,利用了基于UART通信的上位机软件。该软件运行在Windows 10 系统上,它通过USB接口接收FPGA发送的数据信息,并把信息可视化在面板上,直观明了地看到FPGA采集到的数据。

4 结论

临空环境有低温、低压、高辐射的特点,因此对运行在环境下数据采集系统的设计要求极为严格。本文从软硬件两方面着手进行可靠性研究,设计了应对这种复杂环境的数据采集系统,取得了良好的效果。该系统能够可靠稳定地采集到传感器数据,并能长时间稳定地与北斗模块和机载计算机通信,能够通过地面控制系统发送指令控制数据采集系统。

参考文献

[1] MONMASSON E,IDKHAJINE L,CIRSTEA M N,et al.FPGAs in industrial control applications[J].IEEE Transactions on Industrial Informatics,2011,7(2):224-243.

[2] KANDADAI V,SRIDHARAN M,PARVATHY S M,et al.A comprehensive embedded solution for data acquisition and communication using FPGA[J].Journal of Applied Research & Technology,2017,15(1):45-53.

[3] 周珊,杨雅雯,王金波。航天高可靠FPGA测试技术研究[J]。计算机技术与发展,2017,27(3):1-5.

[4] 宋克非.FPGA在航天遥感器中的应用[J]。光机电信息,2010,27(12):49-55.

[5] 陈柯勋,王晓毅,薛辉。基于FPGA的数据采集器设计及可靠性分析[J]。科技资讯,2017,15(24):7-8.

[6] 王敬美,杨春玲。基于FPGA和UART的数据采集器设计[J]。电子器件,2009,32(2):386-389.

[7] NING Y,GUO Z,SHEN S,et al.Design of data acquisition and storage system based on the FPGA[J].Procedia Engineering,2012,29:2927-2931.

-

基于FPGA的数据采集系统2012-08-11 0

-

求:基于FPGA的数据采集存储系统的sch原理图2012-10-29 0

-

基于FPGA的数据采集存储系统2012-10-29 0

-

基于FPGA与SRAM数据采集系统设计2018-05-09 0

-

基于FPGA+AD7609的数据采集系统实现2018-08-09 0

-

采用LabVIEW和声卡的数据采集系统实现2019-05-13 0

-

基于FPGA的高速数据采集系统该怎么设计?2019-09-05 0

-

FPGA实现数据采集的方式对比(传统串口、数据采集卡及外设计接口)2020-01-07 0

-

如何利用FPGA实现高速连续数据采集系统设计?2021-04-08 0

-

FPGA在膜式氧合器测试数据采集系统中的应用2011-03-15 324

-

基于FPGA的数据采集系统设计2012-05-08 725

-

基于FPGA的高速数据采集硬件系统设计2016-05-10 787

-

基于FPGA的高速数据采集系统接口设计2016-05-10 796

-

基于FPGA的数据采集板设计与实现2016-05-10 512

-

基于FPGA的高速数据采集系统设计_杨江涛2016-05-17 748

全部0条评论

快来发表一下你的评论吧 !