ISA总线原理

电子常识

描述

ISA总线的原理

ISA总线概况

ISA总线来源于IBM-PC微计算机。开始时PC机面向个人及办公室,定义了8位的ISA总线结构,对外公开,成为标准(ISO ISA标准)。第三方开发出许多ISA扩充板卡,推动了PC机的发展。1984年推出IBM-PC/AT系统,ISA从8位扩充到16位,地址线从20条扩充到24条。

ISA总线: (Industry Standard Architecture:工业标准体系结构)是IBM公司为PC/AT电脑而制定的总线标准,为16位体系结构,只能支持16位的I/O设备,数据传输率大约是8MB/S。也称为AT标准。

ISA总线插槽示意图

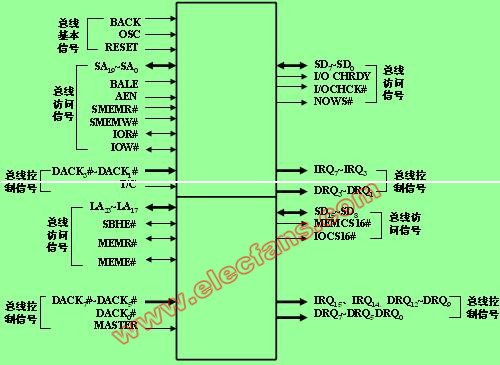

ISA总线引线示意图

ISA总线引线定义:主要信号说明

RESET、BCLK:复位及总线基本时钟,BLCK=8MHz。

SA19-SA0:存储器及I/O空间20位地址,带锁存。

LA23-LA17:存储器及I/O空间20位地址,不带锁存。

BALE:总线地址锁存,外部锁存器的选通。

AEN:地址允许,表明CPU让出总线,DMA开始。

SMEMR#、SMEMW#:8位ISA存储器读写控制。

ISA总线引线定义:主要信号说明

MEMR#、MEMW#:16位ISA存储器读写控制。

SD15-SD0:数据总线,访问8位ISA卡时高8位自动传送到SD7-SD0。

SBHE#:高字节允许,打开SD15-SD8数据通路。

MEMCS16#、IOCS16#:ISA卡发出此信号确认可以进行16位传送。

I/OCHRDY:ISA卡准备好,可控制插入等待周期。

NOWS#:不需等待状态,快速ISA发出不同插入等待。

I/OCHCK#:ISA卡奇偶校验错。

IRQ15、IRQ14、IRQ12-IRQ9、IRQ7-IRQ3:中断请求。

DRQ7-DRQ5 、DRQ3-DRQ0: ISA卡DMA请求。

DACK7#-DACK5#、DACK3#-DACK0#:DMA请求响应。

MASTER#:ISA主模块确立信号,ISA发出此信号,与主机内DMAC配合使ISA卡成为主模块,全部控制总线。

-

ISA总线的标准DMA技术在Linux中的实现2019-07-01 0

-

WinCE精简ISA总线和外部中断的相关接口函数2019-09-27 0

-

怎么设计一款基于ISA总线的通用多DSP目标系统?2021-04-13 0

-

ISA总线信号时序简介2009-05-21 1682

-

基于ISA总线的轴角数字转换卡设计2009-09-25 669

-

基于ISA总线的虚拟万用表设计2010-05-19 515

-

基于ISA总线的计算机与DSP的通信2010-12-20 539

-

ISA总线引脚定义2007-11-23 4808

-

ISA总线接口定义2008-05-31 5766

-

ISA总线和Futurebus+总线2009-05-21 2732

-

基于ISA总线的ADC板卡设计2009-12-14 1464

-

EM9000下的ISA总线软件开发环境配置2011-06-09 900

-

基于ISA总线的同步通信控制器2017-02-07 902

-

如何快速访问ISA总线端口2019-09-26 3382

-

英创信息技术精简ISA总线WinCE编程简介2020-02-11 1059

全部0条评论

快来发表一下你的评论吧 !