基于SDR技术实现SIMD处理器的设计与仿真研究

通信网络

描述

引言

第四代移动通信技术的标准已经被提出并在继续的完善和建立当中。相较于3G无线技术,4G采用MIMO-OFDM技术来提升数据速率,大大提高了数据处理能力;同时,标准对4G的数字信号处理量的要求比现有的3G方案高出数个数量级,而功耗仅允许增长2-5倍。因此,仅仅扩展3G DSP是不能满足4G处理器的能耗比要求,必需设计新的处理器体系结构。目前国内的两大通信设备生产商华为和中兴相继开发了面向WINMAX及LTE等4G基站解决方案,但是其核心处理单元仍然采用国外的一些DSP芯片。

经典的无线通信体系结构都是由面向特定应用的专用集成电路和数字信号处理器所构成的,无法提供任何的灵活性。软件无线电(SDR)的原理描述是将无线通信设备的物理层处理工作全部或大部分交给可编程体系结构来完成。可编程的SDR解决方案相较于传统的硬件解决方案具有非常明显的优点:(1)使得软件开发和硬件设计工作同时进行,开发时间和成本相较于传统的专用集成电路的来说大大降低。(2)在同一处理器体系结构上可以动态执行不同的无线通信协议,这种多模式的工作向服务商提供的一个但可以应对多种市场需求或向用户提供更多的功能。(3)系统的可编程性可以有效地降低维护成本。

虽然SDR系统增加了灵活性,降低了无线通信设备的开发成本。然而为了支持灵活性这一新特点,导致SDR系统功耗变得很高。未来4G无线协议瞄准的速率在100Mbps~1Gbps之间[4-5];因此,SDR解决方案在需要保证高吞吐量的同时,还要严格遵守无线通信设备的功耗约束。功耗效率对于SDR系统来说是异常重要的。

4G无线通信涉及的算法均有较高的数据并行需求。单指令多数据(SIMD)处理器可以在并行数据通路上处理向量数据,并且能得到较好的能耗比。因此,SIMD处理器将会成为未来SDR系统的基础。然而,SIMD的缺点也很明显,即只有在数据通路被完全利用的情况下才达到高的处理性能。所以,本文在处理器设计中引入了变宽度的概念。结合实际硬软件条件,通过深入研究针对下一代移动计算的高性能数字信号处理器,完成一种基于SDR的变宽度SIMD处理器体系结构的设计和相应模块的设计仿真工作。

1 体系结构设计

1.1 4G终端物理层结构

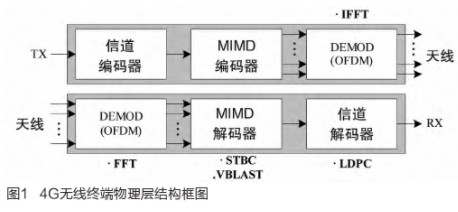

现今已提出的支持3G WCDMA和802.11的物理层结构无法满足4G系统高于3G系统两个数量级数据吞吐量的需求。为支持千兆级的数据吞吐量要求,4G系统将三种技术整合到了一起:即正交频分多址(OFDMA)技术、支持多天线并行的MIMO (Multiple-Input Multiple-Output)技术和前向纠错(LDPC)技术。4G无线终端的物理层结构如图1所示,它主要由一个信道编码解码器、一个MIMO编码解码器和一个调制解调器所组成。MIMO是一种多天线技术,支持多天线的发射与接收,其中运用的STBC(空时块码)和V-BLAST(Vertical-BLAST)算法分别用于增强信号质量和扩充信道容量。

1.2 体系结构设计

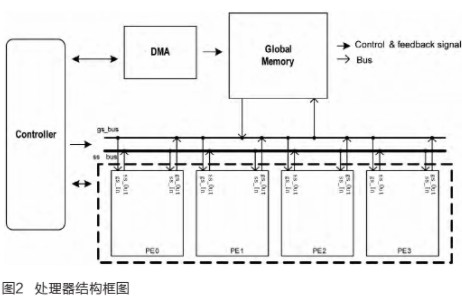

基于SDR的变宽度SIMD处理器体系结构如图2所示。该SIMD体系结构主要由4个模块组成:(1)多个PE核,主要用于无线协议和视频的相关算法的计算工作;(2)一个全局便签式存储器为PE核提供计算数据;(3)一个全局控制器,用于协调各模块之间的工作;(4)模块间双总线。

1.2.1 控制器

控制器完成对各个模块的状态控制和模块的初始化工作,主要由一个标量路径构成,包括初始化态和执行态两种状态。当处于初始化态时,控制器呈现出2级流水,分别为取指阶段和译码阶段;初始化阶段完成后,控制器进入执行阶段,此时将屏蔽取指阶段,不再从指令存储器中读取指令,而是依据DMA、PE核的状态信息,以及初始化时保存在控制器中的PE核间生产者消费者关系,产生相应的控制信号,用以协调各个PE核的协同工作。

1.2.2 DMA与Bus

DMA是不需要控制器干预的情况下独立完成批量数据的传输工作。控制器在初始化阶段对DMA进行初始化;当控制器进入执行阶段后,DMA也将开始独立传输数据,并且当一批数据传输完成后,DMA的计数寄存器值将还原成初始化值,再次执行之前的数据传输操作,从而重复为PE核提供计算数据。

本体系结构中的Bus结构为双总线结构:一条总线为32位,其中每16位为一组,用于PE核和全局数据存储器之间的数据通信;另一条总线为48位,也是以16位为一组,用于PE核间互联。

1.2.3 全局便签式存储器

全局便签式存储器的主要功能是为PE核提供计算数据,并接收PE核的计算结果。全局便签式存储器容量为128KB,字长为16位,具有一个读端口和一个写端口。当读写端口同时有效时,先读后写。读写地址线均为16位。

1.2.4 PE核

PE核主要由SIMD数据路径、标量数据路径、地址产生单元和局部存储器4部分构成。SIMD数据路径主要用于DSP算法的高强度计算,由64个计算lane组成。标量数据路径主要处理程序中的标量指令和无法向量化的指令。地址产生单元用于产生访问局部存储器块的地址;SIMD数据路径中每组计算lane都有各自独立的地址产生单元,所以一共有8个地址产生单元。局部存储器大小为32KB,平分为bank0和bank1两部分。同一时刻最多只允许一个bank接收数据,最多只允许一个bank在为PE核的计算模块提供计算数据。

1.3 工作模式

处理器设计中引入了变宽度的概念,即处理器可以支持多种向量宽度的算法,在支持窄向量宽度算法时,使用线程级并行性来充分利用硬件资源。从算法角度看,系统由几个主要的算法所构成,由于每个PE核具有足够强的计算能力,能独立处理一个完整算法,所以算法在对数据进行处理的过程中彼此之间通信很少,基本上是一种生产者和消费者的关系。可以把这些算法当做不同的任务,分配到不同的处理器核上运行,这样既可以有效地利用PE核的计算能力,又能很好地保证多核的并发处理。

以4G无线协议为例:4G无线物理层主要由调制解调器、MIMO编码解码器和信道编码解码器三部分组成。其中调制解调通过FFT和IFFT算法来实现; V-BLAST算法和STBC算法分别用来提升通信速率和通信强度。LDPC算法完成前向纠错部分的工作。每个算法的计算结果将作为下一个算法的计算数据,所以算法之间是串行关系,整体上多个PE核组成了一条宏流水线。

这里,PE核扮演的是一种“软ASIC”的角色。PE核的指令存储器中装载的算法是FFT算法,则此PE核将会完成FFT算法的计算操作。即当为PE中的指令存储器载入不同的程序后,该PE核也将实现不同的算法。

2 仿真验证

本文根据SIMD核取指、译码、执行整个过程以及指令集设计(限于篇幅这里没有介绍),采用硬件语言Verilog HDL对微体系各个部分进行了设计实现。综合电路如图3所示。

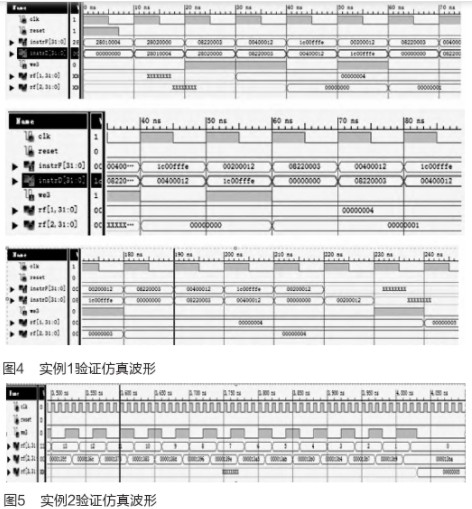

控制器流水线的主要工作是控制程序流,所以分支与跳转占其工作负载的很大一部分。涉及到流水线的设计,数据冒险也需要考虑。这里通过两个实例对几个关系进行仿真,以验证设计的正确性。

2.1 验证实例1

汇编源程序:

addi r0,r1,4;

addi r0,r2,0;

bret r2,r1,3;

inc r2;

jnt -2;

inc r1;

这段程序的目的是为了验证标量流水线的条件判断类指令和无条件跳转指令是否符合设计预期。仿真波形如图4所示。从验证波形可以看出,从0ns 时刻addi r0, r1, 4指令进入取指阶段开始,一直到240ns时刻程序段执行结束,整个运算过程结果都正确,最终寄存器r1的值变为5。2.2 验证实例2

汇编源程序:

addi r0, r2, 0;

addi r0, r1, 100;

add r1, r2, r2;

loop r1, -1;

addi r0, r3, 5;

这一段程序的目的是为了验证在4G 无线通信或视频算法中常见的循环计算,标量流水线的loop指令就是专为应对这样的计算所设计的。实例程序展示的是100以内的自然数求和。仿真波形如图5所示。

从图5可以看出,首先将寄存器r1和寄存器r2的值分别初始化为100和0;执行add r1, r2, r2指令,$r2 = $r2 + $r1。loop r1, -1指令判断是否寄存器r1的值大于0,如果成立,则跳转成立,寄存器r1值减1,跳转到add r1, r2, r2指令继续执行,如此反复。最终寄存器r2值为100以内的自然数的和5050,16进制表示为000013ba。循环结束,addi r0, r3, 5执行,置寄存器r3值为5。两个实例验证波形都验证了指令执行的正确性。

3 总结

本文以4G无线通信这一学术热点为研究对象,结合4G无线通信协议和高清视频中所使用的算法,研究和设计了基于SDR的变宽度SIMD处理器体系结构,包括处理器的工作模式、PE核标量流水线。仿真结果验证了该处理器体系结构设计的正确性。

下一步,本文将针对4G无线通信所涉及的算法进行并行处理,并对处理器进行并行处理实例验证。

责任编辑:gt

-

ADC技术在SDR实现中有哪些挑战?2019-08-02 0

-

如何为4D无线通信设计基于软件无线电及变宽度SIMD处理器体系结构?2021-05-20 0

-

Vector向量计算技术与SIMD技术的对比2021-09-01 0

-

32位ARM处理器开发过程中调试技术的研究与分析2021-12-14 0

-

Vector向量计算技术与SIMD技术的对比简述2022-03-09 0

-

Arm Cortex-M系列处理器进阶选型秘籍中,M4 SIMD支持多少MAC/cycle呢2022-09-15 0

-

ARM1136J-S处理器技术参考手册2023-08-02 0

-

ARM1156T2F-S处理器技术参考手册2023-08-02 0

-

Arm Cortex-A32处理器高级SIMD和浮点支持技术参考手册2023-08-02 0

-

Arm Cortex-A35处理器高级SIMD和浮点支持技术参考手册2023-08-02 0

-

SIMD计算机的优化编译器设计2009-04-03 713

-

适用于SIMD体系结构的FPGA分页仿真模型研究2011-03-15 669

-

一文看懂基于SIMD的媒体处理器2021-03-29 409

-

EE-267:在SISD和SIMD SHARC®处理器上实施就地FFT2021-04-25 633

-

EE-270:SIMD SHARC®处理器上的扩展精度定点运算2021-05-24 410

全部0条评论

快来发表一下你的评论吧 !