逻辑电平探测器电路图

电子说

1.2w人已加入

描述

逻辑电平测试器的原理

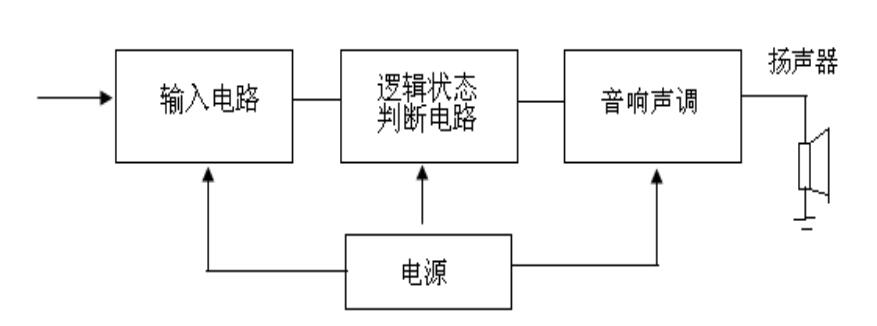

由图1可知,逻辑信号电平测试器电路由五部分组成:输入电路、逻辑状态判断电路、音响电路、发音电路和电源。

逻辑电平探测器电路

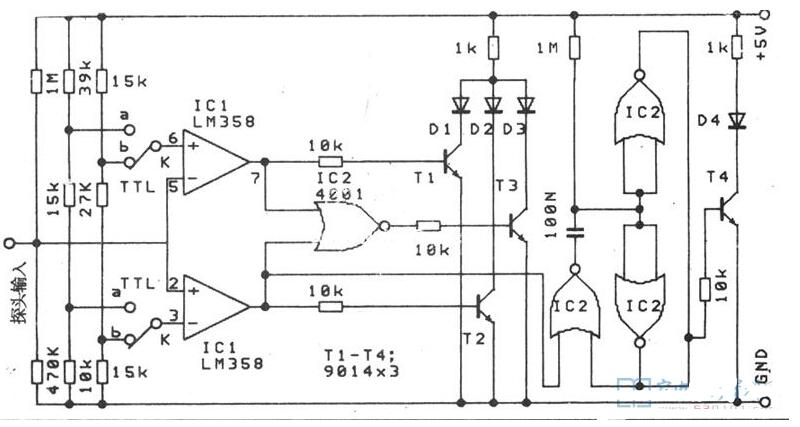

电路如下图所示,这种逻辑探测器,可探测TTL、CMOS高低电平及不确定电平。D1亮表示高电平,D2亮表示低电平,D3亮表示不确定电平(TTL在0.8V~2.0V之间,CMOS在3.5V~1.5V之间),D4亮表示探测点电压变化。电路如下图所示。IC1是电压比较器,通过开关K设置不同的电压基准,a处为TTL,b处为CMOS。T1、T2、T3用来驱动D1、D2、D3,使之点亮。IC2组成一个单稳态电路,以使T4驱动D4。该探测器的输入阻抗为330kΩ。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

全部0条评论

快来发表一下你的评论吧 !