“多模式交错电源” 的设计过程

电子说

描述

接下来小编给大家一起分享下这款 “多模式交错电源” 的设计过程吧!

先回顾下本次大赛内容:

参赛要求

1. Vin=12V, Vout=2.5V,lout=2A;整版使用电容合计容量,不得大于 60uF;

2. PCB 设计仅限于2-4层 (不接受6层及以上 PCB 设计);

3. 测试中,不允许切换工作模式。

评选规则

作品实物图

专家点评

设计思路清晰,满载效率高。

作品设计过程

1

方案介绍

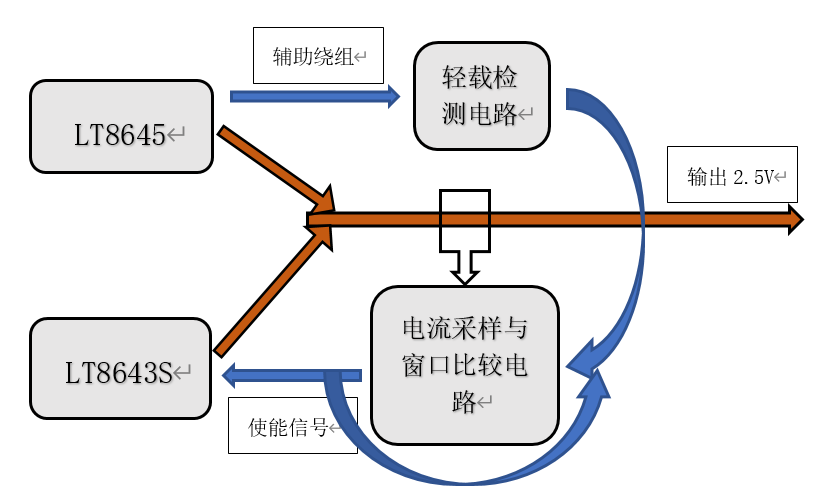

设计一款较好符合比赛要求的电源,需对电源的各方参数做出整合和推敲。 低纹波、小负载波动、高效率、低静态功耗均可用 ADI 芯片实现,但无法用同一个芯片达到所有指标的极致。其中最难的是效率的提升,这个局限于芯片和物理法则,不作为首要考虑的重点。 其次是动态响应,这要求电路快速动作,这显然与轻载和空载性能要求相反,具体可参考 LT8643 和 LT8645 的区别。将他们融合在一起谋求两个芯片性能的叠加,成为一个不错的选择。 解决方案为双路交替工作,功率级分别是 LT8643S 和 LT8645S,其中集成 MOS 开关的 LT8643S 可以在高频下实现快速响应的 CCM 模式,这款芯片还支持可配置的外部补偿,而 LT8645S 可实现低空载电流和满载的高效率,运行在较低的开关频率。 LT8645S 工作在 Burst 模式下,实现空载和满载的高效率,LT8643S 以 CCM 工作在 100mA 到 1.5A 的输出电流段,且输出设定电压比 LT8645S 高一点,当 LT8643S 开启时,LT8645S 自动处于休眠状态。 以上功能的实现需要低功耗输出电流采样电路,ADI 具有使能端 LTC2067 可以完美的用亚毫欧电阻对 0.1A 到 2A 的输出电流进行采样。 为了提高静态和轻载性能,读取 LT8645S 的状态信息作为电流测量控制逻辑电路的启动信号,这可以利用 LTC2067 的使能端和电感副绕组实现。控制框图如下图1.1.

图1.1 控制框图

本方案看似有3个状态,实际上只有两个,主工作状态是 LT8645,它的工作空白区间是 0.1-1.5A,在空白区间内是 LT8643 以超高的开关频率和超快的环路,抑制纹波,压低动态,而这整个模式切换只需要一个电流采样和窗口比较器控制 LT8643 的使能就可以实现。 这是我思前想后最简单的控制逻辑了,这个方案还有个优点,负责效率的电感和开关频率是独立与高速部分,便于优化最终的效率,负责高速的部分可以选取更合适的电感,以谋求最好的动态响应。

2

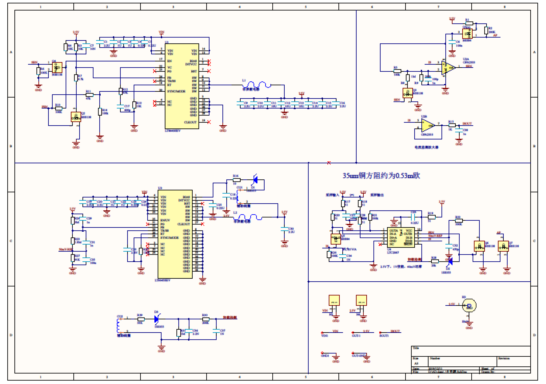

原理图设计

图2.1 原理图

(原帖可下载源文件)

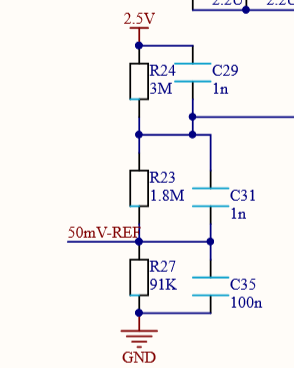

左上角部分为工具模块 LT8643,除了基本配置,外加一个控制使能的窗口电路,模式脚可以浮空,接上只是为了了解这个芯片的更多细节。 左下方为这个电路的基本结构,这个模块除了 LT8645 的基本配置和唤醒部分,最重要的就是那个阻容分压结构。这个区域放大图如下图2.2所示。

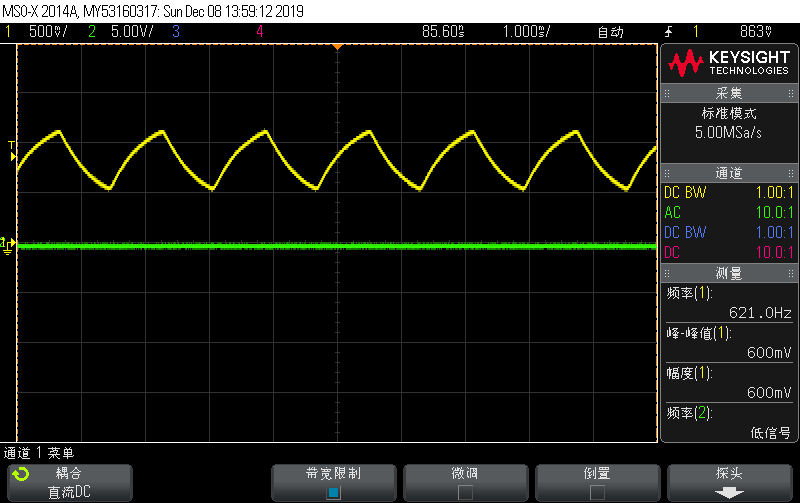

图2.2 阻容反馈及唤醒基准

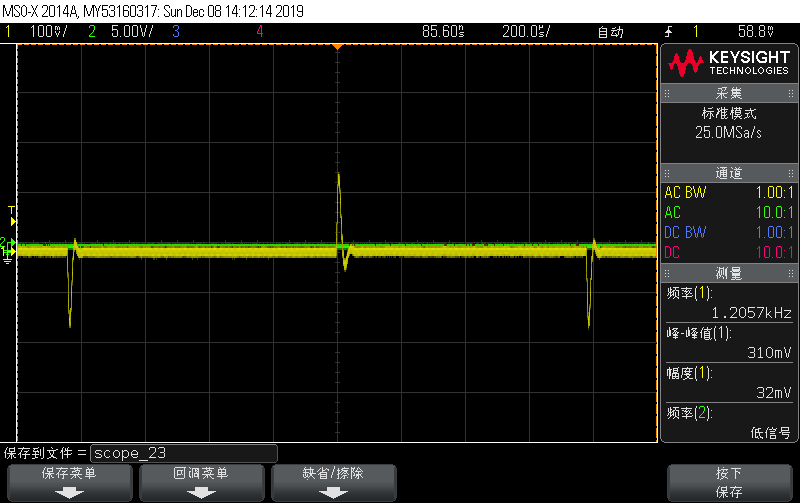

为了高的效率,LT8645 需要工作在大电感和低开关频率条件下,在之前的实验板上 LT8645 出现了运行不稳定的现象,可这个芯片没有外部补偿,只能通过其它方式使环路稳定,阻容分压结构就不错,可以在高低频之间产生一个零极点对,降低高频段的反馈系数和环路增益达到补偿的目的,下图2.3是在 4.5uh-370khz 小的 1A-2A 动态响应。可见环路的稳定性还是很不错的。

图2.3 动态响应

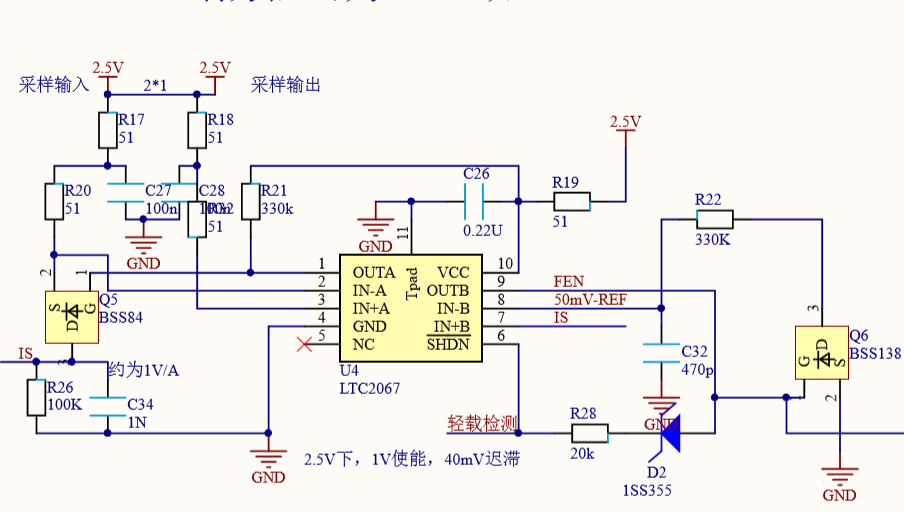

左下方为铜箔电流采样技术,电流检测芯片为 LTC2067,失调电压在 1uv 左右,铜箔采样电阻为 0.7 欧左右,采样电流的精度校准使用下部电流源的负载电阻。这个模块也是这个电路在调试时遭遇 “玄学” 最多的地方,下图2.4是该区域的放大图。

图2.4 电流采样电路与唤醒

图2.4中左侧构成了最普通的电流检测结构,最初的问题是 LTC2067 的供电是以地为参考的,并且通过 rc 结构从输出电压上取电,这种结构可以保证这个芯片的使能端被外部轻载检测触发启动。

正是这个结构导致了严重的问题,左侧2、3号脚要承受大量高频共模,这将导致两个严重的问题,首先是小电流的采样完全是错误的,容易在没有负载的情况下容易被干扰 (示波器电流探头测量 PWM 时) 触发 LT8643 的启动,另外一个问题是电流检测的非线性,这个原理不明,应该和放大器内部结构有关。

上述问题可以通过在这两个引脚和采样铜箔间插入 rc 滤波器来缓解,事实证明这种措施十分有效,电流采样电路对动态采样结果如下图2.5,实际在 10mA-2A 误差不超过 5%。

图2.5 电流采样

此处二号 “玄学” 是电流采样输出脚的迷之漏电流,经过反复排查,确定初始漏电流由斩波放大器引脚输入引发的电荷泵效应将高电压引脚的的电荷泵送到低电位的引脚。

发生这种神奇现象的根本原因是我用斩波运放 OPA2333 作为比较器,因为手头可以工作在低电压的低功耗运放或比较器不多。

这个问题通过更换普通低压运放后,唤醒后的漏电流问题基本解决,其实不完全解决,LT2067 也是斩波运放,另一半也是连接电流采样作为比较器使用,用来使能 LT8643 和自锁使能端,可能由于引脚压差太小或内部特殊结构,没有形成可观漏电流。

之后是漏电流二号出场,这次漏电的原因是外部运放的强行使能导致电流流过芯片通过 ESD 结构从运放输入脚漏向电流采样端口。这个现象发生在实验板上,是外部运放使用低侧 MOS 开关跟随 LT8643 一起被唤醒,在未唤醒前运放的地引脚浮空,被内部漏电拉到高电平,这个地又和输入脚有个二极管,自然就会从这个脚向外漏电流。解决方案使用一个 NMOS 和一个 PMOS 同步驱动,将芯片和地同时断开。

上面的操作引出了漏电流三号,漏电流三号表现非常诡异,在示波器可以看到控制逻辑回路在稳定震荡。

在没有任何输出电流的情况下,电流采样输出出现间距极大的小尖峰,这个小尖峰启动自锁结构,所有芯片正常供电,电流恢复到正常状态,因为没有电流输出,自锁信号被电流测量信号复位。然后外部运放切离电源,戏剧性的一幕出现了,外部运放下 MOS 比上 MOS 断开速度更快,差了一个低速反相器时间,这个瞬态和上一种漏电流现象一样,漏出一个电流尖峰 (极窄,不用单次触发观察不到) 到电流采样输出,唤醒自锁,就这样往复循环。

上述电流采样和控制逻辑出问题的根本原因是我对斩波运放认识不够深刻,还试图强行给芯片加使能。

3

PCB设计

PCB 为双层,正反面如下图3.1、3.2,实物图,如图3.3。

图3.1 PCB正面

图3.2 PCB反面

图3.3 实物图

实物测试

图4.1 测试电路

5项指标测试: ❶ 静态电流空载电流为2.3ua左右 ❷ 轻载输入电压和电流为11.870v、33.7ua,输出电压2.503v,负载为20k,效率计算为78.4%。 ❸ 纹波纹波出现时,电路切换到 LT8643 的 CCM 模式,开关频率2.6MHZ,纹波基本不可观测,接近低频噪声的幅度,总的幅度不超过3mv。 ❹ 动态测试这块板子的动态性能十分优秀,最大峰值 10mv 左右,上下峰峰值加起来也只有 15mv 左右,如下图4.2、4.3、4.4。

图4.2 动态响应,绿线电流波形

图4.3 动态响应上冲

图4.4 动态下冲

❺ 2A效率为了优化 LT8645 的效率,选取了6个不同的频率点测量效率取其最优解。 分别取 374KHZ、388KHZ、405KHZ、418KHZ、442KHZ、483KHZ,其中在 405KHZ 处达到最高效率94.6%。其它各点效率如下:94%、94.4%、94.4%、93.9%、93.7%。

-

改进交错式DC/DC转换器2011-07-14 0

-

面向电池充电应用的 120V AC 输入·200W 交错反激式2015-04-29 0

-

AD9767交错模式使用中5V指的是哪个?2019-02-20 0

-

开关电源的多模式控制2019-03-25 0

-

详解时间交错技术2019-07-23 0

-

内存交错的功能是什么?2019-09-18 0

-

交错边界传导模式PFC2020-08-12 0

-

面向电池充电应用的200W交错反激式参考设计2022-09-23 0

-

交错式平均电流升压型功率因子修正器的研究2010-03-20 566

-

电源转换的交错式PFC控制技术应用2010-04-28 1985

-

基于交错反激的微型逆变器不同工作模式控制策略的仿真研究2016-12-15 755

-

600W 交错式双相转移模式 PFC 转换器—PR7352021-04-05 2756

-

Boost模式下交错并联磁集成双向DCDC变换器的设计准则2021-09-27 692

-

使用 FAN9611 / FAN9612 的交错边界传导模式 PFC 的设计考虑2022-11-14 187

-

设计100~1000W AC/DC交错式PFC电源?我们有一款高效、可靠、易用的解决方案~2023-09-28 1292

全部0条评论

快来发表一下你的评论吧 !