两款多级输出的延迟电路图解析

电子常识

2593人已加入

描述

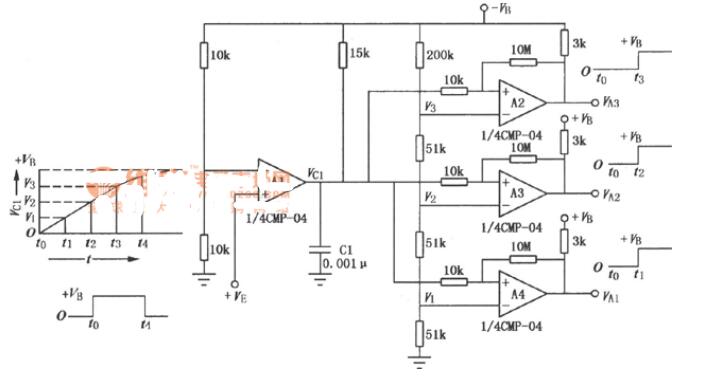

多级输出的延迟电路图(一)

如图是具有多级输出的延迟电路。电路中采用了运算放大器作比较器,当运算放大器A1的同相输入端加电压+VE后,在运算放大器A2、A3、A4同相输入端上的电压VC1将沿着指数曲线规律上升。运算放大器的反相输入端加入由分级分压器提供的电压。因此各运算放大器输入在Vc1由零变为+VB(电源电压)的t1、t2、t3时刻,分别使各输出信号翻转,从而实现了VA1、VA2、VA3逐级延时的目的。注意本电路使用了双电源,即正电源+VE、+VB与负电源-VB。

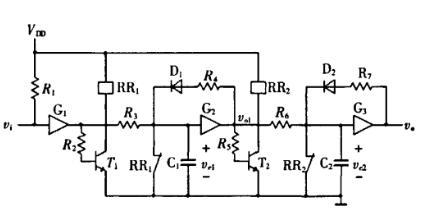

多级输出的延迟电路图(二)

图2为一种采用CMOS同相缓冲器组成的两级电容充电式长时问延时电路根据上述分析方法,第-级和第二级的延时时间分别为:

(综合整理:mcu资讯、百度文库)

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

- 相关推荐

- 延迟电路

-

两款u***功放制作2012-08-20 0

-

求主板电路图解2013-07-21 0

-

美国国家半导体两款低功率LVDS 2x2交叉点开关电路2018-08-27 0

-

AP65500和AP65400两款降压型转换器2018-09-28 0

-

Exar两款多路输出同步降压型的可编程电源模块2018-09-28 0

-

吉时利仪器两款2290系列优化的高压电源2018-11-30 0

-

2V升5V的升压芯片,两款芯片电路图2020-12-14 0

-

电子灭蝇器电路原理图解析2021-04-27 0

-

220V电子镇流器电路图解析2021-04-28 0

-

250种功放电路图解!2021-08-12 0

-

多级负反馈放大电路图2007-11-25 1074

-

长延时电路图解2009-04-13 879

-

华硕电脑电路原理图解析2013-09-09 7853

-

常见的电子元件及电路图解析2021-06-27 7200

-

USB接口电路图解析2022-08-25 20057

全部0条评论

快来发表一下你的评论吧 !