EMC设计重要点关注时钟

电子说

描述

从1月份到现在,全球都被这个病毒闹的不安生,地球村背景下,能独善其身?都是环环相扣,一个一个的在封,然后一堆材料开始告急,特别是一个小国家,这一闹,怎么弄?天朝,产生链算完整的,但一些关键元器件国外在把持着,根本无货。

今天跟兄弟们聊聊时钟。

大部分的技术资料都会告诉你,EMC设计重要点关注时钟

为什么?因为是时钟是EMC三要素中重要的骚扰源,所以要重点对待。

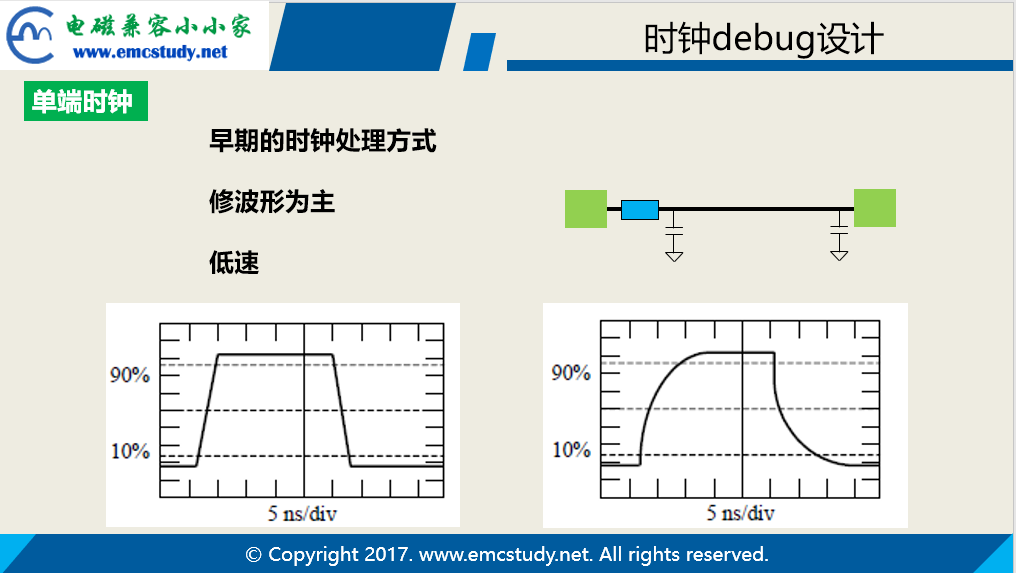

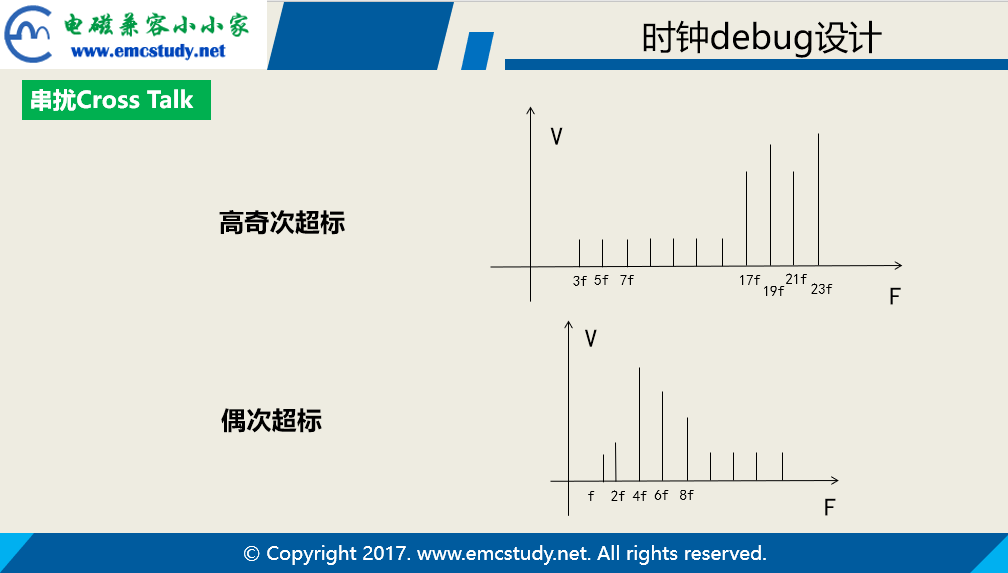

图示是标准理论方波的时域和频域波形,我们根据波形的频谱来做具体的设计。大部分情况下,我们时钟都是奇次谐波能量高,理论上偶次谐波为0,但事实上做不到。所以就单端时钟而言,设计主要集中在奇次谐波上。

(1)你可以在时域内衰减幅度A,从而降低各谐波的幅度,实现频域内的降低

(2)你可以通过加旁路电容,减缓上升沿,吸收杂波。

这是骚扰源能量降低基本的手法,也是最省心的,所以许多兄弟看到时钟就一顿猛操作,远场一看有点效果,都非常的开心,有时候为了达到某个裕量,揍的有点狠,比如电容加个100PF,电阻串上100ohm,甚至更大。当速率比较低的时候,系统是勉为其难的在工作,时间长了,系统工作是非常不稳定的。

你修的图时域波形可能就像上图一样,已经快变形了,速率慢的时候负载端能正常识别,到了一定程度,基本就挂了,所以整改时悠着点。

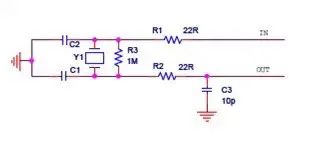

图示是晶体的基本原理图,除了原理上需要的R3、C1和C2之外,R1、 R2和C3组成了基本的EMC电路,大部分情况下还会多一个C4给R1(没找到图,懒得重新画)。大部分兄弟都会盯着这四个器件一顿狂揍,某些时候效果很明显,你可能就差哪几个db,然后就没有然后了。

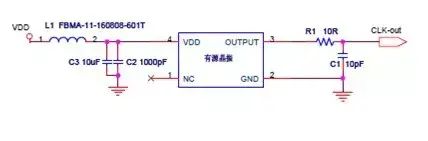

上图是晶振的基本原理图,电源VDD大部分情况下会做成图示的那样,LC滤波,但我们建议你最好做成PAI型滤波,去耦和旁路同时去做,电容从高到低都配上(高频、中频和低频都配上)。输出端的RC是标配,兄弟们都会根据自己的测试结果来调整。

上面的内容是不是都懂,都会,好像不用我太多说。

咳咳

以我个人多年的经验,这两个源做基本的衰减和滤波足矣,不必过头。

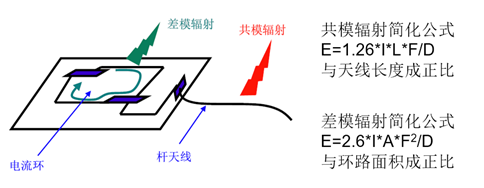

先回忆一下杨老师的经典公式

公式中差模辐射因其跟信号整个环路相关,如果你的电路都是短距离传输的,比如我们上面讨论的驱动时钟,都离IC很近,那么其差模分量还是很小的。尽管能量不高,但我们还是很注重在PCB设计时控制其环路面积,所以大部分的guideline都会要求你尽量靠近IC。共模辐射与天线长度成正比,大部分兄弟都会忽略这一点,因为在实际电路中并没有明显异常的天线在。

但是大部分的EMI问题都是因为多次串扰耦合的问题,这句话是不是耳熟,因为我讲课时常说,老工程师也这么说。其中重要的原理就是时钟电路周围存在许多未知的L,因为共地和共电源的问题,这些能量会多次串扰找到一个合适的L发射出去。

然后就出现了类似上图的现象,是不是常见,这种情况,你把时钟揍死了,看到的效果都一般般。然后有兄弟感慨,为啥我处理半天时钟咋没反应呢,我的时钟明明就对应着他呀。老工程师会心一笑,too young。

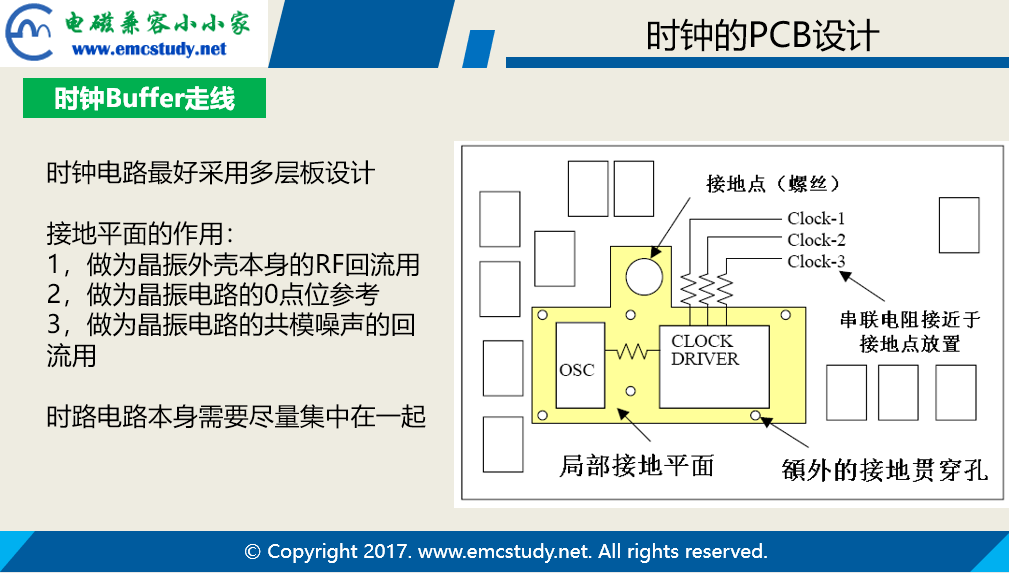

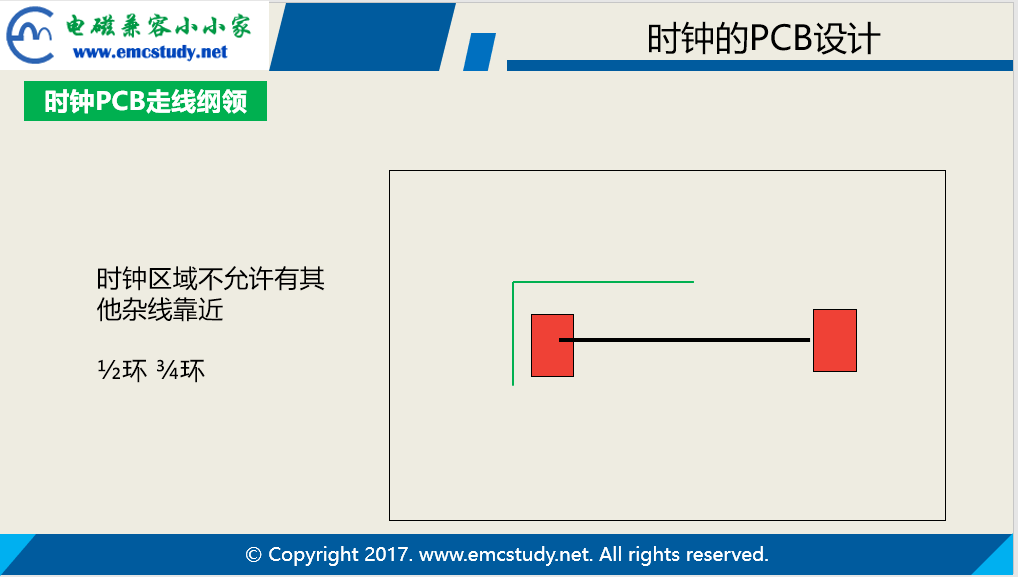

为了减小后期一些莫名其妙的串扰,所以会对时钟电路周围做一些规则限制。上面是另一经典的图,许多老师都会引用,结合我们上面说的原理,这时候理解这个图是不是轻松多了。为了降低时钟电路能量可能的串扰,首先需要多层GND平面尽量多拾取时钟电路产生的能量(自行脑补这部分电路产生的电力线和磁力线分布图),这部分能量尽量少往空中耦合,必要的时候可以采用局部屏蔽(示意图中有BUFFER)。其次尽量将时钟线走到内层(原理同样是控制电力线和磁力线在空中的分布)。

上述的要求,相对来说容易做到,基本没有歧义,但这还是属于骚扰源设计范畴。

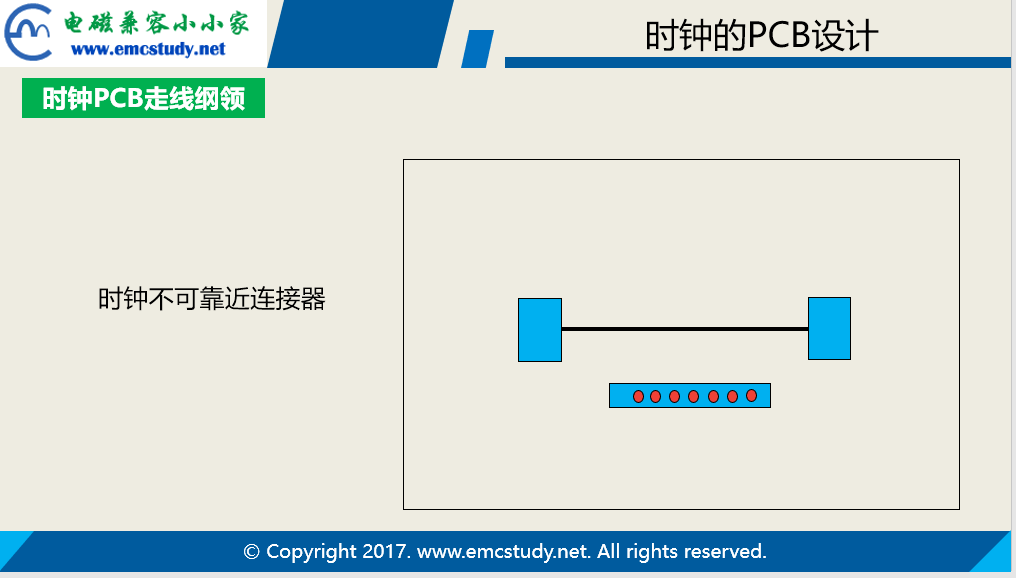

当时钟电路有连接器时,就会出现主动拾取干扰会二次耦合发射的问题,这个相对容易发现,原理上做滤波,破坏天线效应即可,然后就能看到,连接器的pin上加了一堆的滤波电容。

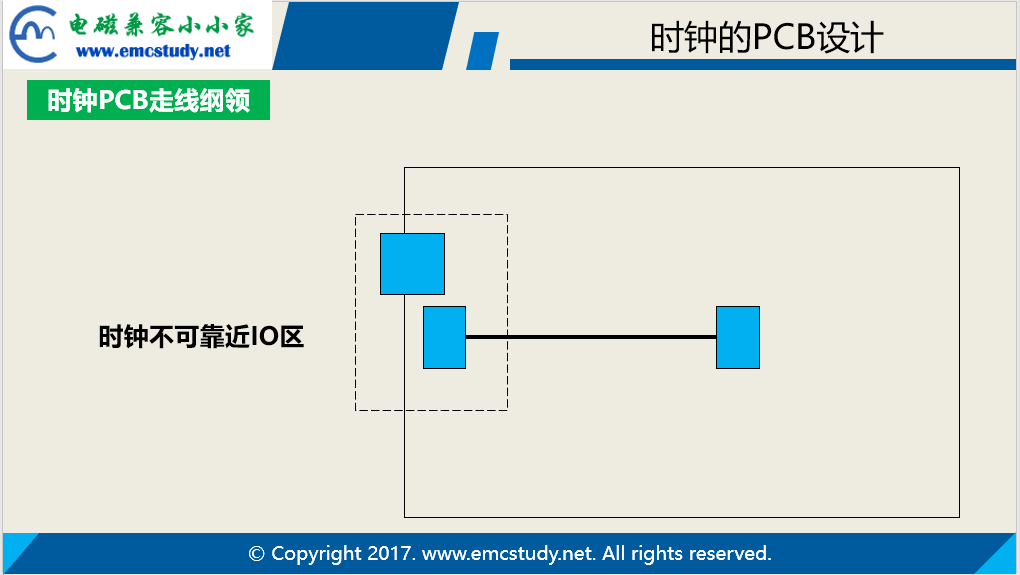

时钟电路如果靠近IO,这个天线效应同样容易理解,但是因为线缆较长,会带来其他的问题。

这个大部分人很难处理,大部分的借口是板子密度太高,但是这是我们工程上见到的最多的隐藏天线,这时候你会发现我们时钟线走在内层是多么的明智。

这些杂线在PCB设计时就是重中之重了。

(1) 内层走线,且与时钟不同层

(2) 3W法则(10W或更高)。

难就难在很难全部做到,有时候这么做了,却是过设计,但你不这么做,可能是隐患。这种一次侧的耦合相对容易发现,现实中因为低层板设计,将EMI设计提高了好几个难度等级。越是这样,后期的对策越难做。

所以,在设计之初,尽量多做一些规则检查,即使做不全,后期排查时也会做到心中有数。

最后,我依然十分诚恳的建议兄弟们,把注意力多放在串扰耦合中,多年的高速设计(通信行业中25GHz这样的高速)经验会告诉我们,串扰是EMI设计第一杀手。

-

解析EMC滤波器:功用、设计与应用?|深圳比创达电子EMC a2024-01-22 0

-

EMC接地设计要点 - .接地EMC设计-4赛盛技术 2022-04-27

-

6.2 EMC 设计要点(二)jf_06209345 2022-09-23

-

EMC设计、工艺技术基本要点和问题处理流程2015-08-25 0

-

【EMC家园】电容滤波的要点2016-01-16 0

-

【转帖】EMC的处理需要遵循的要点有哪些2018-09-04 0

-

良好的EMC性能的PCB布线设计要点2010-03-13 994

-

杨庆新:关注半导体照明中的EMC问题2011-11-01 731

-

EMC设计中电容滤波的两个要点2012-06-25 2967

-

电容滤波在EMC设计中的重要性2012-11-13 1925

-

汽车DCDC电源芯片EMC设计要点的详细资料说明2019-04-02 2638

-

USB硬件EMC设计要点分享2020-07-21 5226

-

EMC有哪些重要的规律2021-01-06 763

-

EMC三个重要规律2022-02-12 957

-

AT32微控制器硬件设计指南及抗EMC设计要点2023-09-19 96

全部0条评论

快来发表一下你的评论吧 !