一位串行BCD加法器电路

信号处理电子电路图

328人已加入

描述

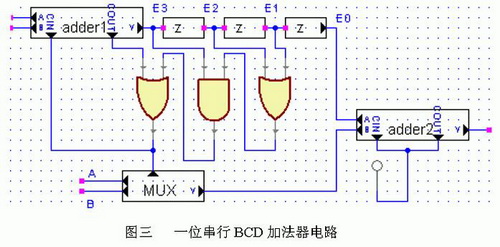

图三所示为一位串行BCD加法器。它是以牺牲速度以达到减少硬件逻辑门的目的,这种电路在对频率要求不高的系统中非常之适用。其中ADDER1、ADDER2均为一位全加器。ADDER1 做主运算器,ADDER2做BCD校验运算器,不管是否做BCD校验,ADDER2的初始进位、借位始终为“1”。

打开APP阅读更多精彩内容

图三中Z型门为延时电路,延时一个时钟周期,这样在外部电路控制下,经过四个时钟周期,得到一位十进制BCD结果E3E2E1E0.由电路图所以当 C+(E3E2+E3E1)逻辑值为‘1’时,控制多路选择器选择A通路(A通路为序列 1001),当C+(E3E2+E3E1)为‘0’时,选择B通路(B通路序列为1111),即需要校验时,多路选择器输出序列1001;不需要校验时,输出序列1111,与Z型门的输出对应相加,并且ADDER2的初始进位始终为‘1’,由此可完成BCD的校验工作。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

- 相关推荐

- 加法器

-

加法器电路原理图解2018-10-11 0

-

32位浮点加法器设计2013-10-20 0

-

两个4位加法器级联构成一个8位加法器 verilog怎么写啊?!!2013-12-03 0

-

加法器2016-10-20 0

-

什么是加法器?加法器的原理是什么 ?2021-03-11 0

-

4位加法器的资料分享2022-07-07 0

-

多位快速加法器的设计2010-05-19 928

-

4位并行的BCD加法器电路图2009-03-28 12242

-

加法器,加法器是什么意思2010-03-08 5151

-

十进制加法器,十进制加法器工作原理是什么?2010-04-13 12861

-

同相加法器电路原理与同相加法器计算2016-09-13 55504

-

运算放大器的同相加法器和反相加法器2022-08-05 23103

-

加法器的原理及采用加法器的原因2023-06-09 3764

-

半加法器的工作原理及电路解析2023-06-29 5757

-

镜像加法器的电路结构及仿真设计2023-07-07 1313

全部0条评论

快来发表一下你的评论吧 !