上拉电阻和下拉电阻的主要作用

描述

上拉电阻和下拉电阻的主要作用

1. 提高电压准位

当TTL电路驱动CMOS电路时,如果TTL电路输出的高电平低于CMOS电路的最低高电平,这时就需要在TTL的输出端接上拉电阻,以提高输出高电平的值;OC门电路必须加上拉电阻,以提高输出的高电平值。

2. 加大输出引脚的驱动能力

有的单片机引脚上也常使用上拉电阻。

3. N/A引脚(没有连接的引脚)防静电、防干扰

在CMOS芯片上,为了防止静电造成损坏,不用的引脚不能悬空,一般接上拉电阻降低输入阻抗,提供泄荷通路。同时引脚悬空就比较容易接收外界的电磁干扰。

4. 电阻匹配

抑制反射波干扰,长线传输中电阻不匹配容易引起反射波干扰,加上下拉电阻使电阻匹配,能有效的抑制反射波干扰。

5. 预设空间状态/默认电位

在一些CMOS输入端接上拉或下拉电阻是为了预设默认电位。当不用这些引脚时,这些输入端下拉接低电平或上拉接高电平。I2C等总线上空闲时的状态是由上下拉电阻获得的。

6. 提高芯片输入信号的噪声容限

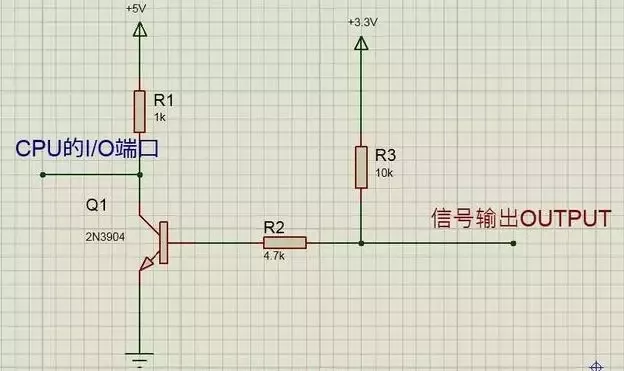

输入端如果是高阻状态,或高阻抗输入端处于悬空状态,此时需要加上拉或下拉电阻,以免受到随机电平的影响,进而影响电路工作。同样,如果输出端处于被动状态,需要加上拉或下拉电阻,如输出端仅仅是一个三极管的集电极,还可以提高芯片输入信号的噪声容限,增强抗干扰能力。 在BJT晶体三极管的基极端,上拉电阻和下拉电阻也起着至关重要的作用。在三极管的电路应用中,串接在基极上的电阻起限制基极电流的作用,如图1中的R2所示:

图1

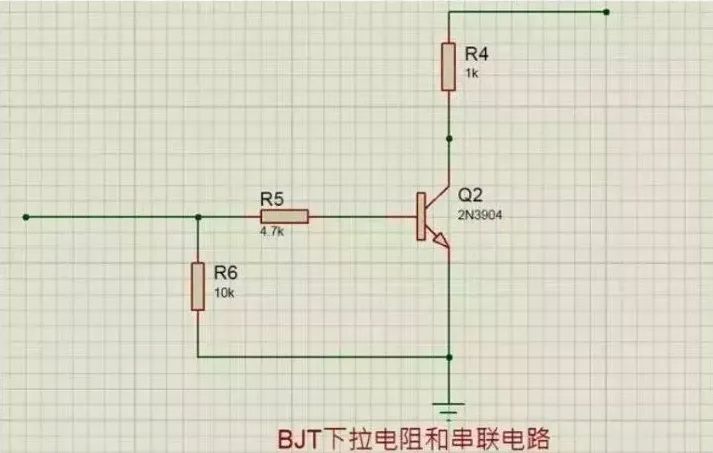

如图2中的R5所示,上拉电阻使三极管基极的输入电平在默认情况下是高电平输入,当CPU有低电平信号输出时,外围电路响应,下拉电阻使晶体管的基极输入在默认情况下拉到低电平,如图2中的R6所示。

图2

-

拉电阻:上拉电阻、下拉电阻的作用#电子元器件jf_97106930 2022-08-27

-

上拉电阻和下拉电阻的作用2008-05-22 0

-

上拉电阻下拉电阻的总结2011-09-19 0

-

上拉、下拉电阻的作用2012-08-20 0

-

拉电阻、下拉电阻的原理和作用2014-11-17 0

-

电阻的上拉与下拉作用2018-06-28 0

-

上拉电阻与下拉电阻有什么作用2019-05-20 0

-

上拉电阻和下拉电阻问题2019-06-27 0

-

上拉电阻与下拉电阻的定义及应用2021-10-14 0

-

上拉电阻和下拉电阻是如何确定2021-11-12 0

-

上拉电阻与下拉电阻最基本的作用2021-12-13 0

-

上拉电阻与下拉电阻概述2021-12-13 0

-

理解上拉电阻与下拉电阻的原理与作用2022-01-14 0

-

上拉电阻与下拉电阻怎么接线2022-01-14 0

全部0条评论

快来发表一下你的评论吧 !