fir分布式滤波的fpga实现

可编程逻辑

1339人已加入

描述

此设计的结构包括:1.移位寄存器链,n阶的有n-1个寄存器。

2.第一次累加部分。由fir滤波系数对称可得到对称的寄存器相加可以减小电路规模,所以第一次累加很有必要。

3,锁存并移位部分。此部分是为了通过移出lut地址,通过给出lut地址即可得到lut输出。

4,lut部分,该部分实现的主要功能是输出不同地址情况下的结果。

5,二次累加部分。该部分是将每一位卷积得到的结果加权累加,需要注意的是,由于是采用补码运算,最高位加权后应该是被减去而不是被加上。

分布式滤波器的原理如下

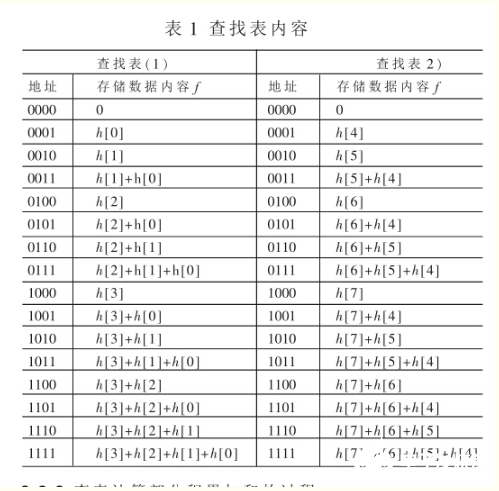

查找表的实现可参考下表

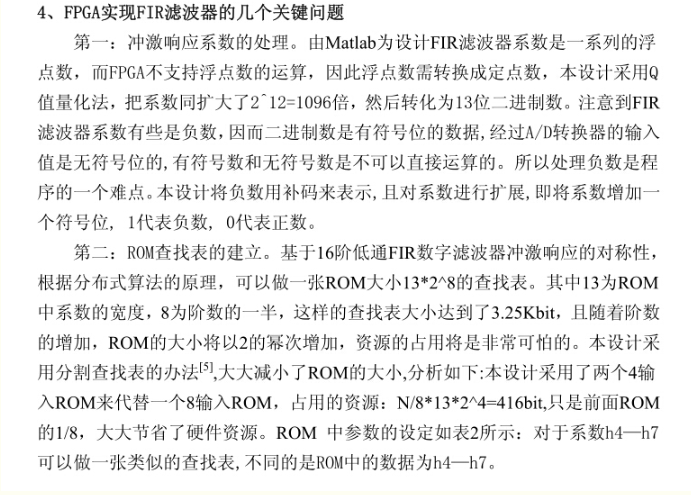

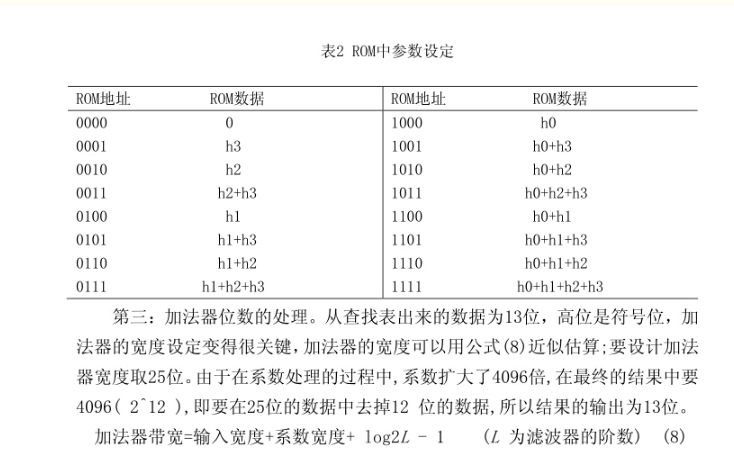

实现过程的几个关键问题:

这次设计就在加法器带宽处产生问题,带宽不够,发现出来的波形顶部挪到低下去了,通过看中间数据发现是数据位宽不够造成的,根据这个公式得到的加法器带宽刚好能满足设计需求。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

基于FPGA的FIR滤波器设计与实现2012-08-11 0

-

fpga实现滤波器2012-08-12 0

-

《无线通信FPGA设计》分布式FIR的并行改写2017-02-26 0

-

一个基于FPGA的FIR滤波器的问题2018-02-25 0

-

求一种基于FPGA分布式算法的滤波器设计的实现方案2021-04-29 0

-

请问一下基于分布式算法的FIR滤波器怎么实现2021-04-30 0

-

如何设计基于分布式算法的FIR滤波器?2021-05-08 0

-

FIR滤波器的FPGA实现及其仿真研究2009-08-31 458

-

基于分布式算法的FIR滤波器的设计与实现2009-09-02 502

-

FIR数字滤波器分布式算法的原理及FPGA实现2009-10-27 813

-

应用分布式算法在FPGA平台实现FIR低通滤波器2009-12-14 554

-

一种基于分布式算法的低通FIR滤波器2017-11-24 3029

-

如何使用FPGA和分布式算法实现FIR低通滤波器的设计2020-09-14 673

-

如何使用FPGA实现分布式算法的高阶FIR滤波器2021-03-23 755

全部0条评论

快来发表一下你的评论吧 !