可实现满足电源预算要求的FPGA设计

可编程逻辑

描述

前言

随着便携和以电池供电的应用快速增加,低功耗设计已成为延长电池寿命所不可或缺的任务。此外,在决定产品尺寸、重量、和效率时,功耗也扮演了重要角色。由于消费性电子的生命周期越来越短,具可程序特性,且能轻松为产品增加差异化特性的FPGA在消费应用中日亦受到重视。因此,想要达到最佳的静态与动态功耗,必须取决于选用适当的FPGA架构。

Actel的闪存FPGA是业界低供耗的领导厂商,除了闪存 FPGA本身的低功耗特性外,设计人员还可利用一些技巧来进一步降低系统总体功耗。在这篇文章中,将综合介绍易失性FPGA的电源特性,以及如何在进行板级设计时,降低系统的静态与动态功耗,包括RAM、I/O、以及频率树等。

基于闪存的 FPGA的电源特性

传统以来,在选用FPGA组件时,成本、容量、效能、封装形式等,通常是系统架构师或设计人员的主要考虑。但随着包括便携消费电子、医疗等要求低功耗的应用快速兴起,现在,功耗效能也已成为选用FPGA时的首要考虑。一般来说,设计人员对ASIC或FPGA的静态与动态电源特性都相当熟悉,但却可能不了解基于闪存的易失性FPGA具备有别于传统基于SRAM的电源特性。

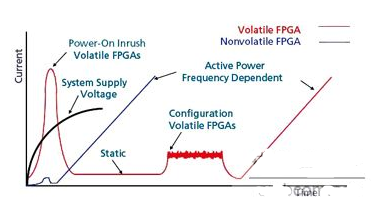

易失性FPGA有两个额外的电源要素:在系统通电时,编程所消耗的配置电源(configuration power),以及在FPGA组件通电时所散失的突波电源(inrush power),如图1所示。

图1. 易失性vs. 非易失性FPGA的电源特性

基于FPGA的板级设计人员在选择电源供应和电池时,必须将配置电源与突波电源都纳入考虑。尽管基于SRAM 的FPGA供货商都试图降低突波和编程电源,但是在单一电路板上有数颗 FPGA,或它们是在不同的电路板上,却由相同电源供电的情况下,这两个电源成份还是会产生严重的负面影响。

若系统有频繁的On/Off周期,此一额外的电源消耗就会更加严重,这在预估电池寿命时,一定要特别考虑进去。

另外,易失性FPGA需要外部启动PROM作为配置储存,这也增加了总体的电源消耗。即使有些供货商在装置中内建了大容量的闪存,但此额外的储存电源还是会存在。

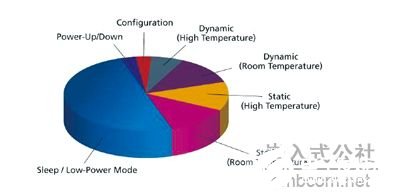

因此,要选择一能够改善电源的策略时,系统架构师与设计团队必须了解确实的系统操作模式以及相对应的电源情境。如图2所示,此一系统的电源特性显示出,此系统会在不同的温度下操作,且其工作与闲置周期时间比大约是1:1。

透过这样的图形显示,有助于做出正确的电源设计策略。以图2的案例来说,显然,设计人员必须尽力降低温度、静态、以及动态电源。

图2. 系统操作模式和电源分布

降低静态电源

只要当FPGA通电之后,不管是否运作,都一定会有静态电流产生,而它亦称为晶体管漏电流,此现象会随着工艺缩小日益严重,而且当组件在运作时,会造成温度的上升。不过,虽然静态电流增加,但相较于动态电流,还是比较小。

降低静态功耗的方式有很多种,对FPGA设计人员来说,应该遵循以下三个基本原则:最小的晶粒、最少的资源、熟悉FPGA架构。

FPGA产品通常都会包括一系列不同容量与不同特性的不同晶粒。因为,晶粒越小,其静态电源就越小,因此FGPA设计人员应该在确保效能目标可满足的情况下,选用系列产品中晶粒最小的组件。

“最少的资源”是指,设计人员应尽量减少RAM、PLL、I/O等资源的使用。举例来说,要降低I/O数量,设计人员就必须使用时间多任务(time multiplexing),以及最少的I/O数量设计区隔,此技巧能协助关闭I/O组(bank),或降低一个组中所需的I/O标准数量。

“熟悉FPGA架构”意味着,设计人员需了解PLL、RC、振荡器、I/O 组等动态资源的各种不同断电模式。以Actel IGLOO FPGA为例,它可提供具不同电压的相同I/O标准。因此,采用较低的参考电压,可能会显着改善静态功耗。

而电路板设计人员在决定热能管理、电压水平、阻抗负载时,扮演了一个关键的角色。温度上升会影响静态电源,而静态电源的非线性增加不只会导致静态电源的增加,同时也会产生更严重的散热问题。利用冷却技巧尽量降低周围温度不是一件简单的工作,特别是在电路板空间和成本都有限的条件下。

此外,将输入电流驱动到完整电平、避免阻抗负载、以及将无用的接脚接地等,都是降低静态电源的有效方法。

降低动态电源

动态电源与以下各种参数有关:

# 使用的FPGA资源,包括逻辑模块、频率树、嵌入式RAM、PLL等

# I/O上的负载和阻抗终端(resistive termination)

# 数据类型、信号活动或切换率 (toggle rate)

# 信号静态可能性(probability)

与降低静态电源相较,设计人员在处理动态电源时必须更为谨慎,且须透过后布局(post-layout)、电源模拟等分析工具,先得到明确的设计动态电源分布图形(power profile)。

动态电源分布图形能够清楚呈现出每个FPGA所使用的资源。因为FPGA具有弹性,一个相同的装置上,可以有多种不同的应用类型,所以若没有深入了解实际的动态电源分布,便无法有效地处理这个问题。图3所示为三种不同的设计类型。分析MPEG的电源分布,可以让设计人员避免花时间降低I/O动态电源,但是,若对系统控制器来说,就应特别将电源优化和热管理聚焦在I/O问题上。

图3. 不同应用有不同的动态电源分布

动态电源主要是由RAM、I/O、频率树、逻辑电源等因素所造成,接下来将分别介绍降低不同类型动态电源的技巧。

RAM电源消耗

RAM模块在读/写操作时会消耗电源。主要造成影响的信号包括地址线(address line)、Read Enable(RE)、以及Write Enable(WE)。

通常,读取的电源消耗会比写入高一点,而RAM读/写的电源会随连续地址的汉明距离(Hamming distance)增加而变大。因此,应该尽量在启用读取信号前,先尽可能执行最多的写入操作,然后,在切换回写入操作前,尽可能读取内存以取得所需的数据,这样才能有效降低 RAM电源消耗。

在降低峰值 RAM电源方面,可以考虑采用将读取和写入操作置于频率边沿(clock edge)的反侧,或是对RAM读/写埠上的频率予以门控 (gate)。

I/O电源消耗

FPGA I/O电压通常比核心电压大,而且通常I/O 组(bank)会消耗不少的电源,因此设计人员在决定选用I/O标准、接口频率需求、接脚限制等设计时,都需要非常谨慎。

差动式 (differential) I/O,如LVDS、LVPECL和阻抗终端式I/O,如HSTL、SSTL等,通常其静态电源较高,但动态电源较低。因此,对有较高切换(toggle)频率的设计来说,可以选用这些I/O。

降低 I/O 数量是重要关键,设计人员应重新考虑整体的设计/功能区隔(partitioning)是否恰当?以及是否可能用时间多任务(time- multiplexed)的方式减少I/O数量。此外,由于高切换频率会导致动态电源增高,为了降低 I/O的活动或切换率,设计人员必须消除 I/O驱动器输出端的非预期突发信号(glitch)。另一个常用技巧是,选择可降低切换位的总线编码(bus encoding),并将总线上的连续数值关联在一起。

频率树电源消耗

频率树(clock tree power)系与频率成正比,而且不管区域中的活动是否进行,频率树电源仍会持续消耗。而传统的频率门控(clock gating)技巧是有效降低电源消耗的方式。

以芯片级的频率门控为例,一般常用的系统级频率门控技巧可使整颗FPGA的频率暂停,有效停用所有的功能性,并防止逻辑的切换。爱特的闪存 FPGA可提供Flash*Freeze模式,较系统级频率门控更具弹性,可以控制输入/输出状态并终止频率。

RTL级的频率门控也是普遍使用的省电技巧,共有基于 latch以及没有latch的两种类型。但在运用时必须注意频率偏移(skew),以及启用信号可能造成的额外异常信号(glitch)。我们通常会建议使用基于latch 频率门控来消除AND门输出端可能产生的额外异常信号。

此外,大部分基于闪存的 FPGA组件中都有一个以上的PLL,来作为分频、倍频、移相等操作,这些PLL也都会消耗额外的电源。对功耗敏感的应用来说,应尽可能避免使用PLL。举例来说,若需要分频,可以用一个除法器取代PLL,来产生新的频率频率。若一定要用PLL,则必须尽量将各种PLL的组合予以优化,以降低PLL输出的最大频率。同时,基于闪存的 FPGA中的PLL有一Power-Down 输入接脚,当不需要的时候,可以利用此输入来关闭 PLL和频率网络。

结论

当采用FPGA进行具严苛功耗要求的应用时,系统架构师和设计团队应该明确了解终端系统的操作模式以及电源分布状态。再透过对FPGA架构的认识、嵌入式功能方块、电源相关特性,如电源模式、各种操作电压等,设计人员才有可能安排适当的设计技巧,来满足电源预算的要求。

对系统架构师来说,我们建议的设计方法论为:取得终端系统的操作模式与系统电源分布。分析系统分别处于闲置、睡眠、关闭模式的时间比例、 On/Off频率、以及操作的任务周期。若是On/Off频率高,则须注意易失性FPGA可能会有突波和配置电流的问题。若是任务周期占操作的比例不高,且大部分的时间是处于闲置或睡眠状态,重点就应该放在降低静态电源。但若任务周期在所有模式下都很平均,那么处理静态和动态电源就一样重要。最后,如果系统大部分都处于操作状态,那么FPGA的动态电源设计就更为重要。

责任编辑:gt

-

FPGA的特殊电源有哪些要求?2012-02-24 0

-

FPGA使用的电源类型有哪些?2012-02-24 0

-

为了满足FPGA的电源要求2018-12-03 0

-

FPGA的电源要求是什么?2018-12-03 0

-

如何利用FPGA满足电信应用中的降低功耗要求?2019-07-31 0

-

如何才能确保电源系统符合FPGA要求?2021-04-08 0

-

FPGA能否满足便携式存储应用的低功耗要求?2021-04-29 0

-

怎么实现基于FPGA的动态可重构系统设计?2021-05-10 0

-

采用赛灵思7系列FPGA满足严格的功耗预算2018-06-05 3294

-

台式电源满足最新的能效要求2022-08-15 307

-

Xilinx FPGA的电源设计和实现方案2022-10-17 3298

-

Spartan-7 FPGA满足对成本敏感的市场要求2023-09-13 79

全部0条评论

快来发表一下你的评论吧 !