基于并行数据处理改进算法在FPGA中实现

可编程逻辑

描述

1、引言

在信号处理过程中,我们通常将模拟信号转化为数字信号进行处理或传输。原始数据用取样的方法进行采集,通过A/D转换将模拟信号变成数字信号。但是这样的数字信号由于码位多,在传输过程中占用带宽多,传输率也低。为了提高传输效率,必须对原始数据进行量化处理。在实际运用中通常采用非均匀量化。采用输入信号幅度和量化输出数据之间定义了两种对应关系,一种是在北美日本使用的 律;另一种是在欧洲中国大陆使用的A律。A律压缩重要运用于数字电话通讯中的语音压缩编码,如何实现快速压缩已成为实际应用的关键。随着VLSI(超大规模集成电路)特别是FPGA技术的日益成熟,基于FPGA的各种压缩编码的实现显示出其独特的优势和广泛的应用前景。本文针对13折线来的算法特点,提出一种并行数据处理且适合于实现编码流水线作业的改进算法,运用VHDL语言将其在FPGA中实现,借助Quartus II 6.0平台对其进行验证、仿真,并对仿真结果进行分析,评估了系统的性能,证实了该算法的优越性和高效性。

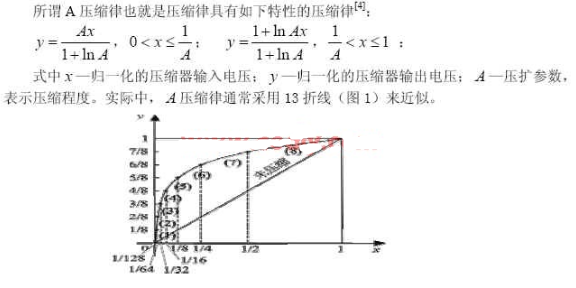

2、原理

图1 13折线示意图

3、编码流水线算法设计思路

本设计从适合流水线操作的角度对常规算法作了改进,前级完成相应位计算后将其结果传递到下一级,完成后进入下一组数据的编码运算,从而达到流水作业的目的。由于每个模块功能独立,适合模块化设计。

3.1极性码C1

表示输入信号抽样值处于8个

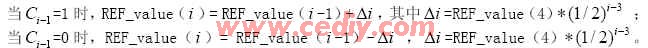

4、具体实现

图2 系统框图

图2系统框图中实现了一种并行数据处理且适合于编码流水线作业的改进算法,并采用FPGA具体实现。系统主要由状态机(state)和比较单元(compare)这二部分组成,其中Comp1,Comp2,……Comp7这七个单元模块在状态机的控制下并行进行流水线数据处理。即在状态机的控制下,在一个clk时钟脉冲当中,七个单元同时进行着数据的处理工作,处理完成后,前一个Comp单元的输出作为后一个Comp单元输入,在下一个clk时钟脉冲到来时紧接着又进行下一组数据处理。按照这种方式,依次处理下去,从而达到流水线作业的目的。下面对该系统进行具体实现。

4.1状态机(state)

为了使comp模块间有序进行工作,确保之间数据正确稳定的传输,特引入状态机对各模块进行数据读、写控制。

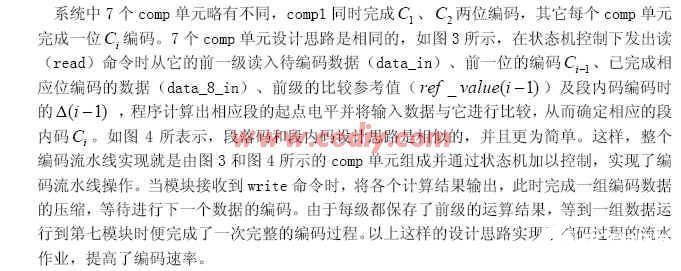

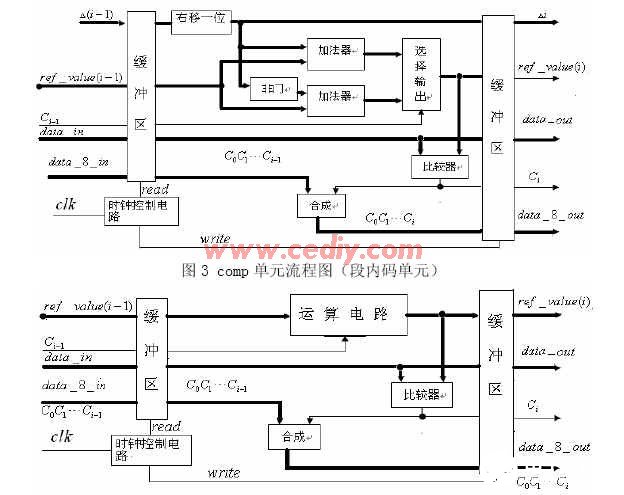

4.2比较单元(compare)

图4 comp 单元流程图(段落码单元)

5、验证结果

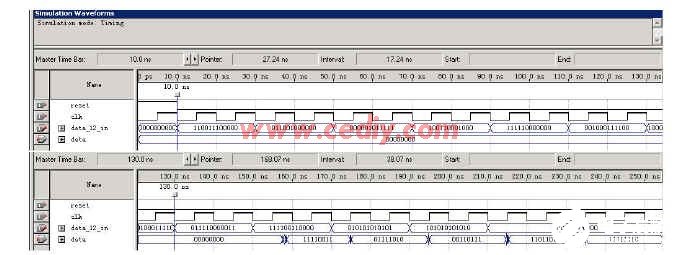

本文设计算法在quartusII 6.0开发平台上,选用cyclone家族芯片对设计进行了功能、时序验证[6],时序结果如下(图5):

图5 时序仿真结果图

从图5中可以看出,在clk=100MHz时钟下,在第一个数据+1248(110011100000)输入后,经过14个时钟周期,输出相应的带极性的8位编码为11110011,再第14个时钟周期之后,随后每两个时钟周期完成一组数据的压缩编码。这样就实现了编码的流水线作业,提高了数据处理效率。经过对数据的核对验证,证明了数据运算的正确性,达到预计设计效果。

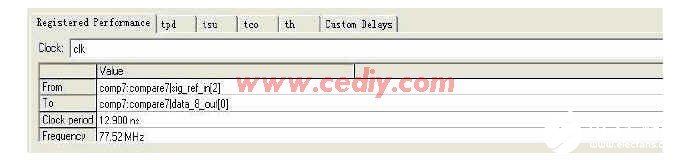

对系统进行运行速率评估,确定瓶颈通道如下图6

图6 时序分析图

从图5时序仿真图可以知道,每两个时钟完成一组编码,这是由于每个模块完成数据处理需要读写两个时钟。从图6可以看出,信号处理的最大时间消耗发生在comp7模块内,耗时12.900ns,这意味着整个模块的最大时间消耗为12.900ns。即有2T=12.900ns,计算出T=6.450ns,得出系统的最大时钟频率 Fmax=155.04MHz,最快编码速率为77.52Mbyte/s。

6、结束语

在实际语音通讯中,由于语音采样速率相对比较低,一般编码速率通常为64Kbit/s,在A律压缩编码中,使用本文提出的并行数据处理算法,应用VHDL实现了编码的流水线操作,最快编码速率为77.52Mbyte/s。因此,在多路信号采集中使用该算法可以极大的提高系统的工作效率。

本文创新点:本设计从适合流水线操作的角度对常规算法作了改进,实现了流水线操作算法在FPGA上快速A律压缩编码的设计与验证。

责任编辑:gt

-

基于改进的CORDIC算法的FFT复乘及其FPGA实现2011-07-11 0

-

高速专用GFP处理器的FPGA实现2012-08-11 0

-

fpga设计中双口RAM在雷达数据处理上的应用2012-08-11 0

-

触摸屏数据处理算法研究及实现2012-08-15 0

-

DSP怎么在进行数据处理的同时进行串口通信2014-02-24 0

-

Verilog并行数据处理问题2017-11-10 0

-

FFT 算法的一种 FPGA 实现2017-11-21 0

-

VHDL 基于FPGA的高速数据处理系统设计思路2020-08-31 0

-

FPGA的高速数据处理系统结构和硬件设计2020-09-04 0

-

怎么解决人工神经网络并行数据处理的问题2021-05-06 0

-

STM32 USART串口是如何进行数据处理的呢2021-11-25 0

-

在FPGA体系结构能够实现的并行运算2021-12-15 0

-

基于模糊关联规则并行挖掘算法的飞行数据处理2009-12-30 452

-

Spark的并行数据挖掘的研究2017-12-30 514

-

如何使用FPGA实现嵌入式多核处理器及SUSAN算法并行化2021-02-03 680

全部0条评论

快来发表一下你的评论吧 !