基于FPGA器件实现高速采集系统的设计

可编程逻辑

描述

1、 引言

在雷达、气象、地震预报、航空航天、通信等领域里,现场信号具有重要的作用,这些信号的主要特点是实时性强,数据速率高,数据量大,处理复杂,运算量大。因此,高速数据采集的研究一直是工程实践中一项倍受人关注的领域。目前由于数字信号的快速发展,对信号采集的要求也不断的提高,特别是在参数方面的要求越来越高,如精度、速度、采样通道数等。鉴于此,本文会介绍一种基于FPGA来控制高速A/D转换器AD9432实现高速采集,从而满足在系统中的应用。

2、 系统结构

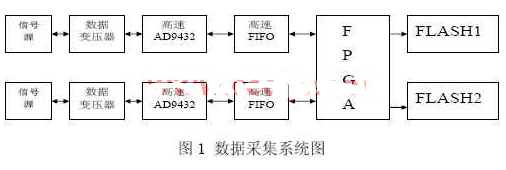

系统对输入的两路模拟信号采样率为60MHz,每路1K的采样周期(前100微秒进行采样,后900微秒进行数据转换,放入FLASH中),量化精度为12bit。转换后的数据经过FPGA的控制送到乒乓FLASH中。再以140Mbps的数据率平稳输出,利用FPGA对数据进行帧结构处理,最后经数据采集卡送入电脑中通过软件进行显示。数据采集系统的结构如图1所示。

3 、硬件设计

常用的高速多通道数据采集的设计方案有两种:

(1)以单片机MCU为控制核心,控制多通道数据采集与处理。因为单片机本身指令周期及处理速度的影响,同时随着程序量的增加,如果程序的健壮性不理想的话,可能会出现“程序跑飞”和“复位”现象。因此对于高速多通道数据采集,普通单片机很难满足系统对数据采集实时性和同步性的要求。

(2)以FPGA作为数据采集的控制核心,实现多通道模拟信号的采集和处理。由于FPGA采集采样控制、处理、缓存、传输控制、通讯于一个芯片内,编程配置灵活,开发周期短,系统简单,具有高集成度、体积小、低功耗、高速、I/O端口多、在线系统编程等优点,尤其在只需要简单数据处理的情况下,FPGA能够提供比专用高速DSP更好的解决方案,并且特别适用于对时序有严格要求的高速多通道数据采集系统。

针对雷达实时监测系统对实时性和同步性的要求,选择第二种方案设计高速多通道数据采集系统。

本设计中采取了高速模数转换器AD9432+高速FIFO+大规模可编程逻辑器件FPGA+FLASH存储芯片的方案。根据之前相关系统的经验,此方案的可实现性高,系统可靠性大。关键器件的选择目的如下:

1.高速AD转换器的选择

信号采集的核心是模数转换技术。模数转换包括采样、保持、量化和编程四个过程采样就是将一个连续变化的信号X(t)转换成时间上离散的采样信号X(n)。

由于本系统时钟频率为60MHz,分辨率要求又较高,所以积分型、顺次逼近型、闪烁型无法使用本次设计,在本次设计中采用了ADI公司生产的AD9432模数转换器。它是单片、12位精度、采用带有误差校正逻辑的多级差分流水结构的、105Msps高速模数转换器,片内集成高性能的采样保持放大器和参考电压源。同时,AD9432还具有较低的功耗(850mw)和较高的信噪比(66dB)。

2.固态存储介质的选择

可作为固态记录器件的半导体件有多种,其中主要包括SRAM,DRAM,FRAM,FLASH等几种器件;其中SRAM和DRAM为易失型(断电后数据不能保持),FRAM和FLASH为非易失型(断电后数据能保持)。由于DRAM和FLASH两种器件的特速工艺结构,能实现较高的位密度,因而得到广泛应用。

SRAM和DRAM均为易失型器件,需要一个后备电池提供连续的电源,同时,它们的电源功耗相当大。在EEPROM的基础上发展起来的闪烁(Flash)PROM,解决了上诉问题。FLASH为非易失型器件,当断电后,数据仍保持在FLASH存储芯片中,因而不需要后备电源,同时它的功耗非常低。由于半导体技术的迅速发展,FLASH存储芯片的密度不断提高,容量越来越大,所以本设计采用了SAMSUNG公司生产的K9F1G08U0M型FLASH。

3、可编程逻辑器件的选择

本系统采用了Xilinx公司生产的XC2S100E型FPGA。

XC2S50E是Spartan-IIE系列产品中的一款,它采用了1.8V的内核电压,系统性能可达到200MHz,具有50000个系统门,CLB数量为16×24,LC数量1728,BlockRAM容量32Kbit,拥有182个I/O。由于这款FPGA采用了低内核电压,这将从根本上减小芯片功耗,从而解决高速工作状态下发热量大的问题。同时其丰富的门阵列资料,也为复杂控制逻辑的实现提供了可能。

3.1 ADC转换以及控制

根据上述采样要求,ADC转换芯片选用ADC公司的AD9432,在使用AD9432时,本设计采取了以下方法:

1.高速采集工作中,为满足抗干扰性强,传输数率快,电平稳定,采用外接ECL差分芯片来提供差分时钟;

2.为满足对直流精度和温度漂移的要求,采用外接基准电压源的形式;

3.为满足对信号输入抗电磁干扰及信号放大采样输入端前加变压器;

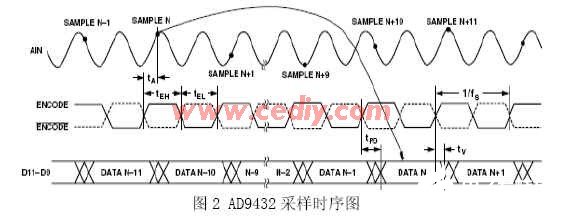

4.从图2中可以看出,由于AD9432采用多级差分流水结构,其在每个时钟周期的上升沿捕获一个采样值,10个周期以后才可以输出转换结果,可以看出输出管道延迟10个采样周期,因此采样时钟脉冲的个数必须比采样点数至少多10个才能保证采样的正确。

由于通道数有2路,因此直接取其数字量的高12bit先分别送入高速FIFO中,再送入FPGA中,利用FPGA内部的资源生成锁存器进行两路数据的合并,这样提高了集成度,可以减少外围的器件数量。设定两路锁存器的时钟相差1800,这样可以实时地把输入的数据转换为顺次输入的数据。

3.2 ADC控制时序说明

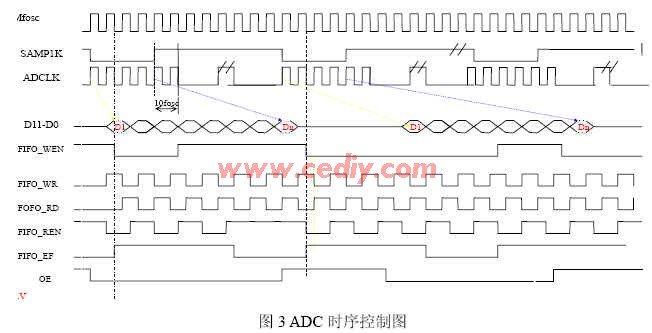

采集信号启动,开始采集数据,在60MHz频率下工作,如图3。

因为两路是对称的,所以两路控制AD是同时进行,时序一致。由于ADC的输出延时,启动ADC采集后,延迟10个fosc,送出FIFO的写时钟WCLK和写使能信号/WEN,把AD采集的数据送到FIFO中。在每个fosc的上升沿检查FIFO的/EF引脚,若/EF=‘1’,说明FIFO不空,就启动对FIFO的读操作,否则,对FIFO的读操作无效。由FPGA送出FIFO的读时钟信号RCLK和读使能信号/REN,把FIFO中的12位数据读出,进入FPGA片内进行乒乓FLASH数据处理。

3.3 乒乓FLASH的结构及读写控制

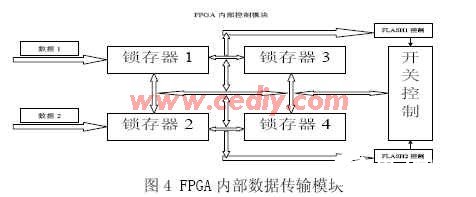

由于需要同时输入和不间断输出数据,且数据量较大,因此选用乒乓FLASH来保证采样和传输同时进行。乒乓传输部分包括两个开关控制(FPGA中实现)以及两块高速FLASH,如图4。

部数据传输模块

将在FPGA中已经合并的数据再分为两路,流向由锁存器控制,当门控信号控制FLASH1时,FLASH1则进行数据写入,锁存器1打开,锁存器2成高阻状态;与此同时,FLASH2进行数据读出,锁存器3成高阻状态,锁存器4打开。当满足切换的条件后,切换到FLASH2写入而FLASH1读出的模式,如此循环。

为了使各个通道的数据排列在同一个数据区、读出时更加容易操作,我们将同一个通道的数据放在一片FLASH,即在1/60MHz的时间内,写入FLASH的地址不变,其中两片FLSAH的片选信号CS交替有效,而读出FLASH中只有一片FLASH的CS有效。这样,更具FLASH的容量大小及读取速度,在一个0.4s的时间段中,正好读出一片FLASH的数据就是一个通道数据,而下一个0.4s的时间段中,正好读出的一片FLASH的数据就是一个通道的数据,而下一个中读出的就是另一个通道的数据。

4 、抗干扰硬件设计

由于本系统的数据传输率比原有的设备提高了几倍,达到120Mbps,此时电路板将面临噪声和干扰问题。本系统采用了一下抗干扰措施。

1.高速数据采集系统把系统的电源分成模拟和数字两部分,把系统的地分成模拟地和数字地,正确使用两者之间的单点接地或多点接地,尽量用真个平面作为地平面。

2.在电源接入PCB板和板上每对电源和地之间加上滤波和去耦电路,能够更好地消除有电源引起的噪声。系统将数字电源和模拟电源分开供电,以免快速变换的数字信号干扰模拟信号。

3.去耦电容有两个作用:一方面是本集成电路的蓄能电容,提供和吸收该集成电路开门关门瞬间的充放电能;另一方面旁路掉该器件的高频噪声;

4.时钟产生器尽量靠近到用该时钟的器件,时钟线要尽量短;

5.布线的方式尽量采用菊链法的方式,这种结构便于阻抗匹配;

6.印制板尽量使用45度折线而不用90度折线布线,以减小高频信号对外的发射与耦合;

7.任何信号都不要形成环路,如不可避免,必须让环路区尽量小;

8.用大容量的钽电容而不是电解电容作电路充放电能储电容,而使用电解电容须在每个电容边上加一个小的高频旁路电容。

5、 实验验证

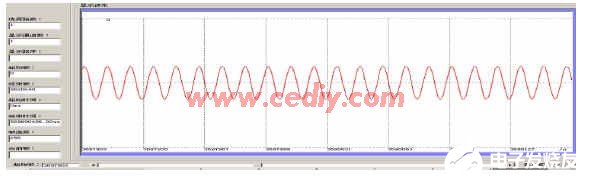

通过上述方案,进行了硬件实现,图5显示了该设计的高速采集系统对50Hz的正弦波形采集,并对采集后的波形实现了波形再现,该图所显示的波形符合采集前设定的波形,充分说明了该系统的可行性。

6、 结束语

高速数据采集系统的关键技术体现在合理的设计结构和对干扰的有效抑制,本文对这两方面进行了充分的考虑,接下来利用FPGA组织方式灵活的特点,根据实际情况设计合理的结构满足同步实时高速数据采集系统的要求,因此,本文所介绍的是一种不失一般性的数据采集解决方案。

本文作者创新点:1.以AD9432为核心的高速数据采集系统,最高采样率能达到60MB/S;

2.利用FPGA编程设计乒乓FLASH结构;

责任编辑:gt

-

如何利用FPGA实现高速连续数据采集系统设计?2021-04-08 0

-

怎么实现一种基于FPGA高速数据采集系统中的输入输出接口?2021-04-29 0

-

基于FPGA的高速多路数据采集系统的设计2009-12-19 471

-

基于DSP和FPGA的CCD图像采集系统设计与实现2011-02-25 1124

-

高速数据采集系统中的FPGA的设计2016-05-10 606

-

基于FPGA的高速数据采集硬件系统设计2016-05-10 787

-

基于FPGA的高速数据采集系统接口设计2016-05-10 796

-

基于FPGA的高速数据采集系统的设计2016-05-10 736

-

基于FPGA的高速数据采集系统设计_杨江涛2016-05-17 748

-

基于FPGA的多通道高速CMOS图像采集系统2016-08-30 527

-

基于FPGA的高速图像采集系统的研究与设计2016-08-30 505

-

基于FPGA的高速AD采集卡设计2017-08-30 1238

-

如何使用FPGA和DSP进行高速数据采集系统设计2018-11-07 983

-

如何使用FPGA设计高速实时数据采集存储系统的资料概述2018-12-10 959

全部0条评论

快来发表一下你的评论吧 !