使用CPLD器件和VHDL语言实现USB收发模块的硬件功能设计

可编程逻辑

描述

引 言

当前,高密度可编程逻辑器件CPLD,由于具有巨大的灵活性而广泛应用于状态机、同步、译码、解码、计数、总线接口、串并转换等很多方面,而且在信号处理领域的应用也活跃起来。通用串行总线(USB,Universal Serial Bus)接口既是一种快速、双向、廉价、可以进行热插拔的串行接口技术,也是一种体系完备的通信协议,已逐渐成为计算机的主流接口。USB接口的收发模块用于进行数据编码和与外部相连。本文主要介绍使用CPLD实现通用串行总线(USB)接口收发模块。

1、USB收发模块的数据规范和通信协议

1.1 USB的数据编码方式

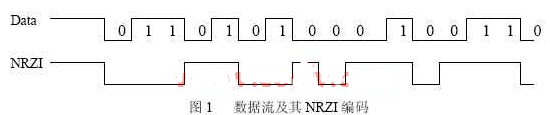

USB系统在进行串行数据传输时,使用一种NRZI(None Return Zero Invert ,即不归零反向码)的编码方案。在该编码方案中,“1”表示电平不变,“0”表示电平改变。图1

给出了一个数据流和它的NRZI编码。

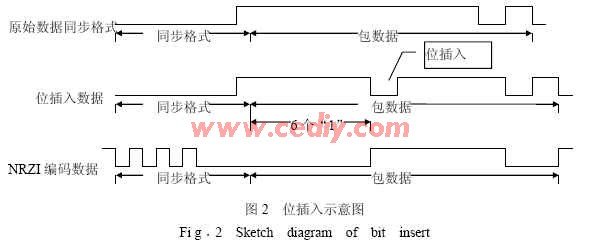

如果直接使用这样的编码方式会遇到一个很严重的问题:若重复相同的“1”信号持续进入时,就会使电平长时间无法转换,逐渐积累从而导致读取数据产生严重的脱节。为了确保信号发送的准确性,当在USB总线上发送一个数据包时,传输设备就要进行位插入操作。所谓位插入操作是指在数据被编码前,在数据流中每6个连续的“1”后面插入一个“0”,从而强迫NRZI码发生变化。

位插入操作如图2所示。USB数据的传送是由低位到高位。每包数据的开始是一个同步格式,同步格式固定为80H。从同步格式开始,位插入操作贯穿于整个数据传输过程,在同步格式后的数据“1”作为真正数据流的第一位。位插入操作是由传输端强制执行的。

1.2 USB收发模块工作过程

USB收发模块的发送单元由串行化﹑位插入﹑NRZI编码等几部分组成;接收单元由NRZI解码﹑反位插入﹑并行化等组成。整个收发单元的工作过程如下:发送端在数据发送前,首先要将并行数据串行化,然后进行位插入,最后进行NRZI编码;接收端在接收数据前就必须先执行NRZI解码,然后进行反位插入,最后进行串行数据并行化。

2、USB收发模块的设计流程

使用VHDL语言进行USB收发模块的设计采用自下而上的设计方法,即先设计其各部分功能单元,再编写顶层文件调用各功能单元以实现其总体功能。根据USB收发模块的工作过程可以确定其设计流程。下面以发送模块为例,介绍各模块的具体实现。

2.1 串行化部分的设计

USB收发模块传输的数据都是串行数据,一个串行数据由10位组成:1位启动位,8位数据位,1位停止位。由于系统内部处理的都是并行数据,所以在发送之前应该进行并行数据串行化处理。串行化的过程是将输入的并行数据按由低位到高位的顺序存入一个有序数组中,并按串行数据格式进行编码。根据这一原理可以编写VHDL程序实现串行化功能。

2.2 位插入部分的设计

在位插入部分的设计中,最关键的步骤是计数器的设置和使用。位插入的进行与否由计数器的值决定,而计数器的值则由输入串行数据的状态直接决定。由于只有在连续输入6个“1”之后,即计数器的值为6时才进行一次位插入,而在计满6个数之前,只要有一位输入的串行数据为“0”,则计数器立即清零。因此,在每读入一位数据之后,就要判断其是否为“1”,以决定计数器加一还是清零。正是由于计数器状态极易发生改变,所以增加了编程的复杂性。

2.3 NRZI编码部分的设计

NRZI编码的原理如前所述。

2.4 数据传输控制方式

为了能对数据位进行准确的操作,选取每位数据包含4个时钟周期(CLK)。例如低速1.5Mbit/s的工作时钟应选取为6MHz 。在串行数据发送控制器中设置了一个2位的时钟计数器,利用该计数器高位的状态来产生数据发送时钟(TXCLK),在每个发送时钟的上升沿发送一位数据。串行数据发送过程的波形如图3所示。

最后,在完成各功能单元设计的情况下,编写顶层文件调用各个功能单元,以实现USB收发模块的整体功能。在顶层文件中设置了外部输入和输出端口,作为信号和数据进出发送模块的端口;同时还定义了许多不同的中间变量和信号,用以将各个功能单元连接起来,从而实现数据和信号从输入到输出的连续工作过程。

3、USB收发模块的部分VHDL源代码

下面针对串行数据的NRZI编码,给出USB收发模块的部分VHDL程序源代码:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY NRZI IS

PORT (EN : IN STD_LOGIC;

IND1 : IN STD_LOGIC_VECTOR(7 DOWNTO 0);

OUT1 : OUT STD_LOGIC_VECTOR(8DOWNTO 0));

END NRZI;

ARCHITECTURE behav OF NRZI IS

BEGIN

PROCESS(EN)

BEGIN

IF EN =‘1’ THEN OUT1(0) 《= ‘1’;

IF IND1(0)=‘1’ THEN OUT1(1) 《=OUT1(0);

ELSIF IND1(0)=‘0’ THEN OUT1(1) 《= NOT(OUT1(0));

END IF;

END IF;

IF IND1(1)=‘1’ THEN OUT1(2) 《=OUT1(1);

ELSIF IND1(1)=‘0’ THEN OUT1(2) 《= NOT(OUT1(1));

END IF;

END IF;

… … …

IF IND1(7)=‘1’ THEN OUT1(8) 《=OUT1(7);

ELSIF IND1(7)=‘0’ THEN OUT1(8) 《= NOT(OUT1(7));

END IF;

END IF;

END IF;

END PROCESS;

END behav;

在能够体现模块功能的前提下,该程序中的输入与输出均设置为八位串行数据,但输出起始位设置为

“1”,实际输出为九位。在实际使用中输入与输出数据均有可能超出八位,但也只是增加了编程的复杂性,其设计方法并不发生改变。

4、仿真结果

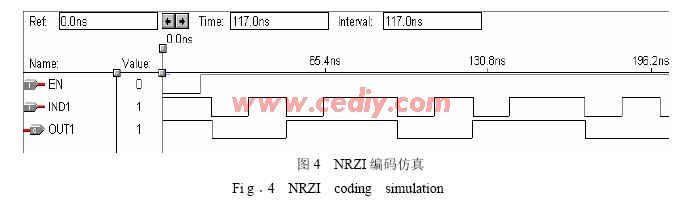

USB收发模块串行数据NRZI编码单元的VHDL源代码通过MAXPLUSⅡ软件仿真[4]后的波形如图4所示。

由图4所示的仿真波形,当使能端EN=‘1’时,电路才开始工作,输入数据和输出数据的起始位都为‘1’。将仿真波形中的输入数据IND1和输出波形OUT1与图1所示的NRZI编码原理波形相比,发现仿真波形符合NRZI编码原理,即说明此VHDL源程序完全符合设计要求。其余各个功能单元的VHDL源代码也可用相同的方法进行仿真,将仿真所得结果与理论推导结果相比较可知各程序符合设计要求。

5、收发模块的硬件实现

在完成源程序的设计和仿真之后,可以选用可编程逻辑器件来具体实现USB收发模块的硬件功能。本设计选用Altera公司MAX3000A系列可编程逻辑器件中的EPM3032A芯片。EPM3032A的集成度为600可用门 ﹑32个宏单元﹑34个可用I/O引脚,外加电压为3.3V。这些基于EEPROM器件的组合传输延迟快至4.5ns。以上述发送模块为例,定义输入引脚为:时钟CLK,使能端EN,8位输入IN0~IN7。定义输出引脚为 :串行数据输出端口OUT。将程序下载至芯片中,即可实现该设计的硬件功能。

6、结束语

USB收发模块是USB接口的重要组成部分,传统的设计方法是使用现有的芯片组合为硬件电路。这种开发方法要受到现有芯片可实现功能的制约,开发时间长,电路调试复杂,设计修改困难,易产生资源浪费。

本文作者创新点:采用VHDL语言作为设计工具,结合相应的CPLD器件来实现USB收发模块的硬件功能,大大地缩短了设计周期,提高了设计的可靠性、灵活性,弥补了传统设计方法的不足。

责任编辑:gt

-

基于CPLD和FPGA的VHDL语言电路优化设计2019-06-18 0

-

如何用VHDL语言实现帧同步的设计?2021-04-08 0

-

如何使用VHDL硬件描述语言实现的十六路彩灯控制系统?2021-04-19 0

-

怎么利用CPLD器件及VDHL语言实现电梯控制系统?2021-04-29 0

-

如何利用FPGA和VHDL语言实现PCM码的解调?2021-05-07 0

-

用VHDL语言实现3分频电路2007-08-21 5554

-

采用CPLD/FPGA的VHDL语言电路优化原理设计2010-03-19 2350

-

基于CPLD的VHDL语言数字钟(含秒表)设计2011-09-27 2524

-

FM收音机的解码及控制器VHDL语言实现2016-06-07 748

-

关于通过FPGA中VHDL语言实现ALU的功能设计详解2018-07-22 7041

-

基于VHDL硬件描述语言实现CPSK调制的程序及仿真2021-01-19 552

-

使用VHDL硬件描述语言实现基带信号的MASK调制的程序与仿真2021-01-19 582

-

使用VHDL硬件描述语言实现基带信号的MFSK调制的程序与仿真2021-01-19 625

-

如何使用VHDL硬件描述语言实现基带信号的MPSK调制2021-01-19 654

-

基于VHDL语言实现远程防盗报警设计2023-11-08 103

全部0条评论

快来发表一下你的评论吧 !