奈奎斯特升余弦数字滤波器的工作原理和采用FPGA器件实现设计

可编程逻辑

描述

1 引 言

随着信息需求量的增大,网络都逐渐朝着综合化、宽带化方向发展。数据速率的提高,对于数字信号处理的速度和质量的要求也越来越高。

在数字基带传输系统中,为使基带数据传输获得足够小的误码率,必须使码间干扰和噪声的综合影响最小。奈奎斯特第一准则指出了要消除码间干扰,系统从发送滤波器经信道到接收滤波器总的传输特性所应满足的条件。根据这一传输特性,实际系统一般采用具有升余弦滚降特性的滤波器作为发送滤波器。在第三代移动通信中,信号的码片速率高,频谱旁瓣大,在传输时容易产生邻道干扰,影响系统容量。如果在发送前,采用奈奎斯特(Nyquist)FIR滤波器将数字基带信号进行成形滤波,压缩旁瓣,可以大大减小干扰的影响,从而降低误码率。因此,滤波器的设计在通信系统中占有重要的地位,它的性能将直接影响整个通信系统的性能指标。本文在对滤波器进行研究的基础上,利用窗函数设计了一种奈奎斯特升余弦数字滤波器,并用硬件语言编程进行了FPGA实现。

2工作原理及结构

在数字信号传输过程中,我们只要求特定时刻的波形幅值如何无失真的传送,而不必要整个波形无失真。奈奎斯特第一准则,又称第一无失真条件告诉我们:如果信号经传输后整个波形发生了变化,但只要其特定点的抽样值保持不变,那么用再次抽样的方法,仍然可以准确无误得恢复原始信码。我们可以求出满足奈奎斯特准则的成形滤波器,在实际中得到广泛应用的是幅度频率响应具有奇对称升余弦形状过渡带的一类滤波器,通常称之为升余弦滤波器。

为了减小或消除码间干扰的影响,滤波器的传输特性的过渡带应设计成具有升余弦滚降特性即设计成奈奎斯特FIR成形滤波器。具有升余弦滚降特性的滤波器传输函数为:

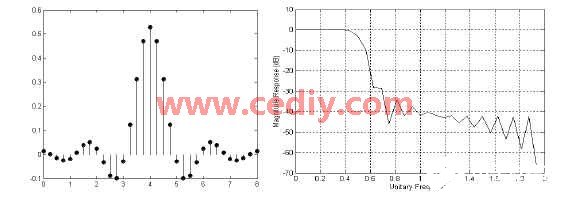

取滚降系数α=0.22,则取样频率根据上式可知应大于2.44倍输入码片速率,我们取为4,取FIR滤波器的有限长度N为33,调用Matlab中的库函数rcosfir可以得到其频域和时域分析图:

根据Matlab的分析结果,阻带最小衰减为33.983085dB,满足设计要求。由于存在量化误差,需要把量化前后的频率响应对比,看量化后的频谱特性是否满足设计指标,从而决定量化的比特数,同时也可能要求对滤波器的阶数调整。在满足频谱要求的前提下尽可能的减小量化比特数和滤波器的阶数,以方便设计的实现。成形滤波器如果选用直接型需要33次乘法和30次加法,利用了平方根升余弦滚降滤波器的系数对称性,选择分布式算法,可以减少大约一半的乘法运算,则使33次乘法减少为16次,总的运算量大大减小。

3 FPGA实现及结构说明

3.1 FPGA总体结构

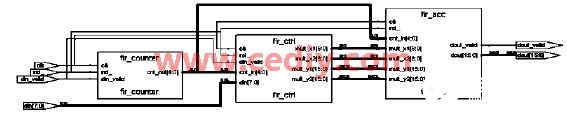

要设计的滤波器为33阶FIR根升余旋滤波器,假设输入取样数据速率为3.84M,滤波器的主时钟只要能够达到76.8M,便能够使每个数据在滤波器里面的计算时间为20个时钟周期,这样做主要是考虑到要使乘法器的使用个数减少(本设计中使用了2个乘法器),提高乘法器的使用效率。由于在滤波器的实现过程中,有大量的乘、加运算,所以为了达到较高的时钟频率,必须在运算的过程中使用流水线方法。

利用分布式算法,所设计的滤波器划分成了三个主要的模块,如下图所示。其中,fir_counter模块主要完成一个计数的功能,输出的计数结果控制另外两个模块的运行;fir_ctrl完成输入数据移位以及送入乘法器的数据的选择;fir_acc则完成乘累加功能并输出最后的结果。

计数模块:计数器输出总线宽度为5bits,数据大小为0~31,在没有din_valid(输入有效信号)信号的情况下,计数器输出会从0到31重复输出

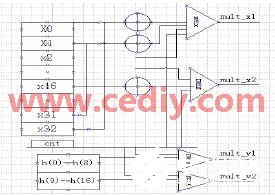

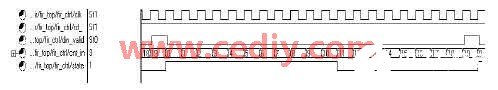

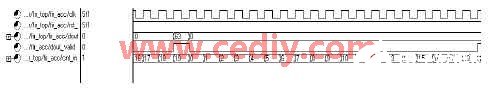

从下面的仿真图中也可以看出,计数器在din_valid信号控制下的计数过程。 数据控制模块:该模块完成的主要功能首先是将输入的数据保存在寄存器里面,进行移位,然后将所保存的33个最近输入数据对折相加,放到另外的寄存器里面。接着根据计数器结果,将相应的对折数据和滤波器抽头系数输出作为后面乘累加运算的输入数据。下面的硬件框图可以现实该部分的主要算法。

在代码的编写上,主要由一个状态机实现,分为Idle和Work两个状态,状态为Idle时,处于空闲状态,乘法器输出为0,当din_valid信号为“1”时,触发状态机进行跳转,Idle-》Work ,同时将滤波器输入数据存入寄存器并进行移位。进入Work状态后,根据计数信号的值进行各种选择运算。

从下面的仿真图中可以看出状态机随输入有效信号信号和计数信号变化而发生的跳转。其中,状态(state)为高电平时表示状态Work,为低电平则表示状态Idle。

乘累加模块:该模块主要功能是完成mult_x1与mult_y1以及mult_x2与mult_y2的乘操作以后把两个乘法器的输出送入累加器,完成循环累加工作。控制该部分的主要关键是一个计数器和一个输出有效信号,每20个时钟输出一次数据。具体计数过程和输出有效控制如下:

3.2 仿真验证

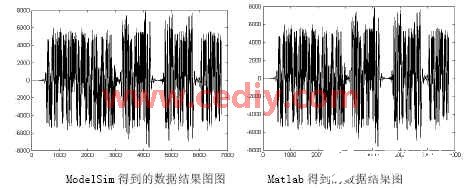

所使用的仿真工具为ModelSim,上面的波形截图便是来自ModelSim的wave窗口。我们用同样的输入数据,分别用ModelSim和Matlab进行仿真,将仿真结果进行比较,得到几乎相同的结果。(由于输入的滤波数据为随机产生的数据,所以得到的结果没有什么规律性可言。)

4 结 论

利用窗函数设计FIR滤波器的原则是:一是选择主瓣较宽的窗函数,从而加大阻带的衰减,保证通带的平稳,二是在保证阻带最小衰减指标的情况下,适当增加列长N值,使过度带窄一些。但N值的变化同时影响过度带和主瓣的变宽或变窄,另外选择主瓣较宽的窗函数时(同等N值下),其过度带就宽一些了,可见这两个设计原则是无法同时满足的,这一结论可从上面的设计示例中得到验证。因此设计FIR滤波器时,应根据技术指标,通过多次试验,找到合适的窗函数和N值 。本文作者的创新点是在原有的滤波器优化结构的理论基础之上对FIR滤波器的硬件模块进行的了设计,选取Verilog HDL语言进行硬件模块划分,分程序进行实现,同时选取尽量少的乘法器,尽可能的优化结构是关键,以达到节约成本简化工序的效果。

责任编辑:gt

-

什么是滚降系数?为什么要采用脉冲成形滤波器?2008-05-30 0

-

什么是平方根升余弦成形滤波器2008-05-30 0

-

IIR数字滤波器的Matlab和FPGA实现2012-08-20 0

-

fpga数字滤波器2013-03-30 0

-

数字滤波器的主要特点2017-05-25 0

-

基于FPGA的IIR数字滤波器的设计和实现方法介绍2019-07-08 0

-

LabVIEW如何实现数字滤波器的设计2019-07-26 0

-

如何采用级联结构在FPGA上实现IIR数字滤波器?2021-04-15 0

-

数字滤波器在FPGA中的实现2010-02-09 524

-

IIR数字滤波器设计-在FPGA上实现任意阶IIR数字滤波器2008-01-16 2312

-

基于FPGA的数字滤波器的设计与实现2010-01-07 3507

-

基于FPGA的FIR数字滤波器的优化设计2011-08-16 3663

-

如何使用FPGA实现IIR数字滤波器的设计2020-08-06 804

-

数字滤波器和模拟滤波器有哪些区别2023-06-27 1117

全部0条评论

快来发表一下你的评论吧 !