高速ADC的动态性能参数和基于DSP技术的测试方法研究

模拟技术

描述

高速ADC是信号处理机的不可欠缺的组成部分,其性能的好坏对信号处理系统的整体性能也至关重要。通常ADC的技术参数是由生产厂商提供,可作为设计的重要依据,但是在电路板上形成的ADC模块的性能如何,还与ADC的周边电路或输入信号密切相关,比如参考电压源、取样时钟、输入运算放大器以及电源,地线和信号线上的干扰等。因此有必要在线评估高速ADC模块的动态性能,分析其对信号处理机系统性能的影响。本文介绍了一种在信号处理机实际设备上在线评估高速ADC模块的动态性能的的方法。该方法利用信号处理机本身的数据采集能力,通过在模拟输入端增加标准测试信号,经过AD转换后,由信号处理机的DSP读入转换结果,通过DSP仿真系统将数据读入PC机,然后利用MATLAB软件对数据进行频谱分析,最终计算出SNR,SENAD等几项动态参数。本文还给出了具体测试结果及其分析,并对高速ADC模块设计给出了一些意见。

一、高速ADC的动态性能参数

评估ADC动态性能的主要参数定义如下:

1、信噪比(dB)

其中Asignal为满幅度正弦模拟输入信号的均方根值,Anoise为所有噪声源之和的均方根。

2、信噪失真比(SINAD)

其中AHarmonic为各次谐波(除直流外)的频率分量的均方根之和。

3、有效比特位数(ENOB)

其中N是转换电路的量化比特位数,A测量误差下为测量噪声平均值,A测量误差为量化误差平均值。

4、总谐波失真其中,AF_IN为输入信号基波的均方根值,AHD_2下至AHD_N为采样所得信号频域中2次到N次谐波分量的均方根值。

5、无杂散动态范围其中,AF_IN为输入信号基波分量的均方根值,AHD_MAX为采样波形频谱中最大失真谐波分量或最大杂散信号的均方根值。

通过这些参数的定义,可以看出高速ADC电路的大部分动态参数能在频域上表现出来;所以对高速ADC电路进行频域的测试可以获得相应的动态性能参数。

二、传统的测试方法

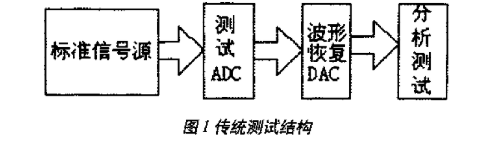

传统测试中,利用一个精度比被测模数转换电路精度高2位以上的DAC产生一个单频正弦波作为被测模数转换电路的测试信号,在被测电路的后端也接一个DAC将波形恢复。如图1。

这种测试结构简单,直观。但是在工程实践中为了评估模数电路必须增加一块DAC电路,会与实际模块连接困难和引入DAC的误差。因此在线评估不好采用。

三、基于DSP技术的测试方法

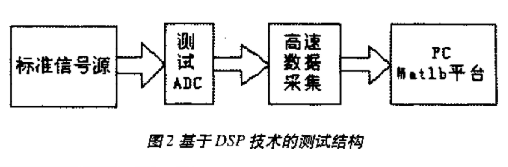

利用DSP技术可构成简便且准确的测试结构,在ADC电路的后端利用数字信号处理器将输出数据采集保存起来,然后利用DSP仿真设备的JTAG接口将数据传送到PC机中,利用Matlab软件进行相关频域处理,以获得高速模数转换电路的实际转换特性参数。结构如图2所示。

在这里用基于DSP的频域分析工具替代了模拟的测试仪表,可以提供更高精度及可重复观察的测试结果。将数据采集到PC机中后,在Matlab这一平台中将时域的离散信号波形通过DFT(FFT)算法转换到频域。在频域中根据定义求出相关的动态性能参数。在输入信号没有失真的理想情况下,输入模拟量为正弦波时,输出频谱应为频率等于输入频率的冲激函数图形。事实上,ADC的量化误差,转换器内部各种噪声,甚至包括测试系统噪声,都会在频谱图上噪声背景中体现出来。基于FFT信号分析的基本函数就是FFT本身和功率谱。FFT 算法中假设离散时间序列可以精确地在整个时域进行周期延拓,所有包含该离散时间序列的信号为周期函数,周期与时间序列的长度相关。然而如果时间序列的长度不是信号周期的整数倍,即,就会发生频谱泄漏。这里是输入信号频率;Fsample是采样频率;Nwndows窗函数长度;Nrecord采样信号数据长度。在测试中一般选用采用汉宁(Hanning)窗函数,以减少频谱泄漏。

求出采样输出信号的频谱后,要得到相关测试参数值还得确定信号基频及各次谐波的位置。下面给出频率分量及其镜像的关系如图3所示。设Fo为位于奈奎斯特区间(DC~Fs/2)的一个频率。又令Fk为频带中Fo的镜像,又称Fo为的第k次镜像。

图3 频率分量及其镜像分量关系示意图

所有镜像间的关系可如下表示:

从上面的关系可看出,对于奇偶次镜像分量而言,都能在奈奎斯特区间内找到它们对应的频率分量,也就是说对于任意的超出奈奎斯特区间的谐波分量都可以在奈奎斯特区间内找到其镜像分量。如果,谐波位于奈奎斯特区间内,可直接计算得到谐波位置;要是谐波超出奈奎斯特区间,则要估计上面的镜像方法来获得谐波的数据。

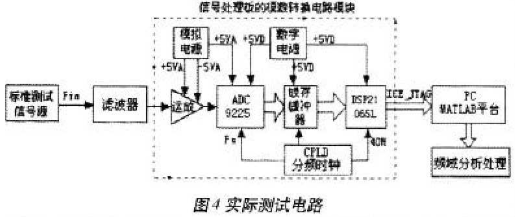

四、基于信号处理机的ADC模块测试

我们对信号处理机的电路板的高速ADC模块进行了在线测试。图4中虚框所包围的部分是信号处理机的模数转换电路。DSP21065L将采集到的数据存储在内部存储区中,采集完毕后通过DSP仿真系统的JTAG接口将数据传送到PC中,最后在Matlab中进行相关的数字信号处理,根据处理结果对转换电路的转换性能做相应的评估分析。根据所获得的模数转换电路的性能指标,可以分析转换电路对信号处理机的影响。

图中AD转换芯片AD9225为12位精度,最高转换速率为25MSPS,芯片内部带有采样保持电路和参考电压源。基本性能如下:

lSNR71dB(finput=2.5MHz)

lSINAD 70.7dB(finput=2.5MHz)

lTHD –82Db(finput=2.5MHz)

精度INL:DNL:

4.1部分测试数据

测试信号为满幅度正弦波,每次采样8192点数据,做8192点FFT,得到采样数据频谱。在不同的采样频率和信号频率下,分别做5次实验,取平均值。

4.2 测试数据分析

12位精度的转换电路,其理论信噪比应达74dB,而实际测试中只有60~70dB。说明有除量化噪声之外的别的噪声源。实验中发现如将转换电路中的模拟电源和数字电源采用同一电源供电,则信噪比要比二者分别供电时减少大约5~6dB。改善接地的状况也能有效的提高转换动态性能,例如,在接地情况不佳的情况下5MHz采样1.54MHz时的信噪比只有59.7dB,而在改善接地状况后提高到了61.64dB,提高了1.94dB。实验数据显示谐波失真较为严重,我们分析主要原因是信号源纯度偏低。测试的结果接近AD9225技术手册给出的参数,这说明了该方法的可信度。从SNR值来看,由于测试针对整个高速模数转换电路,得到的结果反映的是整个电路的动态转换特性。由于各辅助电路的影响,使得转换电路的性能低于器件手册给出的参数。根据测试结果分析,对高速模数转换电路的设计提出下列参考意见:

l转换器件后端与数据总线间采用数据所锁存器进行隔离驱动,以减少后端数据总线上的噪声串入模拟电路,降低转换性能。

l模拟电源和数字电源应作隔离处理,以减少模拟端的噪声。

l选用合适的运放减少谐波失真。

l模拟输入信号线应尽量宽,减少信号失真。

l器件选型时。所选器件的转换精度应高于所需精度要求的2个以上有效位数。

l所选ADC芯片的转换速率应大大高于取样的速度。

五、小结

本文介绍的对信号处理机高速ADC模块动态性能在线评估方法具有简单,可信度高,便于工程上采用的特点。对信号处理机系统性能的评估与分析都有很好的参考价值。

责任编辑:gt

-

高速公路GPS车辆动态监控技术研究2009-04-16 0

-

高速 ADC/DAC 测试原理及测试方法2018-04-03 0

-

请问有什么更好更简便的方法来测量ADC的静态参数?2018-08-24 0

-

怎么测试高速ADC的性能?2021-04-14 0

-

汽车的主要结构参数和性能参数相关资料分享2021-08-30 0

-

ADC有哪些性能参数2021-09-28 0

-

ADC的性能参数及优缺点2021-12-20 0

-

影响锌锰电池电性能参数检测的因素有哪些?2009-10-28 1739

-

基于DSP的汽油机点火参数自动测试系统2011-02-25 829

-

氮化硅陶瓷球材料性能参数测试2018-03-20 914

-

高速ADC测试和评估方法2021-09-16 666

-

高速ADC、DAC测试原理及测试方法2021-09-16 1230

-

blog高速ADC、DAC测试原理及测试方法2021-09-17 740

-

定义和测试高速ADC中的动态参数2023-02-25 1209

-

高速ADC的动态测试2023-02-25 1832

全部0条评论

快来发表一下你的评论吧 !