基于TMS320DM642 DSP芯片实现多功能视频处理系统的设计

处理器/DSP

描述

1、 引言

视频采集系统在航天、工业等领域大量存在,随着多媒体技术的快速发展.对视频采集及处理技术系统的性能提出更高的要求,如高采集速度、低功耗、信号连续平滑、延时小、实时性及扩展性等。TI公司推出的TMS320DM642器件很好地解决了上述问题,其丰富的外围接口及专用的视频处理模块使得其非常适合日益发展的视频处理系统。这里,提出了以TMS320DM642为核心,由解码器TVP5150为视频输入解码处理器,与非门Flash为存储器、LXT971为网络传输器组成的集视频采集、压缩、存储、网络传输于一体的多功能视频处理系统。

2、系统硬件设计

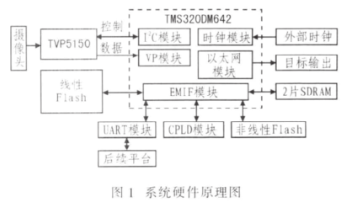

图1出系统硬件原理图。TMS320DM642器件具有强大的处理能力和丰富的外部设备接口。满足各种不同应用环境的控制与图像输出的需要。TMS320DM642在600 MHz的时钟主频下,数字处理能力可达到4 800MI/s,内部具有256 K字节的二级缓存结构:TMS320DM642具有4个可配置的视频接口(VP0~VP3),能提供与通用视频编解码器等数据流的无缝连接,支持ITU—BT.656等多个视频标准;并具有多通道音频接口(McASP)、10/100 Mb/s以太网介质接入控制器(EMAC),以适应网络和多媒体的需要,其片内64位的EMIF(Eixtemal Memoryr Interface)接口可以与SDRAM、Flash等存储器件无缝连接,极大方便大量数据的搬移。

多功能视频处理系统中CCD摄像头将采集到的PAL制式的图像信号通过视频解码器TVP5150转换成8 bit的ITUBT.656格式的数字视频信号,同时将相应的同步信息,比如行、场同步信号等,打包成内嵌同步头信号送入TMS320DM642的VP0接口模块.再通过TMS320DM642的内部集成外设将分离后的数字视频信号通过EDMA送入SDRAM中,由DSP直接处理。TMS320DM642的CLOCK使用50 MHz的外部时钟网络和12倍的片内锁相环倍频系数,将DSP的主频配置为600 MHz。由于视频采集系统的数据存储量大,计算复杂。系统在TMS320DM642的CEO空间通过EMIFA接口外扩了2片SDRAM存储器,频率为133 MHz,由外部ECLKIN外接PLL(Phase Locked Loop)产生133 MHz时钟,使系统的SDRAM存储空间达到32 MB。

TMS320DM642的Boot为EMIFA方式,系统在CEl空间外扩了一片Flash AM29LV320存储器作为程序存储器,当TMS320DM642上电或复位启动时,自动从AM29LV320上加载程序代码。另外系统在CEl空间外扩了一片NAND FlashK9 K8G08130M用来存储处理后的视频数据。同时系统采用Ahera公司的CPLD EPM3064ATCl00,管理系统内的控制信号,包括测试信号、复位信号、使能及中断信号、同步控制信号等,以及对TMS32013M642的部分地址空间的管理,CPLD还预留了部分引脚用于系统功能的扩展。同时TMS320DM642内部集成了以太网控制器外设,在外部只需外扩PHY物理层器件LXT971就可为系统构建一条100 Mb/s的高速以太网接口,使系统具有了网络传输的功能。

3、主要模块数据处理

3.1 TMS320DM642数据处理模块的工作流程

TMS320DM642的工作流程如图2所示。上电后,首先初始化DSP的CSL库函数,然后初始化PLL、GPIO及相关中断寄存器,等待中断信号的来临。采集模块中CPLD控制A/D转换器写FIF0,FIF0半满时,通过HF信号通知CPLD,CPLD对TMS320DM642产生一个中断信号,通知DSP将读取的一帧图像数据读入到内存(SDRAM)中,DSP处理过的数据写入DSP内软FIF0,判断写外部接口满足条件后,软FIFO内数据可通过以太网,串口等接口输出。视频信号经解码器转换成数字信号传送到DSP的专用数字视频接口。DSP将采集的信号放到一个临时的缓冲空间里,缓冲空间满后,触发中断。DSP接收到中断后将缓冲空间里的数据放到图像缓存(SDRAM)中。DSP处理数据后,将处理后的数据写入图像输出缓存(SDRAM)。如果写外部接口条件满足,DSP即将处理后的数据从输出缓存中读出,然后经以太网或串口输出。

3.2 视频采集数据处理

视频解码器TVP5150通过TMS320DM642的I2C总线设置其内部寄存器等。通过8位的并行数据线将采集到的视频数据传到TMS320DM642的video port口。TMS320DM642的片内视频端口(VP0、VPl、VP2、VP3)可用作视频捕获端口、视频显示端口、视频流传输端口。每个视频在捕获模式或显示模式时可采用8/10位分辨率的ITU—R BT.656的YUV 4:2:2格式,或者作为一个Y/C 16/20位视频通道,以YCbCr4:2:2格式的Y和Cb/Cr分离的形式输入输出。在系统中VP0口作为视频捕获端口,选用8位ITU-R BT656捕获模式(内嵌式同步信号)。配置好TVP5150后,把DSP的相应采集输入口也配置成ITU—R BT.656的输入格式,然后再设置好EDMA通道并使能相关的中断,DSP里面的EDMA会将视频口输入的亮度Y,还有红差CR、蓝差CB的数据自动分开存到TMS320DM642的内部RAM里,从而达到获取视频数据流的目的。

4 、系统测试

在焊接电路板时先焊接电源部分,待电源部分有稳定的电压输出后再焊接电路板上的其他部分,进行调试并测试驱动程序。当TMS320DM642与SDRAM、Flash、CPLD焊接完毕后,下载完成CPLD程序,然后将电路板连接仿真器及PC机,上电后启动CCS(Code Composer Studio)代码编辑与集成环境,如果能正常启动并运行,则表示测试通道已经建立。TMS320DM642工作正常。

通过I2C总线配置视频解码器TVP5150的内部寄存器.系统调试中I2C的时序测试如图3所示。图3中的曲线分别为时钟总线和数据总线。当数据总线为低时,从时钟总线下降沿开始传输数据,图4给出I2C数据传输原理,通过比较图4和图3,测试结果显示,时钟线与数据线传输正常,可正确配置各器件内部寄存器。

当系统的核心TMS320DM642工作正常后,即可调试系统各个外设模块的调试。视频输入模块是本系统的主要功能,一旦I2C工作正常,通过下载相关视频程序到板子中,通过CCS使用View一》Graph一》Image操作显示图像。从而验证视频输入模块及相关器件的工作情况。图5则验证系统工作正常。

5、结语

采用TMS320DM642处理器设计的切实可行的视频采集存储系统,测试效果良好,性能稳定,达到预期设计目标。多功能频视处理系统具有广阔的应用前景,可广泛应用于智能安防,机器人工业检测和其他需要嵌入式图像信息处理的自动化领域。

责任编辑:gt

-

基于TMS320DM642的MPEG-4编码软件优化设计2009-08-27 333

-

TMS320DM642视频图像处理双路应用主板2008-12-01 0

-

TMS320DM6422016-12-05 0

-

如何利用TMS320DM642设计一个具备网络传输功能的多路图像监控系统?2021-06-07 0

-

怎么实现基于TMS320DM642视频采集驱动开发?2021-06-08 0

-

怎么实现基于TMS320 DM642的多路视频处理系统设计?2021-06-08 0

-

基于TMS320DM642的视频采集驱动程序的怎么实现?2021-06-08 0

-

TMS320DM642 pdf datasheet2008-08-07 834

-

基于DM642的视频处理系统设计2009-06-16 423

-

基于TMS320DM642的视频处理系统中I2C总线的应用2010-08-05 476

-

基于TMS320DM642的视频采集卡设计2010-12-03 1006

-

基于TMS320DM642的CCD图像采集系统设计2010-12-13 1635

-

如何从进行TMS320DM642到TMS320DM6467的迁移2018-04-18 1023

-

基于TMS320DM642视频采集驱动开发2019-02-03 376

-

基于TMS320DM642多媒体芯片实现视频监控系统的应用方案2021-03-17 2896

全部0条评论

快来发表一下你的评论吧 !