采用SOPC技术和VHDL语言实现图像增强处理系统的应用方案

可编程逻辑

描述

引言

图像增强最早起源于人类的空间探索计划。从卫星或飞船上获得的关于地球和太阳系中行星的图像因为多种原因而降质,这些原因如成像设备受使用环境的限制,相机和对象的相对运动,相机机械振动,飞行器的跳动和翻转等等,获取图像的代价十分昂贵,图像的降质造成科学意义上的损失也是巨大的。因此由降质图像获得清晰图像的努力是非常有意义的。图像增强技术是通过采取适当的增强处理使原来模糊不清甚至根本无法分辨的原始图片处理成清楚、明晰的富含大量有用信息的可用图像。因此,增强处理技术在医学、遥感、微生物、以及军事等领域得到了广泛应用。

图像增强一般采用软件或硬件处理的方法。软件处理主要通过计算机来实现复杂、高精度的图像处理算法,这种方法具有灵活、方便、精度高等优点;但是采用软件处理的方法速度上会受限,在对系统实时性要求高的场合往往不能满足要求,比如航天或微波遥感领域,需要实时观测处理信息,及时发出相应的控制指令,这种条件下,软件处理是无法满足要求的。因为软件处理的这种局限性,采用高速的DSP或FPGA来实现实时图像处理显得尤为迫切。DSP是专用的信号处理芯片,它内部硬件集成了许多专为信号处理而设计的部件,比如ADI公司的TigerSHARC系列芯片,它的内部有位反序部件,很容易实现FFT(快速傅立叶变换),因此,DSP被广泛应用于图像处理领域。但是,由于技术壁垒的原因,航天领域很难

得到航天级别的芯片,因此在一些关键的应用系统中,我们则采用FPGA来实现实时图像处理。同时,FPGA以其高的处理速度、灵活的控制及接口能力,广泛应用于实时图像处理领域。现在的FPGA芯片一般都集成了DSP内核,这对图像处理带来了方便。针对这种情况,本文提出一种基于FPGA实现的SOPC,用于完成图像的增强处理。

1、像对比度增强算法原理

图像增强的方法一般分为两类:空间域和频域。本文则采用了空间域的方法。空间域方法主要利用某一准则来实现图像灰度值映射,从而调整图像灰度的动态范围,进而实现图像对比度增强。这种方法可以描述为:

2、设计思路

在实际情况中,我们关心的是图像的目标,对背景不太关注。由式(1)可知,在空间域中,图像对比度增强处理可以理解为按照某一准则对图像像素点灰度值进行映射。按照式(2),采用分段灰度变化,对目标和背景分别采用不同的变换准则,对图像中的不同灰度信息进行灵活处理。

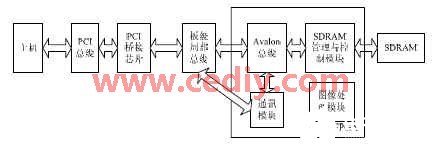

设计采用了PCI总线以32位传送数据,速度较快,PCI桥接芯片用于连接PCI总线与板级局部总线。SOPC内部逻辑模块之间的连接关系由Avalon总线建立。在板级局部总线与Avalon总线之间建立通信模块,使主机可以通过PCI总线、板级局部总线和Avalon总线对SOPC组件进行访问与控制。SDRAM用于存储处理前、后的图像数据。图像处理模块在有处理数据的任务或已经处理完毕时,与SDRAM管理与控制器进行交涉,获取SDRAM中的数据或把数据存入SDRAM。

3、系统结构及其功能实现

图1系统结构

3.1通讯模块

通讯模块负责板级局部总线与FPGA内部总线桥之间的通讯。由于SOPC内部各模块之间的逻辑连接由FPGA内部总线桥完成,因此通讯模块的建立可以允许用户从主机通过PCI总线和板级局部总线访问SOPC组件。该模块作为FPGA内部总线桥的一个主控接口,对总线桥上的其他从外设进行访问和控制。

3.2 SDRAM(同步动态存储器)管理与控制器模块

该模块的工作时钟独立于系统时钟,包括三部分设计如图2所示:SDRAM管理模块、控制器模块与SDRAM控制器。(1)SDRAM管理模块负责对存储图像数据的SDRAM存储空间做合理的分配,使待处理数据与处理后的数据分别放置在不同的存储单元,它作为FPGA内部总线桥流模式从外设,读写端口的数量可配置,这些读写端口可以以流传输模式把图像数据读出或写入SDRAM。(2)控制器模块作为FPGA内部总线桥的主控接口,负责SDRAM管理模块与SDRAM控制器之间的连接,并协调两者之间的访问。(3)SDRAM控制器负责对SDRAM的控制。

图2 SDRAM管理与控制器模块

3.3 图像对比度增强算法模块

常用的并行处理有两种最基本的连接模式:流水线连接和并行阵列连接。针对该算法,我们采用流水线连接,如图3 所示。在流水线结构中, 一个大任务被分解成复杂性大致相同的小任务, 各小任务在流水线上同时执行, 整个任务的速度取决于执行时间最长的子任务的执行时间。因而, 具有处理速度高的特点。在一个时钟触发信号到来时,进程1对图像数据进行存储,同时,进程2对图像数据进行处理;下一个时钟触发信号到来时,进程1存储的数据送入进程2进行处理,同时,进程1存储下一个输入数据。这样就实现了流水线操作,并可保证在一个时钟周期内完成一个像素点的计算。

图3 流水线结构

由于该算法逻辑模块是利用SOPC技术,能够在软件开发工具SOPC Builder中作为自定制模块调用,因此,需设置两个寄存器:帧有效计数寄存器和行有效计数寄存器,它们根据FPGA内部总线地址的不同,同时作为FPGA内部总线的读或写寄存器,从而使自定义模块可以和FPGA内部总线进行通讯。根据算法需求,采用VHDL语言对算法逻辑建模,并以FPGA内部总线从外设的方式在SOPC Builder 中调用。

4、图像增强处理系统的实现及测试结果

考虑到设计优化的方便性,本设计采用标准化硬件描述语言VHDL建立FPGA模块实现。对系统需求进行功能模块划分,按照自顶向下的设计方法生成各设计阶层,将设计任务分解为不同的功能元件,每个元件具有专门定义的输入输出端口并执行各自的逻辑功能。该SOPC设计通过以下步骤实现:

(1) 按照系统需求,采用Top-Down的方法进行部件划分。

(2) 各部件根据功能要求采用VHDL进行模块建立,并仿真综合优化。

(3) 利用SOPC Builder工具编译生成用户自定制模块。

(4) 调用已建立的IP模块并设置参数,配置生成片上系统。

(5) 在顶层VHDL文件中调用模块并示例化,进行信号连接。

(6) 对整个系统进行管脚等约束设置,全编译并进行行为和时序验证。

(7) 下载和硬件调试完成。

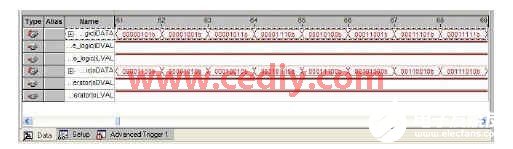

这里我们采用嵌入式逻辑分析仪Signal Tap II对设计中算法模块的信号节点进行测试,结果如图 4所示。

图 4测试结果

输入的图像数据宽度是8位。其中, iDVAL与iLVAL分别是图像处理算法模块的输入数据有效信号与行有效信号,由oDVAL与oLVAL驱动;iDATA与oDATA分别是原图像数据与处理后数据,在iDVAL与iLVAL同时置’1’时,原图像数据被读入图像处理模块进行处理。

5、实验结果及结论

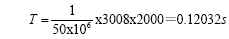

该设计对一幅大小为3008*2000的图像进行处理实验,图像增强前后如图5(a)、图5(b)所示。很明显,图5(b)在增强目标对比度的同时压制了背景,获得了很好的增强效果。这一点也可以从式(3)来判断,两幅图像的对比度函数值分别为37dB和43dB,在本系统处理后的图像对比度增强了5dB。在SOPC系统时钟为50MHz时,每一帧的处理时间为

而在Pentium 4、CPU 3GHz、256MB内存的PC上通过Matlab用代码实现则需0.9850s。该设计采用FPGA实现图像实时处理,与利用软件处理图像的方法比较起来,有明显的速度优势。基于FPGA设计方法灵活实现图像的实时处理,是今后图像处理发展的一个方向,尤其是在大数据量处理和高速实时处理要求较高的场合。

本文作者创新点:提出了一种基于FPGA的SOPC,该SOPC快速完成图像增强处理,满足实时图像处理的要求;同时,系统构成灵活,可根据图像增强处理算法需求,对设计中模块的可重复开发。

责任编辑:gt

-

单片FPGA图像预处理系统的设计与实现2009-09-19 0

-

基于DSP的图像处理系统的应用研究2012-12-19 0

-

浅谈大数据视频图像处理系统技术2013-09-24 0

-

基于FPGA的图像边缘检测系统设计,用VHDL语言实现该怎么做?2018-05-10 0

-

SoPC技术在图像采集和处理系统中的应用设计2018-10-31 0

-

FPGA实时视频图像处理系统的原理是什么?2019-08-22 0

-

使用 ARM 和 CPLD 共同实现嵌入式数字图像处理系统2019-12-10 0

-

如何用VHDL语言实现帧同步的设计?2021-04-08 0

-

FPGA技术如何用VHDL语言实现8位RISC微处理器?2021-04-13 0

-

怎么实现基于SOPC的运动视觉处理系统的设计?2021-06-04 0

-

基于SOPC的通用图像处理系统设计2011-05-24 428

-

高速图像处理系统中DDR2-SDRAM接口的设计2011-07-23 5139

-

基于SOPC的运动视觉处理系统的设计与实现2018-12-02 293

-

基于SOPC技术实现的语音处理系统的设计方法2023-10-26 60

-

基于VHDL语言实现远程防盗报警设计2023-11-08 99

全部0条评论

快来发表一下你的评论吧 !