采用编程逻辑器件控制8个LED小灯电路的设计

可编程逻辑

描述

1、引言

演化硬件(EHW)是指能根据外部环境变化自动改变自身结构和功能的一类硬件,它把可编程逻辑器件的结构位串当作染色体,通过演化算法进行搜索,用符合要求的染色体配置可编程逻辑器件,得到要设计的硬件电路。这一研究方法能够探索新颖的电路设计方案,寻找许多未被人类发现高效的捷径;实现电路的在线自适应与容错,以适应很多应用需求对硬件的灵活性要求。它正在成为未来电路设计的发展方向。

本文进行了数字电路的演化实验,目的是在FPGA中演化出8个LED小灯的控制电路,使其实现根据时钟脉冲从1到8号按顺序依次闪亮的功能。以验证硬件演化的有效性,探索数字电路演化设计的基本方法。

2、染色体编码

用3个二进制位代表1个小灯的点亮次序,这样染色体长度为3×8=24位。三个二进制位的值为0表示在第一个时钟时点亮的小灯,以此类推, 值为7表示最后点亮的小灯,允许有多个小灯同时点亮。

适应度分为二部分,其百位表示将染色体从小到大排序后与目标相符的小灯的个数,最大为8;十位和个位表示排序所需的次数,理想顺序为01234567,其交换次数为0,最差情况为76543210,需要交换28次,所以最大适应度为828。图1给出了一个染色体的例子,排序后共有6个小灯符合目标,其中没有值4和6,有3个5,这表示在时钟5和7时没有小灯点亮,而在时钟6时5、6、7号三个小灯都点亮。排序共进行了14次,此染色体的适应度为6×100+28-14=614。

染色体: 111 101 001 011 000 010 101 101

排序后: 000 001 010 011 101 101 101 111

3、演化算法

采用了Hereboy算法,这是一个类似模拟退火算法的优化算法,它不像标准遗传算法那样对群体中选择的个体进行交叉、变异,而是通过单个个体的变异来探索搜索空间。

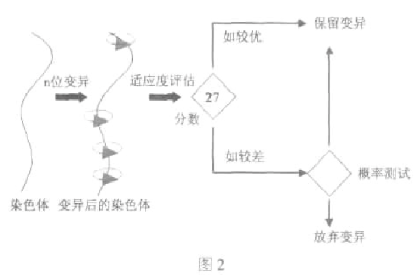

此算法需要用户来确定二个参数:变异率和搜索率。图2显示了算法的一个循环。算法根据变异率计算染色体中出现变异的位数,位置是随机选择的,把相应的位置反。然后对计算出染色体的适应度值,如果值比变异前高,就保留此变异,如果低,则染色体以一定概率(即搜索率)保留较差变异,否则恢复变异前的状态。保留较差变异的目的是允许它们与其它较好变异结合起来,加快收敛速度。然后此过程不断重复。

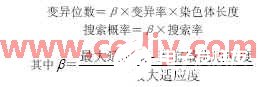

算法运行中采用了一个自适应方案逐步减少变异率和搜索率。如图3所示,它们在使用时被乘以一个系数β,染色体中变异的位数和接受一个较差变异的概率随着逐渐收敛到最优解而不断减小,这样开始时系统以较大步伐搜索,随着当前最优成绩的增加把变异速率调整的更精细。既能加快收敛速度,又防止了演化陷于局部最优。

4、实现

我们选择了XESS公司的XSV300开发板[4]作为实验的硬件平台,它以25针并口电缆与主机相连,通过一片XILINX公司的XC95108 CPLD来控制XCV300 FPGA的配置。板上的条状Led块由10个Led组成,选用其中的1到8号用于显示输出。

JBits2.8是一个Java类集合[5],它提供了对Xilinx Virtex系列FPGA位串的应用程序接口,既可对Xilinx设计工具产生的位串,也可对从实际硬件回读的位串进行操作。JBits使用的程序模型是一个二维CLB数组。每个CLB都有一个行、列号,使人们可以设置和检测选中的CLB内的所有可配置资源,在FPGA器件上设计并动态的修改电路。

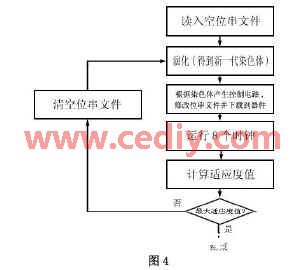

对本实验来说外部演化较为简单,只要将得到的最优染色体下载到器件中即可;内部演化则需要用硬件进行适应度计算,所以每一代的染色体都要下载到器件中,运行8个时钟,计算出其适应度值。图4给出了内部演化的基本流程。

我们采用了一种灵活的方法实现了从染色体产生控制电路,即根据染色体生成8个时钟周期Led灯的状态,共8×8bit等于64bit存入FPGA中的Bram,生成一个3位计数器,其输出连接到Bram的地址线,Bram的输出连接到Led条的输入。这样计数器在时钟的控制下从Bram中选择对应的数据输出到Led显示。而且在适应度测量时,不再需要专门的存储器来记录Led的状态,我们可以直接从Bram中读取电路的输出。

5、实验结果

我们在一台P4 1.7的主机上进行了外部演化实验,对Hereboy算法中变异率和探索率的不同取值对算法收敛速度的影响进行了统计,每对参数分别运行30次,计算出了其平均收敛代数和时间,如表1所示。

变异率 搜索率 平均收敛代数 平均收敛时间(ms) 最小收敛代数 最小收敛时间(ms)

当变异率大于0.7时,收敛速度急剧下降,且绝大部分次数无法演化出最优解。从表中可以看出,变异率和搜索率对演化的影响很大,随着它们数值的增大,演化的平均收敛速度也不断提高,在0.7左右时达到最优,但对最小收敛速度来说影响不大。由于外部演化完全通过软件计算,所以最小收敛代数和最小收敛时间与主机具体的运行状态有关,并不成线性比例关系。

在外部演化的基础上,我们成功的进行了内部演化。XCV300配置位串的长度为218980字节,完全配置下载时间约为50492ms,使用JBits的部分重配函数,在首次对XCV300进行完全配置后,每次只下载要修改的数据。此时部分位串的长度为23048字节,下载时间约为5358ms。将变异率和搜索率都设为0.7,在演化42715代,耗时60多小时后得到了目标电路。

6、结论

从实验可以看出,外部演化时间等于演化收敛时间加上完全配置下载时间,不过数分钟,而内部演化则需要数天。所以对小规模电路演化而言,内部演化受配置位串的下载速度的影响相对较大。如果采用标准遗传算法,每代需要计算适应度的染色体个数更多,内部演化将受到更大影响。对于复杂电路演化,如果其适应度计算时间远大于配置下载时间,此时方可发挥内部演化硬件执行速度快的威力,这有待于在今后的工作中进一步研究。

本文作者创新点:以JBits API和XESS开发板作为EHW平台,以Led控制器的演化为目标,实现了能够进行在线进化的闭环结构,形成了一个较为实用的EHW实验和应用环境的具体方法。

责任编辑:gt

-

什么是可编程逻辑2009-05-29 0

-

8位LED驱动电路AT9551资料推荐2021-04-14 0

-

怎么采用可编程逻辑器件设计数字系统?2021-04-29 0

-

PLD可编程逻辑器件2021-07-22 0

-

通过编程控制8个LED灯循环点亮2021-11-10 0

-

通过外部中断控制8个LED灯顺序点亮2021-12-02 0

-

LED灯有几种编程方法2021-12-02 0

-

采用STM32上一个GPIO口来控制对应的一个LED灯的点亮和熄灭2021-12-15 0

-

LED的驱动电路采用恒流源控制的原因2021-12-30 0

-

在FPGA开发板中点亮LED灯实现时序逻辑电路的设计2022-07-22 0

-

使用STM8S001J3构建一个可编程LED Police-Flasher设备2022-08-29 0

-

基于可编程逻辑器件的数字电路设计2009-11-16 1487

-

基于单片机和可编程逻辑器件实现LED显示屏2009-12-24 970

-

电可编程逻辑器件EPLD是如何设计的2022-08-22 986

-

什么叫可编程逻辑器件 可编程逻辑器件有哪些特征和优势?2023-09-14 1427

全部0条评论

快来发表一下你的评论吧 !