基于可编辑逻辑器件实现IEEE 802.11协议帧生成器的应用方案

可编程逻辑

描述

1、 引言

IEEE 802.11标准定义了能够统筹所有基于以太网的无线通信的协议。它是迄今为止最流行的无线局域网的标准。这个标准还细分了一些子标准, 如802.11a, 802.11b和802.11g。这其中有些协议可使用直接序列扩频技术(DSSS)来发送无线信号, 如802.11b。 无线局域网带宽窄,终端设备处理能力弱,其信号的组帧环节需要尽可能采用处理时延小,占用存储资源少的方法。本文正是以此为指导思想进行802.11协议帧的生成的。

2、模块的设计与实现

2.1 全局控制模块

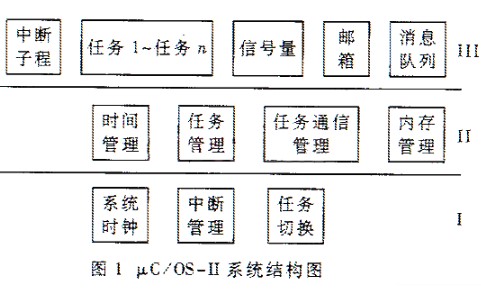

该模块的设计方法是采用一个9bit的计数器,以协议帧的二进制位长度为周期循环计数,在不同的时间片发出不同的使能信号,以实现对多个输出模块的控制,实现实时的串行输出。并设计有选通信号sel[1..0],以实现对输出端口的多路选择器的控制。其仿真时序波形图如图1所示。其关键代码如下:

①always@(posedge clk4) //初始化

begin

if(!reset)

begin

count《=0;

end else

begin

if(count==9‘d472) count《=0;

else count《=count+1;

end

end

②always//对帧序号生成模块的控制

begin

if(!reset) seqenable《=0;

if(count==9’d176) seqenable《=1;

if(count==9‘d192) seqenable《=0;

end ③always //对两个ROM单元的使能和禁止控制

begin

if(!reset)

begin

dataaddrenable《=0;

dataromenable《=0;

crccalenable《=0;

end

if(count==9’d240)//送data

begin

dataaddrenable《=1;

dataromenable《=1;

crccalenable《=1;

end

if(count==9‘d440)

begin

dataaddrenable《=0;

dataromenable《=0;

crccalenable《=0;

end

end

④always //在每帧结束时送出帧序号加1的使能信号

begin

if(!reset)contin《=0; if(count==9’d472) contin《=1; if(count==1)contin《=0;

end

⑤always //对CRC校验码生成模块的控制

begin

if(!reset)

crcdoutenable《=0;

if(count==9‘d440) //数据送完了。

crcdoutenable《=1;

if(count==9’d472)

crcdoutenable《=0;

end

⑥always//选通信号控制

begin

if(!reset) sel=2‘b00;

if(count==9’d470) sel=2‘b01;

if(count==9’d173) sel=2‘b00; 续⑥if(count==9’d190) sel=2‘b01;

if(count==9’d238) sel=2‘b10;

if(count==9’d438) sel=2‘b11;

end

endmodule

2.2 CRC校验码生成器模块

此模块需要的常用CRC生成多项式如下:

CRC-8:x8+x2+x+1

CRC-16:x16+x15+x2+1

CRC-32:x32+x26+x23+x22+x16+x12+x11+x10+x8+x7+x5+x4+x2+x+1

其关键代码如下。该模块CRC校验时序仿真波形如图2所示。

always@(negedge clk)//posedge把数据送出来,

//negedge对数据进行处理

begin

if(calculateen) //flag为高时作crc的产生

begin

dout《=1’bz;

D[0]《=din^D[31];

D[1]《=D[0]^din^D[31];

D[2]《=D[1]^din^D[31];

D[3]《=D[2];

D[4]《=D[3]^din^D[31];

D[5]《=D[4]^din^D[31];

D[6]《=D[5];

D[7]《=D[6]^din^D[31];

D[8]《=D[7]^din^D[31];

D[9]《=D[8];

D[10]《=D[9]^din^D[31];

D[11]《=D[10]^din^D[31];

D[12]《=D[11]^din^D[31];

for(i=12;i《=14;i=i+1)

D[i+1]《=D[i];

D[16]《=D[15]^din^D[31];

for(i=16;i《=20;i=i+1)

D[i+1]《=D[i];

D[22]《=D[21]^din^D[31];

D[23]《=D[22]^din^D[31];

D[24]《=D[23];

D[25]《=D[24];

D[26]《=D[25]^din^D[31];

for(i=26;i《=30;i=i+1)

D[i+1]《=D[i];

end

else dout《=1‘bz;

if(outputen)

begin

dout《=D[31];

D《=D《《1;

end

else

dout《=1’bz;

end

endmodule//

2.3 帧序号生成模块

该模块的功能是产生16bit的帧序号,由overall_ctrl在每帧结束时发出的contin信号实现计数的加一。由enable信号触发,将帧序号串行输出。其关键代码为:

①always@(negedge clk4) //产生帧序号

begin

if(!reset)

seqctrl[15:0]《=0;

if(contin)

begin

if(seqctrl[15:0]==16‘hffff)

seqctrl[15:0]《=0;

else seqctrl《=seqctrl+1;

end

end 续② 4’d3:q《=seqctrl[3];

4‘d4:q《=seqctrl[4];

4’d5:q《=seqctrl[5];

4‘d6:q《=seqctrl[6];

4’d7:q《=seqctrl[7];

4‘d8:q《=seqctrl[8];

4’d9:q《=seqctrl[9];

4‘d10:q《=seqctrl[10];

4’d11:q《=seqctrl[11];

4‘d12:q《=seqctrl[12];

4’d13:q《=seqctrl[13];

4‘d14:q《=seqctrl[14];

4’d15:q《=seqctrl[15];

endcase

end

else

begin

q《=1‘bz;

count《=0;

end

end

else q《=1’bz;

end

endmodule

②always@(negedge clk4) //16 bit帧序号串行输出

begin

if(enable)//enable信号只能严格划分为十六个周期;

begin

count《=count+1;

if(count!=16)

begin

case(count)

4‘d0:q《=seqctrl[0];

4’d1:q《=seqctrl[1];

4‘d2:q《=seqctrl[2];

该模块的帧序号生成模块时序仿真图如图3所示。

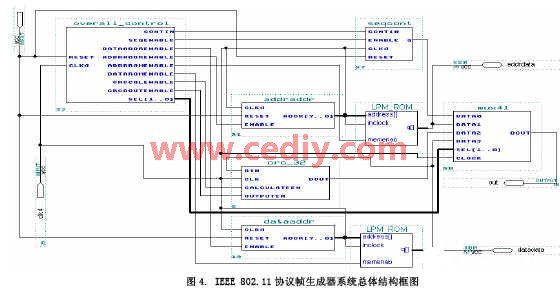

2.4 IEEE 802.11协议帧生成器 系统总体结构模块

IEEE 802.11协议帧生成器 系统总体结构模块框图如图4所示。

3. 结论

本文以展示详尽的Verilog HDL代码、各模块时序仿真图和系统总体结构框图的方式给出了一种基于FPGA的IEEE 802.11协议帧生成器的设计实现方法。该协议帧可直接由DSSS发射机发送。本设计几乎不产生组帧延迟,实时性能好,且不占用缓冲资源,具有新颖性和实用性。

本文作者创新点:

1) 本文给出了一种以FPGA为硬件平台的IEEE 802.11协议帧生成器的设计实现方法。

2)采用该方法几乎不产生组帧延迟,实时性能好,且不占用缓冲资源,具有新颖性和实用性。

责任编辑:gt

-

存储器接口生成器(MIG)解决方案2009-10-24 0

-

回声生成器2015-04-03 0

-

CDKEY生成器2016-07-08 0

-

如何去使用生成器呢2021-10-25 0

-

python生成器2022-02-24 0

-

pim卡资料生成器2007-11-22 551

-

UOC III系列器件 DMP生成器 (DMP Create2008-12-27 982

-

自制酸奶生成器2009-04-23 879

-

LED段码生成器2011-06-03 733

-

代码生成器的应用2016-01-14 739

-

一种自相似网络流量生成器的设计与实现2017-01-07 656

-

如何运行内存接口生成器GUI以生成RTL2018-11-23 4090

-

带你一起学习彻底搞懂Python生成器2019-02-25 2458

-

python生成器是什么2022-02-24 3065

-

通用RFID生成器2023-02-10 266

全部0条评论

快来发表一下你的评论吧 !