基于可编程逻辑器件CPLD实现中压变频系统的设计

可编程逻辑

描述

1、 引言:

中压变频系统要求产生与分配多路SPWM脉冲,控制实时性要求较高,应用软件功能复杂,另外还需要控制多路A/D、D/A转换以及与上位机进行串口通讯输出控制等外围器件工作,即使性能最好的单片DSP也难以满足要求,而片外专用处理器引脚I/O口有限,如果用多片DSP协同工作,都需要与DSP交换数据,这必然会大量消耗DSP时间资源,受高精度与实时性要求限制,很难满足要求。相反用CPLD(复杂可编程逻辑器件)进行I/O扩展,其设计乃至仿真调试都非常方便。

2、CPLD功能总体设计

变频控制器中核心器件由四部分组成,一个DSP、一个I/O扩展CPLD、一个核心CPLD、18个脉冲形成CPLD、6个故障诊断CPLD,如图所示。

其中DSP主要依据控制要求完成调节运算产生脉宽信号、频率信号和数据存取、数据传输、系统保护动作与报警功能,限于篇幅这里主要讲述脉冲形成CPLD的功能。

脉冲形成CPLD有3个功能:分别接受DSP分时段输出的脉宽信号与相位信号,产生SPWM脉冲;产生调制脉冲控制IGBT导通相位信号;经过调制后产生的脉冲信号分两路输出,一路按照三相分时传送到下层IGBT驱动CPLD,另一路将调制后的三相信号传送到故障诊断CPLD;封锁脉冲输出。

3、硬件选型设计

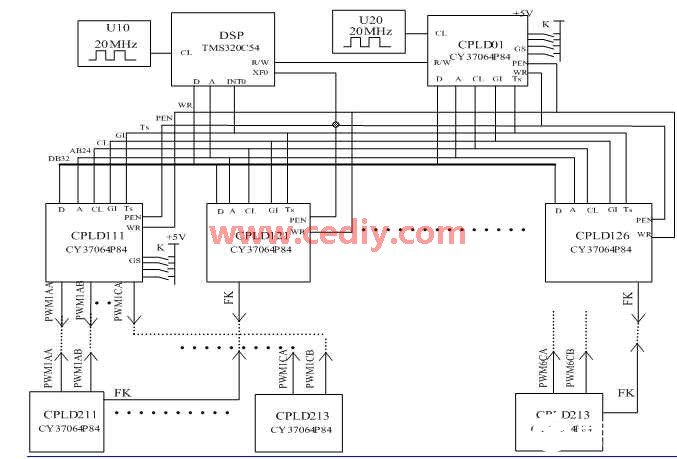

根据触发时序、脉冲分配与收发、设备故障诊断的要求,在硬件设计中选用本控制器CY37128P84 13片作为核心CPLD01、脉冲形成CPLD111—CPLD161、故障诊断CPLD121—CPLD126,18片CY37064P44作为的IGBT驱动CPLD201-CPLD218系列CPLD产品,该系列芯片内的组件门数高,电路信号延迟小,开发工具完备,可以容许多次重新擦除和烧录,可以协助完成电路的合成与仿真和自动对电路进行优化,缩短设计研发周期。硬件接线如下图所示:

图2 XK-GB06/3 中压变频控制器硬件接线图

其中,XRESET复位信号,AB作为地址线,DB为数据线,K为设备装置编址,GN为叠加脉冲串常数,GI为CPLD芯片选通信号,F20M时钟输入信号,EI0为Ts中断信号,EI1为故障中断信号,PWM1AA、PWM1AB分别为A相交流电前、后半周期触发脉冲,PWM1BA、PWM1BB分别为B相前后半周触发脉冲,PWM1CA、PWM1CB分别为C相交流电前、后半周期触发脉冲,WRP写脉宽控制信号,RDP 为读脉冲信号,FK是故障信号传输信道,XF0为脉冲封锁信号。

4、软件开发

本装置CPLD控制软件开发分为四部分,限于篇幅只介绍SPWM脉宽形成CPLD软件。

SPWM形成CPLD应用软件,共有四个流程,它们分别为加减法计数装载,脉宽数据装入,调制脉冲输出与封锁,以下为其主要程序流程。

Gi为组计数器,从2开始加计数,2、3、…N+1周期结束,重新开始一个新周期,组编号为Gs(1、……、Gn)

Gn组PWM输出,周期为Ts=2×Gn×Tn 总组设为Gn=6

当Ti减到0,下一个时钟的上升沿Ti重装为Tn,不间断循环减计数

设置一个半周期加计数器Tc,以便各组产生对称的PWM三角波

复位后Tc=1000B,避免第Gs组脉宽可逆计数器重装前,可逆计数器计数方向改变

设置循环条件:Ti=0 并且 Gi=2×Gs+1时,Tc置为00001B

如果 Ti=0,加1:

如果Tc=Gn 并且 Ti=0,第Gs组脉宽可逆计数器保持不变,使其由减计数器变成加计数器,Gi/2=Gs,Gs=0时,Gi=2×Gn 或 1,即Gi/2=Gn 或 0 第Gs组脉宽可逆计数器PWIA、PWIB、PWIC重装的条件为:Ti=0 并--且 Gi=2×Gs+1,第Gs组脉宽可逆计数器PWIA、PWIB、PWIC保持的条件为:Ti=0 并--且 Tc=Gn, 可逆计数器加/减计数的控制up_dn,up_dn=‘0’表示减计数,up_dn=‘1’为加法记数。

复位后up_dn=‘0’,

Ti=0 并且 Gi=2×Gs+1, up_dn清‘0’

Ti=0 并且 Tc=Gn ,up_dn置‘1’

如果 GS=b“000” 且GI(3 downto 1)=b“000” or GI(3 downto 1)=gn) 输出脉冲

否则 如果GI(3 downto 1)=GS 输出脉冲,GI(3 downto 1)《》GS禁止脉冲输出。

5、CPLD在高压变频控制器的应用

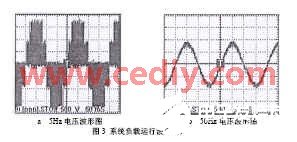

如下图所示,即在CPLD控制的电机负载下运行的电压波形。很明显在频率较低时,单元串联中压变频器输出电压波形的正弦性都不好,高次谐波丰富,而在频率升高时接近正弦波。通过实验证明,工作频率在5—50Hz间系统可以很好地稳定运行。

6、结论

可编程逻辑器件CPLD用于脉冲产生、分配、定时中断等协调工作,能够满足使用要求,经过单元串联中压变频器在实验室空载、负载运行的情况表明,软硬件方面都达到了设计要求,可以安全、稳定地长期运行。

本文作者创新点:

(1) 用CPLD产生PWM脉冲与对传输的脉冲数据链路进行故障诊断。

(2) 用CPLD作为DA转换、AD转换以及ST16552通讯芯片的控制器和扩展通讯端口。

责任编辑:gt

-

清华的可编程逻辑器件实验讲义cpld-2004-8-6-42012-08-16 0

-

可编程逻辑器件2014-04-15 0

-

可编程逻辑器件发展历史2019-02-26 0

-

专家都是如何使用超低功耗的复杂可编程逻辑器件(CPLD)的?2021-04-08 0

-

PLD可编程逻辑器件2021-07-22 0

-

可编程逻辑器件基础及应用实验指导书2010-03-24 569

-

什么是PLD(可编程逻辑器件)2009-06-20 16028

-

EDA技术与应用(可编程逻辑器件)2012-05-23 852

-

可编程逻辑器件FPGA/CPLD结构与应用2016-12-11 700

-

可编程逻辑器件(书皮)2022-07-10 359

-

FPGA CPLD可编程逻辑器件的在系统配置方法2021-09-18 660

-

电可编程逻辑器件EPLD是如何设计的2022-08-22 986

-

可编程逻辑器件的结构2023-03-24 839

-

可编程逻辑器件测试2023-06-06 441

全部0条评论

快来发表一下你的评论吧 !