采用数字信号处理芯片实现IIR数字滤波器的设计

处理器/DSP

描述

1 引言

近年来由于半导体技术、计算机技术的成熟与迅速发展,使得科技与生活的密切结合,尤其是数字信号处理的突飞猛进,以及许多组件得以数字化及一体化,提供了小型、多功能、低成本与低功率消耗的特性。由于数字信号先天上优于模拟信号,因此数字信号对噪声的免疫力远较模拟信号来得好,使得数字信号能长时间的保存或长距离的传输且比较不容易产生失真现象。数字信号处理(Digital Signal Processing DSP)在通信与信息系统、信号与信息系统、自动控制、雷达、军事、航空航天、医疗和家用电器等众多领域得到了广泛应用。本设计是基于数字信号处理的基础上,实现的IIR数字滤波,对于采集信号精度的提高,具有借鉴意义。

2 硬件系统介绍

2.1 系统框图

系统硬件框图如图2.1所示。主要由A/D转换、FPGA、存储器和D/A转换四部分组成。

2.2部分芯片介绍

一个电路的性能与元器件的选择是密切相关的,下面将从控制芯片、存储器、A/D转换和D/A转换四个方面介绍系统硬件设计。

数字信号处理芯片,我们选用采用Xilinx公司的XC2S50型号的FPGA芯片。用FPGA进行数据采集存储的有以下优点:(1)FPGA采取有多少数据转换芯片用多少控制单元模块的策略,功能控制模块与数据转换芯片是一一对应的关系,在硬件上保证了数据采集的完全并行性;(2)XC2S50芯片内有RAM块,可以设计为数据缓冲,方便解决数据流阻塞的问题;(3)FPGA芯片读写速度较高,在采集和存储速度都上不会存在任何问题;(4)FPGA的设计采用在线编程的方式进行,修改和调试都相当快捷、方便;(5)FPGA的外围电路除了一块配置芯片外,不再需要其他任何外围器件,集成度高,可靠性强。

对于A/D和D/A转换芯片,我们选用高精度的16位转换芯片ADS8402和MAX5631,有利于提高所测数据的精度。

2.3 硬件工作过程

传感器采集的模拟信号,经过ADS8402芯片以后转换为数字信号,将数字信号输入FPGA芯片中,FPGA芯片采用IIR数字滤波算法对输入信号进行处理,将处理后的信号一方面可以通过数字接口进行传输,另一方面可以经AD变换以模拟量的形式输出,通过前后输出和输入信号的对比,我们就可以直观的分析滤波效果。

3 IIR数字滤波器的原理和设计

数字滤波器是实现数字滤波的核心器件,按类型分为2大类:无限冲激响应 IIR和有限冲激响应FIR数字滤波器。IIR数字滤波器在很多领域中有着广阔的应用前景,与FIR数字滤波器相比,它可以用较低的阶数获得高选择性,所要求的阶用存储单元少,且成本低、信号延迟小,同时还可以利用模拟滤波器设计成果,设计工作量相对较小。

3.1 IIR 数字滤波器的结构

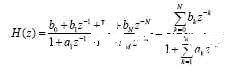

高阶IIR滤波器可通过传递函数, 表示为:

(3.1-1)

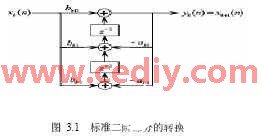

由于高阶IIR滤波器可以用若干个二阶网络级联起来构成。对于每一个二阶基本节,

它可以用转置直接II型结构加以实现, 如图3.1所示。

3.2 滤波器系数的计算

该系统的设计指标为:模拟信号采样频率为2MHZ,每周期最少采样20点,即模拟信号的通带边缘频率为fp = 100KHZ,阻带边缘频率fs = 1MHz,通带波动RP不大于0.1dB(通带误差不大于5%),阻带衰减AS不小于32dB。

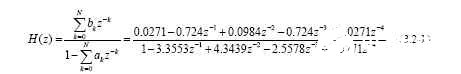

本系统函数H(z)的计算采用MATLAB软件中数字信号处理工具箱比较方便,其中有两个现成的函数可以使用:ellipord(Fp/π,Fs/π,Rp,As)函数用来计算数字椭圆滤波器的阶次N和3dB截止频率Fn,而 ellip(N,Rp,As,Fn)函数可以求得直接型椭圆IIR滤波器的各个系数。利用MATLAB软件进行计算,可得:b =(0.0271 -0.0724 0.0984 -0.0724 0.0271),a =(1.0000 -3.3553 4.3439 -2.5578 0.5771)。

通过调用以上两个函数计算得到的系统函数 :

(3.2-1)

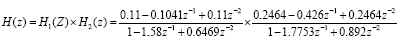

上面的式子是直接型结构,它的实现需用的乘法器和延迟单元相对较多,而且分子和分母的系数相差较大,需要较多的二进制位数才能实现相应的精度要求。如果采用二阶节级联实现,一来各个基本节的零点、极点可以很方便地单独进行调整,二来可以降低对二进制数位数的要求。下面给出了一个直接型结构转为级联型结构的 文件,即利用[b0,b,a]=dir2cas(b,a) ,可得b0 = 0.0271。对该系数进行合理安排后可得式(3.2-2):

为了使设计简便以及资源得充分利用,我们应该对系数进行进一步的量化,将系数由小数转化为整数,根据需要主要考虑量化精度和系统资源两方面,将二阶网络的系数同时扩大N倍后作为新的系数,然后再将输出网络的系数缩小N倍,并用二进制数进行表示,如下表3.1所示:

表3.1滤波器系数扩大

系数 a0 a1 a2 b0 b1

IIR1 原数据 0.11 0.1041 0.11 1.58 0.6469

扩大1024 后的系数 113 107 113 1618 662

IIR2 原系数 0.2464 0.426 0.2464 1.7753 0.892

扩大1024 后的系数 252 436 252 1818 913

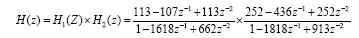

经过系数扩大后的系统函数级联表达式为:

(3.2-3)

(3.2-3)

以下为用VHDL语言所编写滤波器级联结构的部分源程序

第一级乘累加器的源程序如下:

entity mac is

Port (clk:in std_logic;

x0:in bits8;

x1:in bits8;

x2:in bits8;

y0:in bits8;

y1:in bits8;

y2:out bits8

);

end mac;

architecture flex of mac is

begin

process

begin

wait until clk=‘1’;

y2《=(113*x2-107*x1+113*x0+1618*y1-662*y0)/1024;

end process;

end flex;

其中第二级乘累加器的源程序与第一级基本相似,第一级的乘累加器输出为第二级乘累加器的一个输入,其余输入为第一级输出经过寄存器后的输出,或为反馈回来的信号,输入时钟和复位信号相同,第二级乘累加器的输出,也为总的输出,。

4 结束语

该验证过程的输入信号是一个正弦100HZ信号,在信号输出稳定后加上一个高脉冲200,一个低脉冲50,在初始状态时,信号的值初始化为0,当X信号经过连续的输入,信号逐渐稳定,并输入IIR滤波器的差分方程进行滤波,将干扰脉冲滤掉,输出100HZ稳定的正弦信号,该信号的通带衰减为0.09 dB,阻带衰减为32.7 dB,满足设计要求。

文章创新点:本文设计的通用的简单IIR数字滤波器适用于任何一种数据采集系统。一方面可以将传感器采集的模拟数据经A/D转换以后,再经过该数字滤波器后,进行滤除信号中的干扰,以模拟量的形式输出;另一方面还可以将采集到的数字信号直接经过数字量接口输出,经验证经过滤波处理有利于提高采集信号的精确度及准确度。

责任编辑:gt

-

基于DSP的FIR 数字滤波器设计2008-05-14 0

-

IIR数字滤波器的Matlab和FPGA实现2012-08-20 0

-

LabVIEW如何实现数字滤波器的设计2019-07-26 0

-

基于FPGA的FIR数字滤波器该怎么设计?2019-09-29 0

-

如何设计数字滤波器?2019-10-11 0

-

请问如何去设计IIR数字滤波器?2021-04-14 0

-

怎么实现基于Matlab的IIR数字滤波器设计?2021-05-31 0

-

用matlab生成IIR数字滤波器系数2021-08-17 0

-

基于LabVIEW的IIR数字滤波器的设计2009-09-09 460

-

用MATLAB辅助设计IIR数字滤波器2010-05-14 528

-

IIR数字滤波器设计-在FPGA上实现任意阶IIR数字滤波器2008-01-16 2296

-

用FPGA设计的四阶IIR数字滤波器2008-01-16 1144

-

基于FPGA的数字滤波器的设计与实现2010-01-07 3503

-

DSP04_IIR_数字滤波器设计和实现2016-07-29 937

-

FIR数字滤波器设计2022-04-05 4932

全部0条评论

快来发表一下你的评论吧 !