基于Altera的FPGA器件和VHDL语言实现数据采集系统的设计

可编程逻辑

描述

一、引言

传统的数据采集系统,通常采用单片机或DSP作为主要控制模块,控制ADC、存储器和其他外围电路的工作。随着数据采集对速度性能的要求越来越高,传统采集系统的弊端就越来越明显。单片机的时钟频率较低且需用软件实现数据采集,这使得采集速度和效率降低,此外软件运行时间在整个采样时间中也占很大的比例。而FPGA(现场可编程门阵列)有单片机无法比拟的优势。FPGA时钟频率高,内部延时小,全部控制逻辑由硬件完成,速度快、效率高。在此技术基础上,为了满足数据采集对速度的要求,本文就着重介绍了一种基于FPGA,采用VHDL硬件描述语言设计实现的高速数据采集系统。

二、系统的整体硬件设计

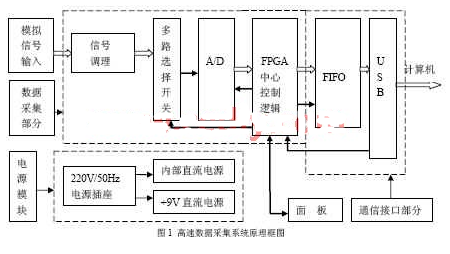

本数据系统以FPGA为中心、主要包括数据采集电路、通信接口电路、电源模块等几部分。其中中心控制逻辑主要负责产生各部分的控制信号,完成对整个系统的逻辑控制和对来自面板的工作模式控制信号的软件消抖,并对所采数据进行编祯处理,电源模块为该系统供电的同时,也为前端传感器提供了+9V的供电电源

系统采用60MHz晶振输入,模式控制信号来自面板上的控制开关,分别产生系统自检、采集开始、及手动复位三个控制信号。系统的原理框图如图1所示:

面板上有三个控制开关,分别为“复位”开关RST, “系统自检”开关S1和“采集开始”开关START。RST信号为外部的手动复位,当拨至高电平时,对系统所有的计数器清零;“系统自检”开关闭合时采集系统内部1路预知信号完成系统自检功能;“采集开始”开关有效时,系统开始对24路模拟信号进行采集,当“系统自检”开关和“采集开始”同时有效时,对系统进行复位。

1. 数据采集部

该部分主要由一片高速AD芯片和一片Altera的FPGA构成。由于本系统设计采样速度最大为50M,根据采样定理,采样频率至少应该在100M以上,所以AD芯片采用的是MAXIM公司的MAX100。该芯片转换精度8位,1.8v电源供电,低功耗,最高工作速度为250MSPS。经过测试可以很好的满足系统测试要求。

通常在低速数据采集系统中常使用MCU作为CPU来控制。但在高速数据采集系统中,往往会受到MCU的影响,而且随着速度的提高ADC,RAM,MCU之间的时序同步问题也会显示出来。因此本系统使用了高速、多I/O口的FPGA芯片来控制ADC和RAM等,从而很好的解决了采样速度过高和时序同步的问题。

FPGA(Field Programmable Gate Array)是从PAL,GAL发展而来的阵列型高密度PLO器件,具有高密度,高速度,低功耗等特点。特别适合实现复杂的组合逻辑。根据系统要求,本系统中使用的FPGA芯片型号为Altera公司的EPF10K10TC144-3。它的可用门数7000个,最大用户I/O数134,计数器的工作频率可达200MHz。在该系统中FPGA实现的功能逻辑主要有:

(1) 完成对来自面板的工作模式控制信号的软件消抖。

(2) 接收采集模式开关发出的开始采样信号START,实现对ADC的控制,开始AD转换;

(3) 当FIFO存储器半满时,发出一个Half Flag信号,通知USB芯片可以读数,FIFO存储器为空时,发出一个Empty Flag信号,提示USB芯片停止读数。

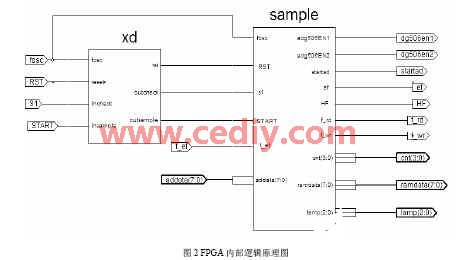

FPGA的功能逻辑使用VHDL语言来实现,这是一种硬件描述语言,主要用于描述数字系统的结构、行为、功能和接口。使用VHDL语言设计硬件电路时,可以使设计者免除编写逻辑表达式或真值表的工作。这样使硬件电路设计的难度有了大幅度的降低,从而可以提高工作效率,缩短硬件电路的设计周期。使用VHDL语言实现的采集系统FPGA内部原理图如图2所示。

图中共有两个模块,xd模块主要完成对输入信号的消抖,能使系统工作更稳定。Sample模块是本系统的核心部分,它主要负责各部分的逻辑控制及AD采样数据的编祯处理。

2. 通信接口部分

通用串行总线USB是一种新型的通信标准,它具有使用灵活,连接方便,通信速度快,能独立供电等特点。目前,越来越多的计算机外围设备开始采用USB的通信接口。由于本系统采集速度高数据量大,因此,也采用了USB通信接口。

目前生产USB芯片的厂商很多,主要的产品有CYPRESS公司的EZ-USB,PHIPILIPS公司的PDUSBD12,National Semiconductor公司r的USB9604等。本设计采用的是CYPRESS公司的带8051内核单片机的EZ-USB系列参CY7C68013。该芯片采用改进的8051内核,与标准的8051指令完全兼容,除此之外内部还集成了存储器、智能USB接口引擎、USB收发模块、串行口等。

在USB下芯片CY7C68013和EPF10K10TC144-3FPGA之间采用了FIFO(First in First out SRAM)芯片作为数据交换的缓冲连接,这样可以使USB接口芯片和FPGA之间的最大数据交换速度超过USB总线的速度,使之不会成为数据传输的瓶颈,从而使FPGA和主机之间的数据传输速度只受USB协议限制。

由于CY7C68013芯片内嵌8位8051处理器,因此使用两片FIFO芯片实现FPGA和USB接口之间的双向通信。FIFO芯片选用具有16K×9bits内存的IDT7206,从FPGA传输的数据首先保存在FIFO中,然后再由CY7C68013带走,这样使数据的传输不会出现堵塞的情况。对与IDT7206只具有双端数据总线和状态信号,没有地址总线,所以FPGA采用I/O译码的方式直接访问FIFO。FIFO的状态信号有空、半满和满,它们都是低电平有效,通过这三个信号就可以灵活的控制FIFO的读写。

CYPRESS公司为EZ-USB系列的芯片提供了固件程序和驱动程序模块和例程。固件程序与驱动程序可以独立的被调试,且调试方便,相对于其它USB芯片,可以提高开发速度。

三、 FPGA主要模块的逻辑实现

FPGA系统的硬件设计模块主要有消抖模块、采集模块两部分。采集模块又包括逻辑控制模块、时钟逻辑运算模块、时钟生成模块等。下面主要就消抖和FIFO控制部分进行描述和实现。

1.消抖模块设计

为了系统各工作状态更稳定,当FPGA接受到一个工作状态信号时,启动一个计数器,若计数器能计到设置的最大值则认为该工作状态信号有效,否则认为无效。消抖的FPGA具体实现方法如下所示

process(reset,fosc)

VARIABLE count : INTEGER range 0 to 50;

begin

if reset = ‘0’ then

count := 0;

outcheck 《= ‘0’;

elsif fosc‘event and fosc=’1‘ then

if incheck=’0‘ then

if count 《 50 then

count := count + 1;

outcheck 《= ’0‘;

else

count := count;

outcheck 《= ’1‘;

end if;

else

count := 0;

outcheck 《= ’0‘;

end if;

end if;

end process;

仿真结果如图3所示:

由图3可以看出通过此方法可以消除因工作状态信号时抖动而引起的误操作,保证了系统工作的稳定性

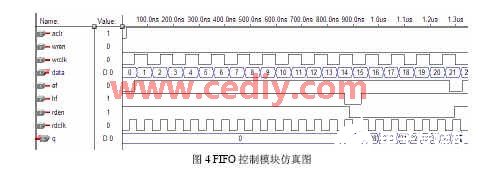

2.FIFO控制模块设计

系统首先把采集到的数据缓存到FIFO里面,当存储达到用户设定的余度时,便送出一个请求信号,通知USB芯片读取数据。FIFO余度值的大小由用户自己设定,但此值原则上不能过于接近FIFO的深度。因为在USB芯片响应这一请求信号,进行读数处理的过程中,FPGA仍在进行数据的采集和存储。如果余度值过于接近FIFO深度,FIFO容易产生溢出的错误。因此本系统中以FIFO芯片IDT7206的半满作为设定的余度,当IDT7206存储数据达到其容量的一半时,FPGA就会送出一个请求USB读取数据的信号。FIFO控制模块的信号有:异步清零aclr;读写数据q/data;读写使能rden/wren;空/半满标志ef/hf。数据data在写使能有效的情况下按照写时钟往FIFO里面存储,在读使能时,数据按照读时钟的速度从q数据总线上输出。其实现和仿真如图4所示:

由图4可以看出,读使能rden在半满信号下降沿到来后才有效,即数据才开始被USB芯片从FIFO中读出,在空信号下降沿到来后读使能rden信号无效,数据停止读取。而整个过程FPGA都在进行数据的采集。

四、结 论

本文完成高速、多通道的数据采集系统的FPGA设计,该系统具有电路简单、体积小等优点。利用EDA工具和语言对FPGA进行设计、仿真和验证,这便于设计的修改和优化,大大缩短了产品的开发设计周期。由FPGA具有在线编程的特点可以依据现场的具体情况,对FPGA的内部逻辑配置进行修改,进一步增加了系统应用的灵活性,经测试该设计达到了满意的效果,是一种比较理想的多通道、高速数据采集方案。

责任编辑:gt

-

基于FPGA的图像边缘检测系统设计,用VHDL语言实现该怎么做?2018-05-10 0

-

基于CPLD和FPGA的VHDL语言电路优化设计2019-06-18 0

-

如何用VHDL语言实现帧同步的设计?2021-04-08 0

-

如何利用FPGA实现高速连续数据采集系统设计?2021-04-08 0

-

FPGA技术如何用VHDL语言实现8位RISC微处理器?2021-04-13 0

-

如何使用VHDL硬件描述语言实现的十六路彩灯控制系统?2021-04-19 0

-

如何利用VHDL语言实现FPGA与单片机的串口异步通信电路?2021-04-29 0

-

如何利用FPGA和VHDL语言实现PCM码的解调?2021-05-07 0

-

用VHDL语言实现3分频电路2007-08-21 5547

-

基于FPGA的数据采集系统设计2012-05-08 723

-

基于FPGA和UART的MCU总线数据采集系统设计2012-09-25 497

-

FM收音机的解码及控制器VHDL语言实现2016-06-07 742

-

如何使用FPGA进行数据采集系统电路设计?工作原理和设计过程详细分析2018-09-06 2052

-

如何使用FPGA和DSP进行高速数据采集系统设计2018-11-07 973

-

如何使用FPGA实现数字采集系统电路的设计2020-07-29 745

全部0条评论

快来发表一下你的评论吧 !