FPGA开发板中关于晶振几大问题

可编程逻辑

1340人已加入

描述

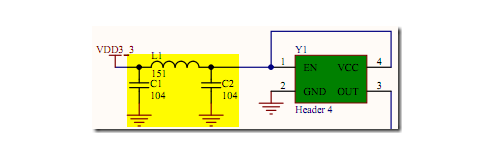

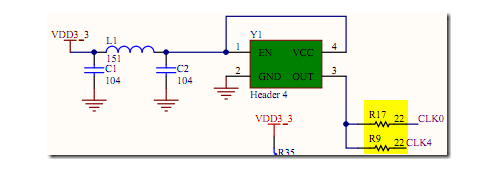

下面几个是FPGA开发板使用的晶振。加滤波,是为了防止振荡器干扰电源。电源稳定,振荡器的频率较高,用一个104电容去耦就够了,如图2所示。图3使用的π型滤波器,由一个电感器两个电容器构成,它的输入端和输出端都呈低阻抗性,因为元件比L或C型多,故抑制性能要好的多。

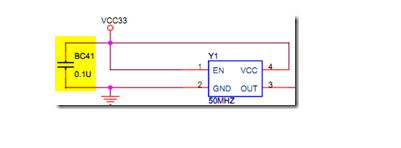

图1 Cyclone III Start Kit 时钟电路

图2 DE1 时钟电路

图3 艾米电子EP2C8 FPGA开发板 时钟电路

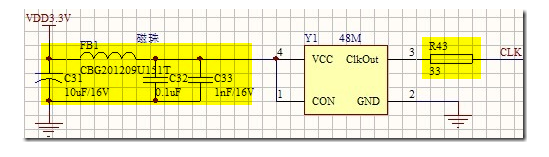

再看下面的有源晶振的输出端,串电阻。芯片的输入端有输入电容,走线也有分布电容,没这个电阻,振荡器输出的上下沿有冲击电流,产生辐射。特别是阻抗不匹配时,高频信号会反射回来干扰信号源。串上电阻,能消除反射波的影响。

图4

图5

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

#fpga开发板 Lattic-mipi开发板明德扬科技 2023-10-25

-

最新的FPGA单片机开发板2009-07-16 0

-

求FPGA CYCLONE IV E系列板上晶振的使用2014-11-24 0

-

关于STM32开发板晶振相关的问题汇总2015-10-14 0

-

开发板晶振频率自动变化问题2016-12-06 0

-

如何只用开发板求板上外部晶振HSE频率值2018-05-17 0

-

请问AD9954开发板上外接晶振型号和封装应该为多少2018-08-24 0

-

【EG4S20-MINI-DEV 试用体验】FPGA新手学习开发板2019-06-24 0

-

ALIENTEK MINI STM32开发板中的两个晶振各是干什么的?2019-08-19 0

-

关于STM32外部晶振的问题如何解2020-05-20 0

-

怎样去选择CT107D开发板上的晶振频率呢2021-10-27 0

-

请问开发板上的时钟晶振外壳用不用接地?2023-10-31 0

全部0条评论

快来发表一下你的评论吧 !