数据收发器CY7B923/933的性能特点和应用范围

移动通信

描述

串行数据传输可实现长距离高速通信,且电缆线少、成本低、安装方便,在计算机网络中得到了广泛应用,并日趋成为长距离数据通信的主要方式。CYPRESS公司的数据收发器CY7B923/933使用方便、可靠性好,可广泛用于长距离高速点对点串行通信中,如光纤通信设备、工作站与海量存储互连、视频点播、语音图像多媒体传输设备及其它长距离高速串行通信场合。CY7B923/933性能特点如下:

·适用于Fibre Channel、IBM ESCON、ATM;

·8B/10B编码传输或不编码直传,传输速为160、330、400Mbps三档;

·最大传输距离(330Mbps的参考值)为:光纤几千米,同轴电缆150米,屏蔽双绞线80米,非屏双绞线40米;

·具有较强的自检功能;

·单一+5V电源;

·TTL同步I/O。

1 结构原理及功能

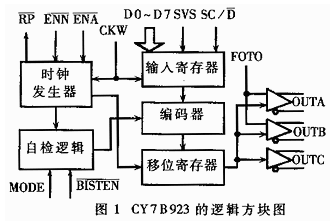

图1是CY7B923的逻辑方块图,其功能是将8bit并行TTL输入数据(D0~D7)转换为PECL串行差分位流输出。输入寄存器用于输入数据,

同序与标准FIFO一致,使能端ENA和ENN可选择时钟上升沿写入数据。输入数据由编码器编码为便于串行链路传输的8B/10B传输码,由SC/D(专用字/数据)端电平控制,将D0~D7输入编成数据码或专用字码。时钟发生器含有一个锁相环PLL,将发送器时钟CKW(数据按字节输入的时钟)十倍频形成位时钟,驱动移位寄存器。移位寄存器将数据变成串行位流,分三路同时输出,FOTO可关闭OUTA和OUTB输出。自检逻辑产生通信系统自检用发送信号。

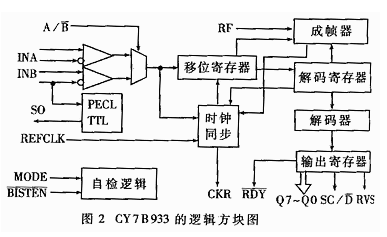

图2 是CY7B933的逻辑方块图,其功能是将INA或INB的PECL串行差分输入位流转换为8bit并行TTL数据输出Q7~Q0。时钟同步器内嵌锁相环 PLL跟踪输入数据位流的频率,产生与发送时钟同步的时钟。移位寄存器按位接收串行数据,在同步时钟作用下将数据按位送往成帖器。成帖器使位流数据正确地为原始数据或专用字,用RVS=H作数据违规或RD(Running Disparity)错的报错信号。串/并转换后的数据从输出寄存器Q7~Q0并行输出。

2 工作模式及8B/10B编码

CY7B923/933有编码、直传两种工作模式及自检模式,由MODE、BISTEN端信号控制。

2.1 编码模式

MODE =1,收发送器工作于8B/10B编码模式,即8位数据或专用字由7B923编码为10位的传输码再逐位传送。10位传输码包括了所有256个8位组合,这些代码符合ANSI X3.230(Fibre Channel)及IBM ECSON Channel规范。使用传输码的优点是:(1)使传输过程1与0的数目均衡,每个8B的数据或专用字对应两个10B的传输码,用参数RD表征传输1及0 的状况。若1比0多则RD取正值,下一个字节发送0的状况。若1比0多则RD取正值,下一个字节发送0比1多的传输码。反之,则RD取负值,下次发送1比 0多的传输码,这样可保证传输的直流成分接近0,基线漂移减至最小;(2)附加位能保证串行位流中有足够的跃变,使接收器能从这些跃变中恢复发送时钟;(3)这种编码大大增加了探测位错或多位错的可能性,一些专用字使用独特的位组合,容易识别,可帮助接收器数据成帧;(4)可用同种编码传输数据或专用字。若为数据,SC/D端应加低电平,编码使用数据字符集,专用字符包含Fibre Channel、ESCON和其它专用系统以及用于诊断的所有协议字符。诊断字符可用于测试Fibre Channel等的连接、诊断系统对故障的响应、系统的时序等。8B数据或专用字编码为10B传输码通过查编码表实现。对应于RD正负两种取值,

每个数据或专用字有两种编码,发送器先取正或负值为RD初值,根据要发送的数据或专用字及当前的RD值,查8B对应的10B代码即实际发送的传输码,并计算该传输码的RD值作为当前值,与下个要传送数据共同查表确定下一个传输码。

2.2 直传模式

MODE=H,收发送器工作于直传模式,即收发送器直接传输数据不编码,编码和解码由外部协议控制器完成。输入分成10位,数据需预先编码,编码方式任意,但需保证有足够的跃变密度(每10位至少一次),使接收器锁相环能正确锁定相位,且编码需与传输介质兼容。

无论是编码模式还是直传模式,若处于空闲状态(时钟CKW上升沿时ENA=ENN=H),编码器将自动插入同步字K28.5(即C5.0)以保证接收器与发送器处在同步状态。

2.3 自检模式

BISTEL =1,收发送器工作于自检模式,7B923可分别发送两种信号来检测整个通信链路是否正常:一种是1与0相间的连续信号;另一种是循环发送的伪随机序列信号。若为后者,7B923输入寄存器转换成线性反馈移位寄存器LFSR,它可产生一组511个字节的伪随机代码序列,包括了所有的数据字和专用字。 7B933将输出寄存器也变成LFSR,产生与发送器相同的伪随机代码序列,并与接收的序列相比较。若相同,则整个通信系统工作正常,否则为异常,使 RVS=H给出错误信号。每次循环,7B923的RP及7B933的RDY都将输出一脉冲,此脉冲可用于记录循环次数以控制自检时间。7B923还可发送违规信号,以检测报错系统是否正常。这些信号都大大方便了故障诊断。

3 CY7B923/933应用电路

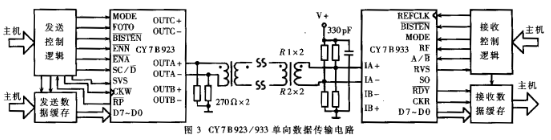

图3 为采用CY7B923/933实现的单向数据传输的应用电路。主机发送控制命令,通过控制逻辑控制CY7B923/933工作在传输或自检模式。这里控制逻辑用FPGA实现,也可采用其它数据逻辑器件实现。控制电路应包含RP、RVS端的检测,以判断系统工作正常与否,及时进行错误处理。主机数据传输速度一般与CY7B923/933不一致,发送端及接收端都需设置数据缓存,缓存一般用FIFO,我们采用CYPRESS公司的CY7C45系列,它可与 CY7B923/933组成无缝接口。若用FIFO的标志位作控制信号,则应注意标志延迟时间。CY87B933的输出信号CKR,可作为其输出数据写入 FIFO垢时钟,RDY可作写FIFO使能信号,使用RDY的优点是同步字串到它无效,自动滤除同步字串,这就保证了只将有奖惩数据写入FIFO,避免同步字将FIFO填满。电路板设计应采用四层板,CFY7B923/933的位置应靠近双绞线接口使连线最短,连线长度应尽量保持对称。输出输入端都应接匹配电阻,如图3所示。R1、R2阻值由下式给出:R1=(VccRt)/Vtt;R2=(VccRt)/(Vcc-Ctt)。式中,Rt为传输线阻抗;Vtt=Vcc-2V。Vcc=5V,UTP双绞线阻抗为100Ω,则R1=183Ω,R2=275Ω。

发送数据前,先进行系统自检,然后进入传输状态,数据在发送时钟CKW上升沿进入发送器,通过发送器的延迟为21tB-10ns(tB为移位时钟周期, tB=1/10CKW),经传输线、变压器进入接收器,数据通过接收器的延时为24tB+10ns。变压器隔离传输线上可能的高电压,并有带通滤波的作用。当7B933的RF=H,成帧器使能,成帧器开始搜导数据流中的同步字K28.5,并以K28.5边界为基准,确定后续数据的字节边界。一些随机错误可导致串行数据变成同步字K28.5,造成错误成帧。为避免出错,可在数据同步过程中关闭成帧器,即令成帧器使能端RF=L,或令RF=H超过2048字节,此时需在连续5字节中有两个K28.5才能启动成帧功能,可大大减少偶然错误导致成帧。

责任编辑:gt

-

CY7C68013的工作范围及性能简介2010-04-19 0

-

捷变频收发器AD936X的特点和优势2018-10-22 0

-

适用于CY7C637无线USB收发器的通用驱动程序2019-02-12 0

-

请问63813是否支持0个数据收发器的端点?2019-08-12 0

-

CAN收发器有什么特点?2019-09-03 0

-

高速串行数据通信发送芯片CY7B923的原理及应用2009-04-27 771

-

CY7B923用作ECL时钟源2009-06-15 748

-

对CY7B923 CY7B933(HOTLink)与具有宽带2009-06-15 1050

-

介绍(HOTLink)CY7B933 RDY引脚在编码、旁路2009-06-15 937

-

连接CY7B923和CY7B933(HOTlink器件)至定2009-06-16 1009

-

连接CY7B923和CY7B933(HOTlink器件)至宽2009-06-16 848

-

如何用Cypress的CY7B923 CY7B933替换Am2009-06-16 979

-

在CY37032 CPLD中,用CY7B933 HOTLin2009-06-16 920

-

基于DSP的转台用光纤数据传输系统设计2009-12-22 637

-

高速串行数据通信CY7B923芯片的性能特点及设计实例2021-05-22 3689

全部0条评论

快来发表一下你的评论吧 !