基于可编程时钟芯片实现遥感卫星地面记录系统的模拟源设计

可编程逻辑

描述

1 引言

卫星数据模拟源是一种能够模拟遥感卫星产生相关卫星数据信号的信号源。主要用于遥感卫星记录系统的系统故障检测以及新系统开发验证。

当记录系统出现故障需要检修时,用模拟的卫星信号代替真实的卫星信号进行系统维护,可以免受卫星过境时间的影响,使得系统的维护工作更方便。另外,在卫星发射之前,相关记录系统的研制中,模拟源可以作为记录系统的测试信号。

同时随着遥感技术的广泛使用,遥感卫星数量的不断增加,不同卫星之间的数据存档格式往往不同,其间经常需要进行转换;由于介质寿命有限,对于需要长期保存得的数据资料,通常需要定期进行介质转换。以上工作也可通过模拟源进行数据回放再存档,存档时选择不同的存档格式或存档介质,达到格式转换或介质转换的目的。

所以模拟源在地面记录系统中起着十分重要的作用。

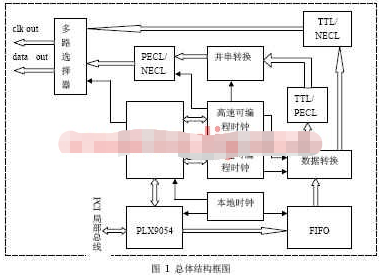

2 总体结构

本文设计的遥感卫星数据模拟源的总体结构如图1所示,其主要原理为:从存储设备读取已存档遥感卫星数据或编程生成的特定图像数据,通过PCI总线发送到PLX9054,PLX9054接收到的数据经过数据缓存、并串转换和电平转换等处理形成与实际卫星码速率一样的串行数据流和伴随时钟。为了模拟各种不同类型的卫星,模拟源的数据发送频率必须是可变的,输出范围:1MHz~400MHz,步进为1MHz。

3 关键电路实现

3.1 高速DMA数据发送

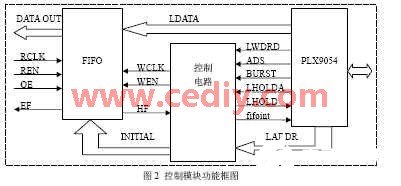

为满足高速的要求,本设计使用插卡形式,且采用PCI总线。PCI接口芯片很多,本文采用PLX公司的PLX9054。PLX9054支持主/从模式,内置6个128bytes或64bytes的FIFO,两个独立的DMA通道,符合PCI v2.2规范,理论传输速率为132MB/s,满足高速数据传输的要求。为了保证连续的数据发送,Local端使用大容量的FIFO进行数据缓存,这里使用IDT公司的大容量FIFO——IDT72V36110,大小为131072 x 36。该FIFO具有独立的读写时钟,五个输出标志位,设计中只用到半满(HF)和空(EF)两个标志位,其中半满标志位用于PLX9054往FIFO写数据,空标志位用于数据转换模块从FIFO读数据。FIFO在使用前必须先进行初始化,如设置FIFO工作模式,读写数据宽度等,这部分工作由控制电路在系统上电后自动完成,使FIFO一直处于工作状态。

在进行数据发送时, PCI局部总线端启动DMA写数据,每次写数据的大小为FIFO容量的一半,结束后即完成一次DMA写数据,如果FIFO中的数据没有被同时往外读,此时FIFO的半满标志位有效为低电平,空标志位无效为高电平。当然实际使用时,转换模块根据空标志无效,判断FIFO有数据,在PLX9054向FIFO写数据的同时对FIFO进行读数据。当FIFO中数据少于容量的一半时,半满标志位无效为高电平,控制模块马上通过PLX9054向系统发送中断请求,系统响应后启动下一次DMA传输。控制模块使用ALTERA公司的MAX3000A系列CPLD——MAX3256A,通过Verilog HDL语言编程实现,其功能框图如上图2所示。

3.2 卫星模拟数据输出

卫星下行数据为串行的差分NECL电平信号,而FIFO中的数据为32位并行TTL电平数据,所以要对FIFO中的数据进行并串转换和电平转换。进行并串转换需要串行时钟信号,为了能够模拟各种不同类型的卫星,串行信号的伴随时钟频率必须是可变的;同时为了适应遥感卫星的下行数据不断向高速发展的趋势,本设计的最高输出伴随时钟为400MHz,总的输出范围:1MHz~400MHz。这个频率范围比较大,用单一的可编程锁相环时钟芯片很难达到。设计中对时钟范围进行了分段,低频部分:1MHz~160MHz,高频部分:160MHz~400MHz,通过两片可编程时钟芯片的组合来完成。

3.2.1 低速可编程时钟

低速可编程时钟选用Cypress公司的可编程锁相环时钟芯片——CY22150,它的输出范围:80Khz~200MHz,且输出频率任意可编程。它具有低抖动、低畸变、高精度的特点,支持在系统编程,编程数据通过I2C总线送入时钟芯片。I2C总线有两根传输线,一根时钟线SCLK,一根数据线SDAT,其中数据线SDAT是双向的。I2C系统有它自己的传输协议。一般在系统中都是用单片机系统实现I2C传输协议。因为单片机系统中软件的每条指令的执行时间都是可以预知的,可严格的控制好两条传输线的时序关系,可以比较方便的实现I2C协议。但是,在本系统中如果仅仅因为时钟电路的现场编程而引入单片机系统,会使电路的设计变得很复杂,而且,加上购买单片机仿真器和编程的费用,整个系统的费用将增加很多。因此在设计时放弃了这种常规设计方法。考虑到I2C总线标准对最低码速率没有严格的要求,尝试依靠PLX9054的I/O读写,并通过CPLD中的逻辑控制完成模拟I2C总线,用软件的方法按照I2C时序完成时钟芯片的现场编程功能。实验证明,此方法可行。

3.2.2 高速可编程时钟

要实现400MHz的高频,只能选择ECL器件,设计中采用ON Semiconductor公司的可编程时钟芯片NBC12429,输出范围:25MHz~400MHz,步进为1MHz,实际使用中只用到160MHz~400MHz部分。它也支持现场可编程,编程方式有两种:并行编程方式和串行编程方式,串行编程方式只需要三根数据线,比并行编程方式需要12根要简单,故选用串行方式。它的编程比CY22150简单,只需要连续地把编程数据写到它的内部寄存器就可以。

3.2.3 数据转换

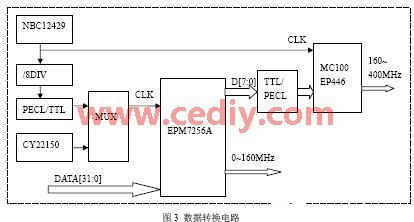

数据转换部分主要完成对FIFO的数据读取以及并串转换,考虑到高速和灵活性,采用Verilog HDL语言编程实现,编程器件使用ALTERA公司的MAX7000A系列CPLD——EMP7256A-5,理论上支持200MHz的时钟频率,实际使用时经过优化后能达到160MHz。当输出频率为1MHz~160MHz时,串并转换比较简单,直接在CPLD里就可以完成;当输出频率为160MHz~400MHz时,串并转换相对麻烦些,整个转换分两步完成:先在CPLD里完成32位到8位的转换,然后采用ON Semiconductor公司的高速ECL并串转换芯片——MC100EP446完成8位并行到串行的转换,而且中间要进行一次TTL电平到PECL电平的转换,具体设计方案如图3所示。

3.2.4 电平转换及输出

模拟源的最终输出信号应该是差分NECL电平信号,数据进行并串转换后,必须进行相应的电平转换,其中低速输出进行TTL电平到NECL电平转换,高速输出进行PECL电平到NECL电平转换,最后通过二选一选择器输出。

4实验与结论

模拟源采用Windows驱动程序模型(WDM)开发驱动程序,在驱动程序的基础上用VC6.0开发相应的应用软件,包括时钟编程,存档数据发送和棋盘格数据生成并发送等。最后在使用Windows 2000平台的高性能服务器上进行了卫星存档数据和程序生成的棋盘格数据的发送测试,其中高性能服务器使用双Xeon CPU,1G内存和高速Raid。在发送过程中,和模拟源相连的记录系统进行实时记录,并用示波器对发送频率进行实际测量。经过不同频率的多次测试表明,示波器的测量结果与预定发送频率一致,对记录文件和被发送文件进行的误码率计算结果,也保持在记录系统允许的范围内。以上测试结果表明,此模拟源工作稳定,达到设计要求的性能指标,有效地解决了地面记录系统开发和维护过程中所需的数据源问题。

责任编辑:gt

-

基于可编程模拟器件的小信号测量系统应用2019-07-02 0

-

可编程模拟的各种架构2019-07-05 0

-

如何利用FPGA设计可编程电压源系统?2019-08-07 0

-

怎么利用FPGA设计可编程电压源系统?2019-08-19 0

-

如何设计基于FPGA的可编程电压源系统?2019-11-04 0

-

如何更有效地使用可编程时钟器件?2021-04-20 0

-

如何采用FPGA设计可编程电压源系统?2021-04-29 0

-

可编程模拟器件原理与开发2010-02-06 487

-

在系统可编程器件在模拟电路中的应用2010-04-25 559

-

在系统可编程模拟电路的原理与应用2010-05-08 399

-

高速可编程遥感卫星数据模拟源的设计与实现2010-08-09 941

-

用在系统可编程模拟器件实现双二阶型滤波器2009-12-08 548

-

采用FPGA的可编程电压源系统原理及设计2010-03-22 2131

-

片上可编程系统原理及应用2021-10-01 1639

-

可编程片上系统是什么2024-03-28 161

全部0条评论

快来发表一下你的评论吧 !