基于独立的CPLD或FPGA的控制电路实现物理隔离网闸的设计

可编程逻辑

描述

1.引言

随着互联网的广泛应用,网络信息安全已成为人们越来越关注的问题。但是目前国内外采用最普遍的网络安全措施防火墙类软件存在如下缺陷:第一防火墙隔离的网络还是基于TCP/IP协议来进行信息交换的,而TCP/IP协议是存在漏洞,因此它无法防止协议本身的漏洞;第二防火墙的运行离不开操作系统,操作系统和防火墙软件都可能存在未知的漏洞,从而不能禁止利用这些漏洞而进行的网络入侵和攻击的发生,使得整个防护体系十分脆弱;第三防火墙类软件在可信网络与不可信网络之间提供了网络的直连通道,但是它并不能保证准许放行的数据的安全性,同时在对入侵检测上也存在局限性。而物理隔离技术通过中断内部网络与互联网的直接连接,不支持TCP/IP协议,不依赖于操作系统,只允许内外网间进行适度的原始数据交换,从而在根本上解决了防火墙的缺陷,为内部可信网络可以提供更好的安全性保护。所以我国在《计算机信息系统国际互联网管理规定》第六条中规定涉及国家秘密的计算机必须实行物理隔离。

2.物理隔离网闸

物理隔离网闸(以下简称网闸)是一种采用物理隔离技术,由带有多种控制功能专用硬件在电路上切断网络之间的链路层连接,并能够在网络间进行安全适度的应用数据交换的网络安全设备,它通过使内外部主机在任何时间都完全断开,对TCP/IP协议及应用协议的剥离和重建,实现内外网在OSI模型七层的网络隔离。通常具备有安全隔离、内核防护、协议转换、病毒查杀、访问控制、安全审计和身份认证,七大安全功能模块。其硬件设备主要由三部分组成:外部处理单元、内部处理单元、隔离硬件。

目前网闸的技术路线主要有基于SCSI的开关技术和基于总线的开关技术两种。基于总线的实时开关技术的网闸采用双端口静态存储器(Dual Port SRAM,以下简称DPRAM)配合基于独立的CPLD或FPGA的控制电路,双端口各自通过开关与独立的计算机主机连接(如图1)。CPLD(或FPGA)作为独立的控制电路保证双端口静态存储器的每一端口上存在一个开关,且两个开关不能同时闭合即K1×K2=0。基于SCSI开关技术的网闸和图1相似,只是数据通道换为SCSI硬盘接口,而存储介质使用的是SCSI硬盘,控制单元使用专门设计的硬件电路板实现。

但是目前采用上述实现技术的网闸系统普遍存在数据交换速度低、数据交换实时性差的问题。为克服这些问题,我们在进行MIPS网闸设计中提出并应用了基于总线的双通道循环缓冲区实时开关技术。

3. 基于总线的双通道循环缓冲区实时开关技术

在图1原有的设计中,进行数据交换时,内部和外部处理单元在任何时刻只有一方与隔离硬件相连。如果数据通道的速度为A bps,那么内外部处理单元间的数据交换速度最高只能达到A/2 bps,未能充分利用发挥数据通道的能力。为此我们提出如图2的设计。

将原有设计中的DPRAM存储区域分为A(a1,a2,…an)和B(b1,b2,…bn)两块(ai、bi为n个相等的小块存储区),K1和K2的约束为K1ai×K2ai=0且K1bi×K2bi=0(K1ai表示K1与ai相连,K2ai、K1bi、K2bi与此相同)。如此一来就将原有图1设计中的一个双向数据通道变为了两个单向的数据通道,当内外部主机中的一方对ai或bi进行访问时,另一方仍可以对aj或bj(i≠j)进行访问,同时实现了传输数据的隔离。

假设开关K1,K2与每一存储区域ai,bi的访问是随机进行的,那么在足够长的一段时间内,开关K1,K2与每一存储区域ai,bi的连接概率都是相等的,因此

我们对ai、bi区域的访问控制进行设计,使其分别组成两个循环缓冲区,这将进一步的减少内外部处理单元对隔离硬件访问读写冲突的发生,同时也提高了交换数据的实时性。通过这样的设计能使系统总线数据通道工作于“全双工”状态,提高了数据交换的速度和实时性,提升了系统的整体性能,满足系统更高的应用需求。

4.硬件设计实现

在我们设计的网闸系统中其内外部处理单元由基于MIPS处理器的嵌入式计算机系统组成,隔离硬件模块为双端口RAM卡,其包含通断控制电路,读写保护逻辑和数据存储电路。隔离硬件与内外部处理单元采用SDRAM总线连接。

4.1内外部处理单元的设计实现

内外部处理单元MIPS主板的硬件电路结构上与PC机相似,如图3所示。

图3 MIPS主板的硬件电路框图

内外处理单元与内外网的连接通过板上的千兆网卡实现的,监控主机系统与网闸系统的连接是通过百兆网络口实现的,该百兆口是对网闸进行设置的唯一端口且不和其它网络相连接。同时该嵌入式计算机系统还对外提供了如PCI、IDE、串口等常用接口。独立的嵌入式主机为内(外)网提供了该侧的全部硬件和软件资源,保证了系统内数据可以获得及时的处理。

4.2双端口RAM卡的设计实现

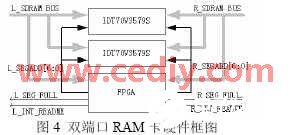

由于在MIPS网闸中实现数据交换的过程是通过对双端口RAM卡上的存储芯片的读写来完成的。存储芯片作为为内外网络的数据交换存储区,其访问设计方案决定了MIPS网闸交换的整体速度。为了最大限度的提高MIPS网闸的数据交换速度,我们MIPS网闸项目组采用了基于SDRAM总线的双通道循环缓冲区实时开关技术,使得MIPS网闸数据交换速度有了突破性的提高。 图4为双端口RAM卡的硬件框图。

设计中采用IDT70V3579S作为内外网间的数据缓冲区,Xilinx Virtex-II XC2V40作为控制单元。设计中采用两片70V3579S,使得数据存储区域和SDRAM位宽相同(64bit数据位8bit校验位)。整个数据存储区域为32K×72bit,容量为256KB,在设计中A、B存储区域大小均为128KB,同时将A、B分别划分成64段ai、bi,每段大小为2KB(因为MIPS处理器RM7065C的cache页替换每次为2KB,如此设置有助于提高系统性能)。如此一来DPRAM地址将分为两部分:高位地址(段地址)和低位地址(段内地址)。

在MIPS网闸中双端口RAM卡与内外部处理单元间数据交换非常频繁,根据第3节的设计原理我们利用FPGA来解决内外网机对双口RAM读写的操作冲突,提高速据传输速度。在FPGA内设置有如下寄存器:REG_L_W是用于控制左端写入的6位段地址寄存器,可以直接对应DPRAM的左端写入段地址;REG_R_R是用于控制右端读出的6位段地址寄存器,可以直接对应DPRAM的右端读出段地址;REG_L_RES是对应于64段ai资源使用情况的64位段标志寄存器;REG_R_W是用于控制右端写入的6位段地址寄存器,可以直接对应DPRAM的右端写入段地址;REG_L_R是用于控制左端读出的6位段地址寄存器,可以直接对应DPRAM的左端读出段地址;REG_R_RES是对应于64段bi资源使用情况的64位段标志寄存器。通过寄存器REG_L_W、REG_R_R、REG_R_W、REG_L_R将ai、bi组成循环缓冲区,同时实现K1、K2与不同的段的连接。通过寄存器REG_L_RES、REG_R_RES指示判断段资源的使用情况,并通知系统北桥。

当北桥向DPRAM写入或读出数据时,由FPGA根据其内部管理寄存器,发出高7位地址L/R_SEGADD[6:0]控制北桥具体访问的数据段ai、bi,而且在FPGA中硬件设置使两端不能同时对同一目标段进行访问,从而控制K1、K2与ai、bi的连接,实现数据的隔离。

对于双端口RAM卡与SDRAM接口的连接实现如下:首先,MIPS网闸是一个数据交换类的共享存储系统,而MIPS主板中北桥GT芯片支持UMA(同一地址架构,Unified Memory Architecture),这一特性为设计共享存储系统提供了很高的灵活性,为我们设计实现提供了便利。其次,在设计中采用的XC2V40芯片能与外部存储器(如SDR/DDR SDRAM,SDR/DDR SRAM )之间建立高性能接口,非常适合我们MIPS网闸系统的应用要求。最为关键的是,通过比较DPRAM与SDRAM在读写的操作时序,两者具有相似性,其主要时序两者基本一致。DPRAM与SDRAM读写操作的最大不同在于DPRAM进行读写操作时,其地址是一次输出同时数据线上信号也发生变化,而SDRAM的地址是分行列地址发出的,在发送行地址等待TRCD周期后,发送列地址,在此时刻数据信号才出现在数据线上。因此根据以上的比较分析,我们可以通过FPGA的设计使得DPRAM对于北桥来说运行于SDRAM情况之下,即北桥GT对DPRAM的操作符合SDRAM规范。

具体设计办法如下:在北桥GT对双端口RAM卡进行访问并发出行地址时,我们设计北桥同时选通FPGA,在经过FPGA内部的运算后,经过TRCD的延迟,在北桥向双端口RAM卡发出列地址及CAS的同时,FPGA发出运算后的合适的DPRAM高位地址(段地址)。此时,高位地址与低位地址将组合成为完整的DPRAM地址并同时到达DPRAM,然后再进行读写操作。从而实现在逻辑上北桥对DPRAM的访问操作等同于SDRAM。

在系统运行中,高7位段地址与北桥发出的列地址中的低8位DADDR[7:0]拼接为双端口静态存储器的完整地15位地址DPRAM_ADDR[14:0],完成对段内单元的访问。FPGA的控制功能还包括:判断DPRAM是否有数据及通知北桥数据可读,DPRAM是否写满及通知北桥放弃写过程,判断是否DPRAM已写到最后的地址及循环到起始地址等。FPGA还对北桥提供了L/R_SEG_FULL(A、B段写满信号)和L/R_INT_README(A、B段读允许信号),这些信号均连接到GT64240的MPP(multiple purpose pins) interface上,通过以上设计从而实现了基于总线的双通道循环缓冲区实时开关技术。

由于DPRAM实际可以认为是SDRAM的延续,而系统通过内部地址将其与系统内存SDRAM加以区分。而段地址的切换由FPGA控制完成,所以对于北桥来说,双端口RAM卡的地址空间大小为2KB。

通过对MIPS网闸双端口RAM卡的设计,在MIPS网闸中实现了基于SDRAM总线的双通道循环缓冲区实时开关技术。

采用SDRAM总线通道使得双端口RAM卡的地址作为内存的一段而存在,北桥GT对其的访问符合SDRAM规范,因此在MIPS网闸系统进行数据交换时,数据是由内存到内存的搬运,其速度比内存到PCI、Local Bus要快,而且方便以后的软件设计。而双端口RAM卡的FPGA控制单元独立工作保证了系统不会被嵌入式计算机或者其他主机远程控制,使得网闸系统获得绝对的安全性。采用新结构-双通道和循环缓冲区结构提高了系统数据传输的速度和实时性。同时双端口RAM卡的FPGA对ai、bi的控制管理实现了内外部处理单元对存储单元的互斥读写,实现了内外网数据的隔离。

通过采用新技术提高了MIPS网闸的数据交换速度,减少了读写冲突的发生。在本设计中,对通道的理论利用效率可以达到99%以上,而SDRAM的速度是133MHz,因此北桥对DPRAM访问的速度也达到了133MHz,那么MIPS网闸的交换峰值将达到133MHz×64bit×2(双向双片),这在性能上是很大的突破。

5.传输过程的控制

MIPS网闸系统中数据的处理流程如图5所示:

图5 系统数据处理流程

用户请求发送给服务器,服务器将收到的数据经确认后,通过专门的通讯软件发给MIPS网闸系统。MIPS网闸收到这些网络数据后,在MIPS嵌入式主机系统A上对它们进行内容过滤、身份验证、安全审计、病毒查杀,同时完成协议剥离,获得纯数据。然后将通过审核的纯数据写入内存地址中对应于双端口RAM卡地址区间。双端口RAM卡通过L/R_INT_README信号通知MIPS嵌入式主机系统B来读取数据。MIPS嵌入式主机系统B读取内存地址中对应于双端口RAM卡地址区间获得数据,然后将数据进行重新封装还原,形成一个安全的网络数据包,通过网络端口B发送给服务器。服务器根据该数据包的服务请求从而完成整个服务过程。

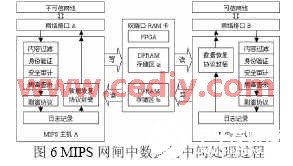

数据在MIPS网闸系统的中间处理过程如图6所示:

图6 MIPS网闸中数据的中间处理过程

6.结论

分析介绍了物理隔离网闸技术,提出了基于总线的双通道循环缓冲区实时开关技术,该技术克服了原有技术中存在的数据交换速度低实时性差的问题。给出了网闸中利用FPGA和双端口RAM在SDRAM总线上实现该技术的具体实现,对该系统中数据传输过程的控制和处理也给予了简要的说明。依据此技术设计实现的物理隔离系统的数据交换速度以及数据的实时性得到了提高,满足了千兆网络级的应用。

责任编辑:gt

-

基于FPGA的汽车尾灯控制电路设计与实现2011-11-10 0

-

FPGA毕业论文选题大全2012-02-10 0

-

低成本光纤隔离网闸方案,快速搭建物理隔离防火墙2014-11-19 0

-

基于软体逻辑的高可靠刀闸接口箱控制器的设计2018-10-18 0

-

一种基于双FPGA实现刀闸接口箱的高可靠性以及通讯控制的设计2019-06-06 0

-

怎么利用FPGA和CPLD数字逻辑实现ADC?2019-08-19 0

-

怎么设计一种基于CPLD的PWM控制电路?2021-05-08 0

-

哪位大侠有EEPROM的读写控制电路?或IP2021-06-25 0

-

低成本FPGA或CPLD实现节能型家电电机控制设计2021-07-14 0

-

MCU+CPLD/FPGA实现GPIO扩展与控制的资料大合集2021-11-04 0

-

基于单片机和CPLD的步进电机控制电路2022-04-02 0

-

双电源光耦隔离门极控制电路2009-02-09 1126

-

FPGA如何实现对高速AD转换芯片的控制电路2018-09-21 1653

-

如何使用CPLD和FPGA实现航空电源逆变控制电路2021-02-03 572

全部0条评论

快来发表一下你的评论吧 !