采用FPGA器件APEX20K1500E芯片实现TCAM的设计

可编程逻辑

描述

一、前言

网际协议(Internet Protocol) 是互联网进行网际互连的基础。随着互联网服务的快速发展,对网络的安全性提出了更高的要求,如何快速有效的过滤网络中的IP数据报文是一个始终需要解决的问题。

过滤IP数据报文是为了防止未授权用户访问内部网资源,同时限制网内用户非法使用外部服务。进行过滤之后,局域网内用户只能使用特定的服务(例如e-mail),网外的用户也只能访问经过授权的网内资源。由于网络带宽的飞速增长,传统的基于软件的查找算法已经不能适应网络速度的飞速发展,迫切需要采用新的硬件过滤方法,方案之一就是采用内容可寻址存储器TCAM(Ternary Content Addressable Memory)。

TCAM利用三个数值存储数据‘0’ 、‘1’ 、‘X’(不关心),每一个表项都包含数值比特串和掩码比特串。TCAM能够在一个硬件时钟周期内完成关键字的精确匹配查找,只需要输入关键字的内容,TCAM就会将此关键字与CAM中所有的表项同时进行匹配比较,最后返回匹配表项在TCAM中所对应的地址,如果存在多个匹配表项则返回地址最低的表项。目前主流的IDS(Intrusion Detection Systems),例如Snort,可以编写相应规则来完成实时协议分析、内容查找/匹配、对网络上的IP包登录进行测试等功能。我们可以把类似于Snort的规则应用到TCAM中,通过制定符合特定规则的表项,来实现IP数据报的匹配。当数据报在TCAM中能够找到相应的匹配项时,我们即认为它是合法的,否则予以拦截并送入后台作为异常报文处理。

为了实现快速查找,设计者必须在PCB板上添加一个独立的TCAM器件,这会增加片间延时,同时减少PCB板上的可用空间,从而降低电路板的系统性能。因此我们采用FPGA来实现TCAM,FPGA芯片采用ALTERA公司的APEX20K1500E。

二、用FPGA实现TCAM

APEX20KE系列芯片采用嵌入式系统模块(Embedded System Blocks)实现了片内CAM,能够提供比传统CAM器件更高的系统性能,同时支持Ternary CAM。其中,每个ESB能够实现32×32的CAM模块,级联多个ESB可以实现更宽更深的CAM。

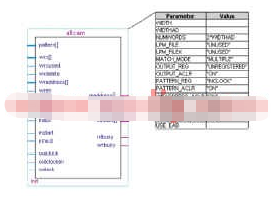

ALTERA公司的Megafunction库提供了altcam Megafunction,运用Quartus软件设计工具可以十分方便对TCAM进行读写操作。图1为altcam的结构图。

CAM可以在初始化配置时预加载默认表项,也可以在系统运行时对表项进行实时更新。在大多数情况下,写入一个数据表项需要两个时钟周期,当写入“X”(不关心)比特位时,需要三个时钟周期。

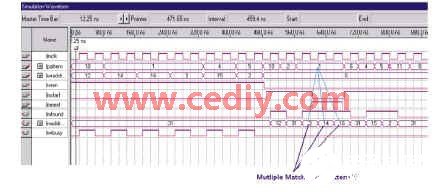

Altera CAM有三种不同的读模式:单匹配模式、多匹配模式和快速多匹配模式,其中单匹配模式适用于CAM里没有多个匹配项的情况。无论工作在哪种模式下,ESB都会输出匹配数据项的编码地址或未编码地址。当用未编码地址输出时,每条信号线对应CAM模块里的一个表项,当输出信号线为高时,表明对应的表项和输入数据匹配(例如,假如地址为15的表项数据匹配,则mbit[14]输出高电平)。通常情况下,在一个时钟周期内每个ESB最多完成16个表项的比对,因此在多匹配模式下,需要两个时钟周期才能完成CAM模块里所有表项的比

对。而快速多匹配模式仅使用每个ESB的一半空间(即16个表项),因此一个时钟周期就可以输出匹配表项的地址,大大提高了查找速度,但同时也耗费了大量的存储空间,限制了CAM

的总容量。图4展示了多匹配模式下的功能仿真波形图。

三、制定CAM表项规则

考虑到报头里包含了报文的地址和控制信息,我们可以从报头中提取某些域的值作为TCAM的匹配关键字。图5给出了CAM表项的一种配置方案。由于规则的不同,大多数的表项都

存储了大量的“X”(不关心)比特位,这是因为:

◆ 并不是IP数据报中所有对应域都需要同表项进行匹配。比如要拦截特定主机的IP包时,仅仅匹配源IP地址就足够了。

◆ 有时IP地址并不是指定一个特定的主机,而是代表一个网络或者一个包含多台主机的子网,这意味着表项的某些比特位必须是“X”(不关心)。

在CAM中能够找到相应的匹配项时,输入数据报可以顺利通过,否则予以拦截并作为非法报文处理。由于只需判断CAM里是否有匹配表项,而不关心具体表项的地址,因此存在多个匹配表项并不会影响比对的结果。在图5中,由于在CAM里找不到匹配表项,源地址为192.168.1.10的主机不能进行Telnet(23)服务。

虽然Snort给出了超过1400条配置规则,但通常并不需要同时应用所有的规则。Y. H. Cho提出了一种包含105条规则的IDS[3],因此大小为128×128的CAM足以满足绝大多数的需要。另外为了有效地进行比对,路由器输入端送来的报文要暂存在SRAM当中,管理这些报文需要对报文进行有效的地址分配,以便对报文进行相应处理。

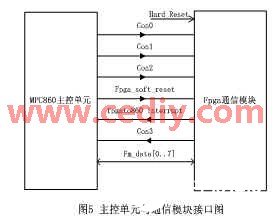

四、动态管理FPGA

为便于管理和动态更新,FPGA不仅要肩负对输入报文进行分类、过滤、提取关键字、进行高速查找等工作,还必须制定专门的通信模块负责与主控单元(实际采用MPC860)进行通信。通信模块起到对下进行数据接收,对上进行状态报告的桥梁作用,是主控单元同FPGA进行通信的接口,主要实现以下功能:

1、 监控系统的硬软复位信号,从而对整个系统进行复位。

2、 向主控单元发送状态报告。主要由主控单元请求获得,从而能够实时监控系统各模块的工作状态。

3、 将FPGA系统划分为正常工作模式和测试模式。FPGA存在两种工作模式,一种是正常工作模式,另一种是测试模式;在正常工作模式情况下,系统正常接收网络中的数据报文;测试模式条件下,系统处于测试状态,可以将内部测试信号送出以达到快速调试的目的。

4、 向主控单元提供错误报告。系统内部对一些关键部分设定监控程序,一旦有问题出现将迅速将错误信息传送给主控单元,从而方便对故障的检测。

5、 将主控单元的命令信息转发给相应模块,实现FPGA的动态更新。这样可以根据实际需要动态更新TCAM的表项,改变IP报文过滤规则。

五、总结

采用基于FPGA的CAM进行IP数据报文过滤是一种理想的选择。由于关键性的功能(搜索CAM)和一些非关键性的功能(改变CAM内容)分别在硬件和软件中实现,因此该设计具有高度灵活性,同时比纯软件过滤有更快的处理速度,在实际中可达到800Mbit/s.

表项宽度可变的CAM能够很好的应用Snort规则进行字符串匹配,同时可通过软件进行动态更新。此外,CAM模块大约只耗费了FPGA一半的存储资源,可以根据需要在FPGA内整合相关功能逻辑电路扩充电路功能。

责任编辑:gt

-

支持重构的FPGA器件2011-05-27 0

-

FPGA 等效门数的计算方法2012-03-01 0

-

FPGA中系统运行频率计算方法2018-08-21 0

-

CPLD/FPGA有哪些设计工具?2019-03-04 0

-

采用FPGA实现直接数字频率合成器设计2019-06-18 0

-

如何使用FPGA实现TCAM2020-06-11 0

-

请问怎么采用FPGA和集成器件来实现IJF编码?2021-04-13 0

-

采用AT89S2051单片机配合串行E2PROM存储器实现CPLD/FPGA器件的被动串行模式的下载配置2021-04-13 0

-

采用FPGA来实现SVPWM调制算法2022-01-20 0

-

TCAM路由更新的硬件优化2010-08-04 603

-

TCAM在高速路由查找中的应用及其FPGA实现2015-11-04 935

-

低成本的采用FPGA实现SDH设备时钟芯片技术2017-11-21 1863

-

可编程逻辑器件APEX20K的特点、功能及应用案例2020-11-12 2102

-

深度剖析TCAM基础知识2021-06-15 11420

全部0条评论

快来发表一下你的评论吧 !