基可编程逻辑器件实现滤波器分组级联系统的设计

可编程逻辑

描述

数字下变频(DDC)就是通过混频、抽取和滤波等步骤,降低射频带通采样信号或中频采样信号的采样频率,以保证后续DSP正常地进行基带信号处理。DDC是软件无线电系统的主要部分,它改变了通常的无线电设计,实现数字域的下变频。同时,数字下变频又是数字处理运算量最大、速度要求最高的部分,也是最难实现的部分。文献[1]对DDC的各功能模块的高效算法并对各类滤波器的合理分组级联进行了研究、提炼与总结,并将各算法融为一体,从软件实现的角度通过滤波器的分组级联完成了对系统的搭建。但没有针对特定的硬件给出系统的具体实现,在实际实现时,往往面对算法实现实时性不够,硬件所需乘法器太多的弊端,难以达到系统要求的指标。

另一种思路就是避开完全用软件实现DDC,转而采用软硬件相结合的方式进行,把计算量最大的数字下变频和抽取系统用专门的硬件芯片实现,其原理仍然通过多类滤波器的分组级联实现。尽管目前的硬件DDC芯片已经可以达到很高的性能要求,但终究与软件无线电的思想相悖,不能实现或者不能完全实现平台通用,更新升级方便等功能。

目前针对数字下变频,除了采用多片DSP组成并行处理模块外,一般都探索采用下变频处理的高效算法。本文针对这些高效算法做了总结,进行合理的分组级联并引入流水线技术以便于在FPGA上实现。

2 滤波器的分组级联技术

抽取滤波器组通常由乘法器和加法器阵列实现。FPGA进行实现时,依靠内嵌的DSP模块完成乘法器和加法器/累加器运算,为了节约FPGA的有限的DSP模块资源,设计面临的最大挑战是克服需要大量乘法器的弊端。

如果将FIR抽取滤波器分解成多个独立滤波器,在满足系统性能要求下,又可以有效减少实现整个滤波器所需的抽头总数。同时,多组滤波器进行分组级联后,便于进行流水线处理,同时由于越靠后级,信号速率越低,便于进行分时复用,这些可以有效减少乘法器需求。

由文献[4]的分析,CIC滤波器的系数全为1,可以变滤波运算的加乘法为全加,FPGA实现时,只需进行累加运算;只要FPGA的工作频率能达到信号速率即可,所以CIC滤波器特别适合于DDC的第一级。

HB滤波器一半左右的系数为0,经过第一级CIC滤波器的抽取后,信号速率已经降低很多,此时采用HB滤波器,可以再减少一半左右的乘法器需求。因此适合作为CIC抽取滤波后的一级。

信号经过CIC,HB滤波抽取,信号速率相对来说已经很低,此时能够进行更高阶的FIR滤波,使得滤波器的通带波动、过渡带带宽、阻带最小衰减等指标符合系统要求。同时有效降低了对乘法器的要求,便于进行分时复用。

3 滤波器的分组级联技术优化

由FIR理论知:要满足基本的滤波器衰减和噪声特性要求,抽取系数为N的单个滤波器需要大量的抽头(乘法器)才能实现。最新的Virtex-5系列FPGA内嵌的DSP48E模块(主要包含硬件乘法和加法单元,能在一个时钟内完成乘法和加法操作)的最高工作频率是550 MHz,而Virtex-5 LX330T提供了多达192个DSP Slice,但考虑到FPGA还需完成后级的信号处理和解调,仍然有必要尽量减少系统对乘法器的需求。

3.1 对称的滤波器系数

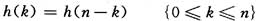

系数对称的DDC抽取滤波器可以用来获得最多50%的乘法器节省效果。在对称条件下,n个抽头的FIR滤波器系数h(0),h(1),…,h(n)满足:

由于h(k),h(n-k)与两个相关数据之和的乘积可以一次完成,因此所需乘法器的数量可以最多减少2倍(对于偶数个系数)。在FPGA中,可以利用低资源消耗的进位链逻辑实现使用相同系数的两个数据的加法。

3.2 利用EBR存储器块实现FIR滤波器

FPGA的嵌入式RAM块存储器(EBR)可以用来存储滤波器系数,对于DDC这种乘法器密集型应用来说,将存储器和LUT结构资源用作乘法器可以显著提升实现效率。样本被串行移位进EBR地址总线。在EBR内部有一个预计算的结果乘法表以及带合适系数的各个输入样本比特(地址比特)总和。累加器将累加n(n是样本比特分辨率)个中间结果,并在n个时钟周期后提供完整的FIR滤波结果。

3.3 流水线技术

在CIC滤波器中,由于滤波器的实质为积分器和微分器的级联,在进行滤波时,引入流水线技术后,后级微分器在处理数据的同时,下一组数据已经送入前级积分器处理。在正确时序的组织下,使信号的处理速度提高了一倍。在后级的FIR滤波中,由于信号速率显著降低,同样可以进行分时复用实现流水线技术。

其实现方法为:对输入时钟进行计数,得到一个时钟2分频的信号rdy,当rdy为1时,输入的中频信号和DDS产生的正弦波相乘;当rdy为0时,输入的中频信号和DDS产生的余弦波相乘,相乘后经过滤波器输出。由于滤波器采用了二级流水线技术,使得只用一套硬件实现了两路信号的处理,达到节省乘法器资源的目的。

4 数字下变频(DDC)的FPGA实现

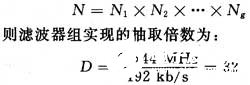

给定设计任务:实现对输入信号为6.144 MHz,信号输出的速率为192 kb/s的AM,FM及数字信号的解调,一个抽取系数为N的大型FIR抽取滤波器可以分解成N个抽取系数分别为N1,N2,…,Ns的较小、较简单的级联滤波器。抽取系数满足以下等式:

在考虑各种滤波器的特性基础上,抽取系统采取多级抽取组分组级联的方式。为了有效利用FPGA资源,采用16倍CIC滤波器和一级半带(HB)滤波器,最后接FIR滤波器进行整形补偿。其实现方框图如图1所示。

4.1 CIC滤波器的设计

因为CIC滤波器的系数全为1,FPGA实现时只需进行累加运算,而加法器是在FPGA的内核逻辑中实现的,通过使用丰富的逐位进位模式(ripple mode)的通用可编程逻辑单元(PLC)片,可以达到很高的频率。

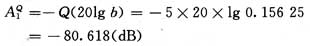

根据本次的设计要求,为了获得更高的带宽,设通带截止频率fc1=B=60,抽取倍数为16,输入采样频率为6.144 MHz,则带宽比例因子b=B/(fs1/D)=0.156 25,系统采用5级级联的方式,此时阻带的衰减为:

但是带宽比例因子和通带内容差是一对无法调和的矛盾,为了更大的带宽,付出的代价就是使得通带内容差为:

说明多级级联增大了阻带衰减,减小混叠影响的同时也增大了带内容差。

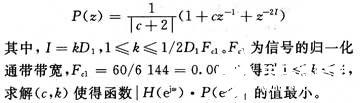

因此,上述参数设计的CIC滤波器带内纹波太大,必须设法进行补偿。采用内插多项式ISOP滤波器,其转移函数为:

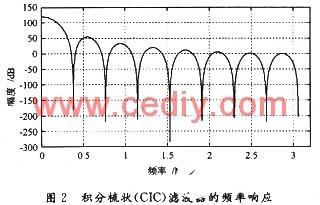

综上所述,选用5级级联的CIC滤波器后接一级ISOP滤波器,CIC采用5个6.144 MHz的积分器和5个工作在384 kHz的微分器通过流水线组成,积分器采用累加器实现,微分器采用全减器实现,中间连接一个16倍的抽取机构。通过判断数据是否已经在积分器内处理完毕送微分器后,下一组数据即进入积分器,实现二级流水线技术。图2为用Matlab仿真滤波器的频率响应。

4.2 半带滤波器的设计

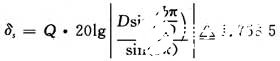

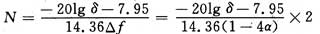

HB滤波器的通带截止频率设为fc1=B=120 kHz,输入采样频率为fs1=768 kHz,使用Matlab的滤波器设计工具,根据文献[2]推导,采用凯撒窗设计半带滤波器所需的阶数N:

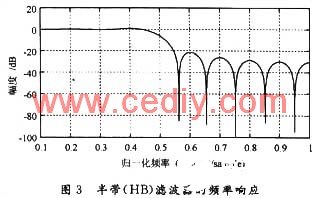

式中,α为由半带滤波器通带带宽确定的比例系数,δ为阻带衰减,取δ=0.001(6 dB),实际设计中,经计算归一化通带截止频率为fc=120/768=0.156 25,阻带起始频率为fA=0.5-0.156 25=0.343 75,得到过渡带宽为△f=fA-fc=0.187 5,代入上式,求得N=20。用Matlab求出滤波器系数,在FPGA中作为查询表实现,其频率响应如图3所示。

5 软件仿真及分析

本文通过ISE9.1i进行Verilog程序的编写后,进行软件仿真。

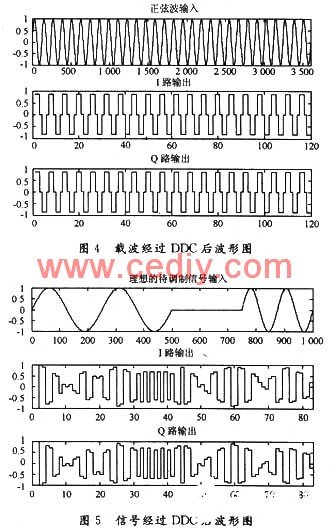

输入如图4所示的6.144 MHz的正弦波信号作为载波信号,输入的待调制信号如图5所示,输入384 kHz的两个周期的正弦信号,经一定延时后,再输入192 kHz的两个周期的正弦和余弦两路正交载波,由于ISE9.1i自带仿真器不利于观察数据的具体波形,图4和图5为Matlab从仿真器中读出数据后绘制的波形图。

可见载波波形和输出的信号波形都发生了严重变形,但根据乃奎斯特原理知:这并不影响后续数字信号的处理。从仿真波形可以得出下变频模块的功能完全正确。

6 结语

通过对数字下变频原理的深入介绍,针对系统的设计要求,对数字下变频的滤波器进行优化设计后,通过对滤波器的级联和分解,在不同的信号速率下彩不同的滤波器,并引入流水线技术,从而有效减少FPGA乘法器开销,最后在Virtex-5 FPGA上高效实现了系统的全部功能,达到了系统的设计要求。

在日记本:gt

-

可编程逻辑器件2014-04-15 0

-

可编程逻辑器件发展历史2019-02-26 0

-

可编程逻辑器件是如何发展的?2021-04-29 0

-

怎么采用可编程逻辑器件设计数字系统?2021-04-29 0

-

PLD可编程逻辑器件2021-07-22 0

-

可编程逻辑器件设计2006-03-25 986

-

可编程逻辑器件基础及应用实验指导书2010-03-24 568

-

什么是PLD(可编程逻辑器件)2009-06-20 15170

-

EDA技术与应用(可编程逻辑器件)2012-05-23 852

-

可编程逻辑器件(书皮)2022-07-10 357

-

可编程逻辑器件的分类有哪些2020-06-10 27091

-

电可编程逻辑器件EPLD是如何设计的2022-08-22 974

-

可编程逻辑器件测试2023-06-06 430

-

什么叫可编程逻辑器件 可编程逻辑器件有哪些特征和优势?2023-09-14 1367

-

可编程逻辑器件的特征及优势科普2024-02-26 621

全部0条评论

快来发表一下你的评论吧 !