高速 ADC 咋有这么多不同的电源轨和电源域呢?

描述

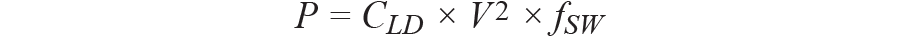

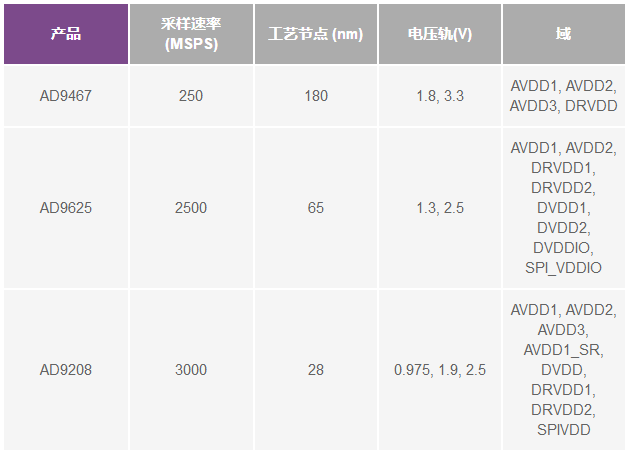

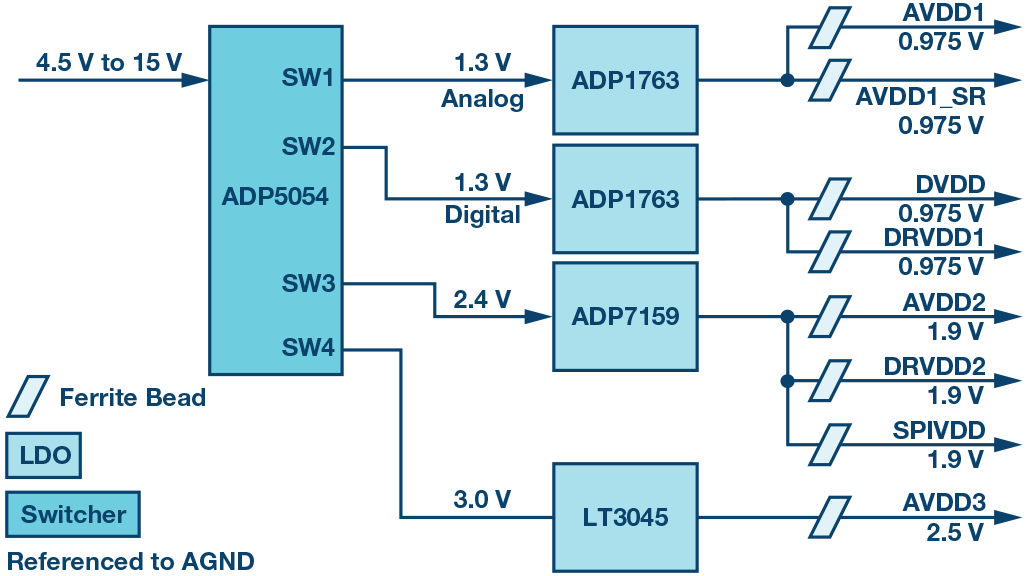

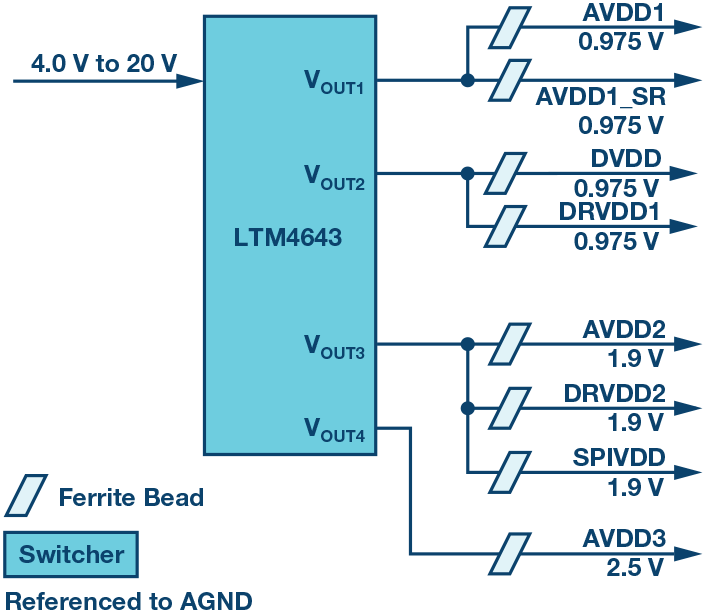

在采样速率和可用带宽方面,当今的射频模数转换器(RF ADC)已有长足的发展。其中还纳入了大量数字处理功能,电源方面的复杂性也有提高。那么,当今的RF ADC为什么有如此多不同的电源轨和电源域?

|

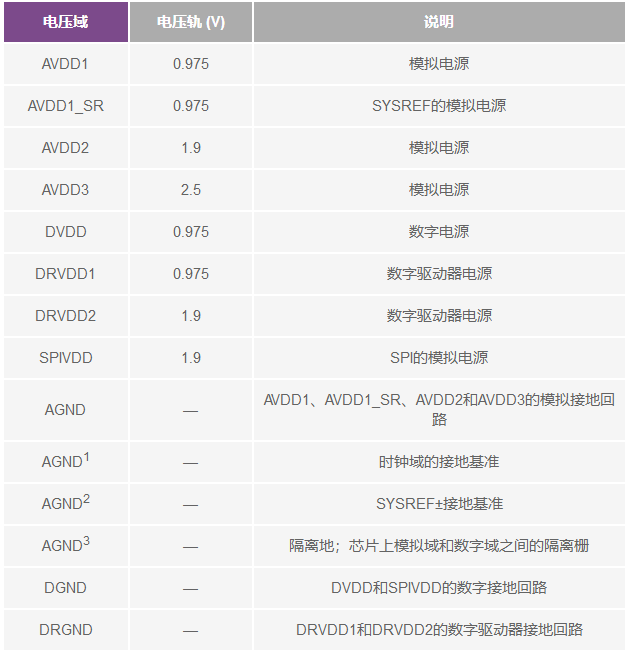

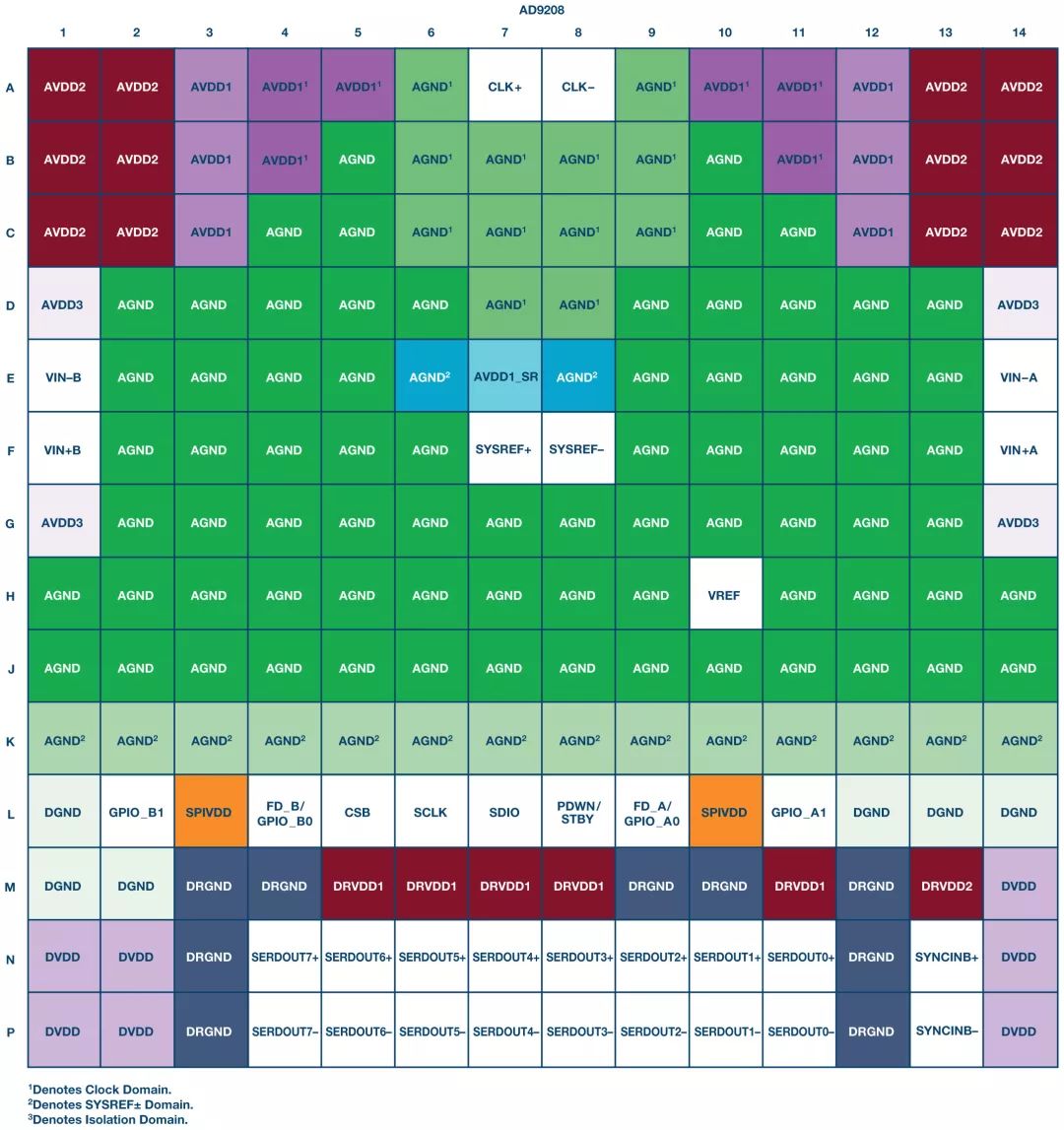

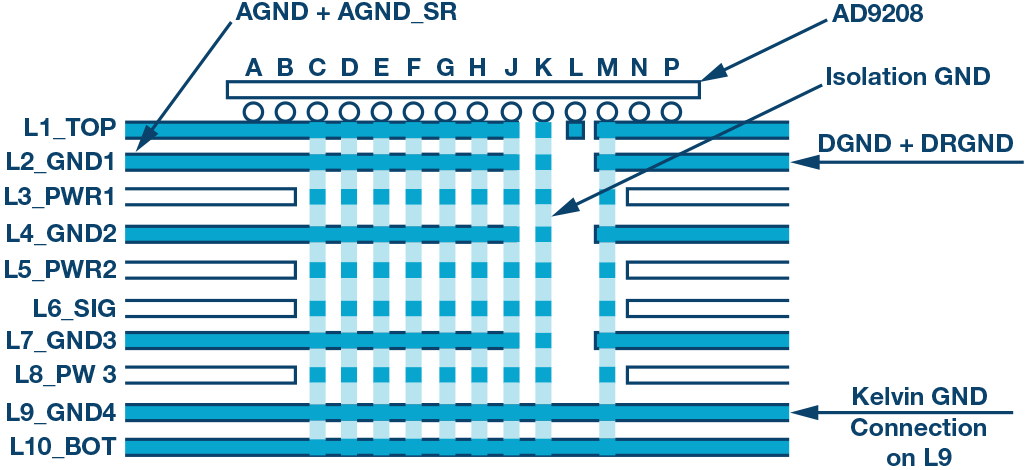

绝对不是。仅仅因为AD9208数据手册显示了所有这些域,并不意味着它们在系统板上必须全部分离。了解系统性能目标和ADC目标性能对优化ADC的PDN起着重要作用。在电路板上使用智能分区以减少不必要的接地回路,是将各个域之间的串扰降到最低的关键。适当地共享电源域,同时满足隔离要求,将能简化PDN和BOM。

-

支持每线高达 16 Gbps 的线速

-

SFDR = 70 dBFS -

SNR = 57.2 dBFS

-

SFDR = 78 dBFS -

SNR = 59.5 dBFS

-

48 位 NCO -

4 个级联半带滤波器

-

具有除以 2 和除以 4 选项的整数时钟 -

灵活的 JESD204B 线配置

-

JESD204B(子类 1)编码串行数字输出 -

3 GSPS 时每通道的总功率为 1.65 W(默认设置) -

−2 dBFS 幅度、2.6 GHz 输入时的性能 -

−9 dBFS 幅度、2.6 GHz 输入时的性能 -

集成式输入缓冲器 -

噪声密度 = −152 dBFS/Hz -

0.975 V、1.9 V 和 2.5 V 直流电源供电 -

9 GHz 模拟输入全功率带宽 (−3 dB) -

用于高效 AGC 实施的幅度检测位 -

每个通道具有 2 个集成式宽带数字处理器 -

相位相干 NCO 切换 -

提供多达 4 个通道 -

串口控制 -

片內抖动

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

- 相关推荐

- adc

-

高速ADC电源设计2018-09-26 0

-

高速ADC电源域2018-10-30 0

-

为什么有这么多不同类型的端口用于高速串行通信2019-02-19 0

-

电压监控ADC系统中,如何设计好电源域隔离?2019-02-25 0

-

高速ADC有多个不同的电源轨和电源域的原因2019-07-19 0

-

为什么高速ADC的电源域多2020-04-30 0

-

RF ADC为什么有如此多不同的电源轨和电源域?2021-03-11 0

-

为什么有这么多编程语言呢2022-01-12 0

-

安卓8.0最新消息:安卓8.0初体验,竟然这么流畅还有这么多黑科技功能2017-04-13 3568

-

RF ADC为什么有如此多不同的电源轨和电源域?2018-06-22 5937

-

小垫圈,里面还有这么多名堂……2019-07-02 2370

-

选AC-DC电源适配器还有这么多门道?看完才知道2019-07-02 5562

-

为什么高速ADC会有这么多的电源轨和电源域2021-01-08 648

-

高速ADC为啥有这么多不同的电源轨和电源域2020-12-29 302

-

高速ADC电源域2023-02-16 864

全部0条评论

快来发表一下你的评论吧 !