ADC 带宽与模拟抗混叠滤波器误差源

模拟技术

描述

生活环境周围信号万万千,对于一个嵌入式 er。我们利用技术去了解世界、改变世界。而一个产品要与外界物理环境打交道,一个至关重要的触角就是采样真实模拟世界的信号,翻译成芯片可理解的数字信号,进而实现很多为人服务的应用产品。那么提到采样,ADC 技术你绕不开,今天总结分享一下 ADC 的点点滴滴。

啥是 ADC

在现代电子工业技术中,模数转换器(ADC, A/D,或 A-to-D)是一种将模拟信号转换成数字信号的系统。ADC 还可以提供隔离的测量,例如将输入模拟电压或电流转换为表示电压或电流大小的数字的电子设备。通常情况下,数字输出是一个与输入成比例的二进制补码,但也有其他的可能性。举些栗子:

KTV 中麦克风将你唱歌的声音转成数字音频信号,经由信号处理,功放再播放出来

数码相机将物体表面反射的光线转换为数字信号,从而成像

疫情期间必用物资额温枪,将人体红外辐射经由光电转换成电压,最终转换为数字信号进行温度显示

举不胜举。

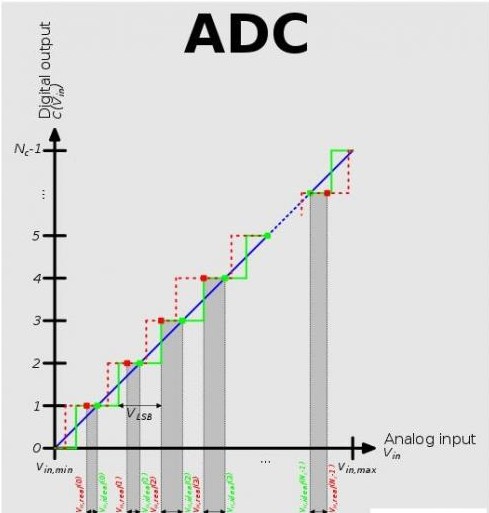

ADC 将连续时间和连续幅度的模拟信号转换为离散时间和离散幅度的数字信号。转换涉及输入的量化,因此必然会引入少量的误差或噪声。此外,ADC 不会连续执行转换,而是定期进行转换,对输入进行采样,从而限制了输入信号的允许带宽。

ADC 的性能主要由其带宽和信噪比(SNR)来表征。

ADC 带宽(Band width):ADC 的带宽主要由其采样率来表征。

ADC 的 SNR:SNR(signal noise ratio)是指信噪比,受许多因素影响,包括分辨率,线性度和准确性(量化级别与真实模拟信号的匹配程度),混叠和抖动。ADC 的 SNR 通常以其有效位数( effective number of bits:ENOB),它返回的每个度量的位数平均来表示,而不是噪声。理想的 ADC 的 ENOB 等于其分辨率。

故,选择 ADC 以匹配待数字化信号的带宽和所需的 SNR。如果 ADC 的采样率大于信号带宽的两倍,那么根据 Nyquist–Shannon 采样定理,就可以实现完美的重构。量化误差的存在甚至限制了理想 ADC 的 SNR。但是,如果 ADC 的 SNR 超过输入信号的 SNR,则其影响可能会被忽略,从而导致模拟输入信号的本质上是完美的数字表示。

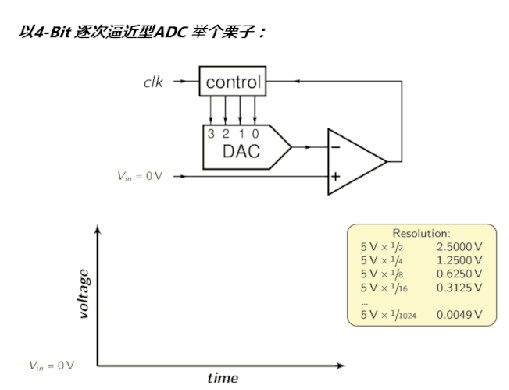

整这么多文字还是不直观易懂,到底啥是 ADC:

须理解的指标

分辨率

非线性度

实际使用的 ADC 除了上面说的量化误差外,还具有更多的误差源:

差分非线性误差 DNL(Differential Non-Linearity):当 ADC 输出在应该改变的时候没有改变,就会出现 DNL 误差。例如,假设给定输入的当前输出代码是 01101100,并且输入值增加了半步量化。代码应该是 01101100 + 1 位,或者 01101101。当输入电压低于当前输入电压时,也会发生相反的情况。此时由于种种原因,这种情况可能不会发生。在本例中,ADC 的误差为±1 位 DNL。

积分非线性误差 INL(Integral Non-Linearity):如果量化水平在整个输入范围内分布不均匀,就会出现 INL 误差。例如,某 ADC 具有 12 位(4096 个计数)分辨率和 4.096V 的参考电压。每个比特数正好表示输入电压变化的 1.000mV,因此,输入电压为 4096 mV,输出电压为 1111 1111 1111,即 0xFFF。对于某些 adc,输入 4095mV,甚至 4094mV,仍然会得到 0xFFF 的数字输出。实际情况是,在整个输入范围内,1 位的值发生了非常微小的变化,比如 1.001mV 或 0.999mV。积累的误差会导致一个或两个比特精度的全量程误差。

在为特定应用指定 ADC 时必须考虑这些因素。

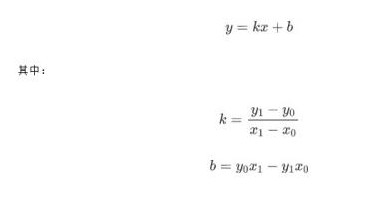

所有 ADC 都存在由其物理缺陷引起的非线性误差,导致其输出偏离其输入的线性函数(或其他函数,在故意使用非线性 ADC 的情况下)。这些误差有时可以通过校准来减轻,或通过测试来避免。所谓校准,比如可以通过量点线性校准,假定 y 为 ADC 数值,x 为输入模拟电压:

应用实施策略:将上述 k/b,利用两个点进行校准,将校准数据 k/b 存储在非易失存储器中。补充说一下:工程实践中需要校准的原因还因为选取的外围电阻、电容器件都有误差,所以这也是另一个需要标定的重要原因。

采样率

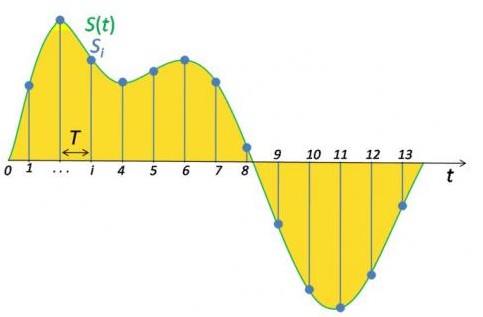

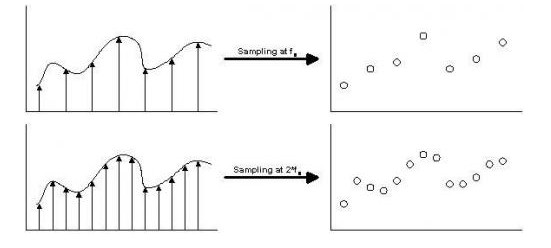

模拟信号在时间上是连续的,因此有必要将其转换为数字序列,这是数字信号处理的基础。因此,需要定义从模拟信号中采样数字序列的速率。该速率称为转换器的采样率或采样频率。可以采样连续变化的带限信号,然后可以通过重构滤波器从离散时间值中再现原始信号。奈奎斯特 - 香农采样定理表明,只有当采样率高于信号最高频率的两倍时,才可以忠实再现原始信号。个人在使用时,一般会选 4 倍以上。

由于实际的 ADC 不能进行瞬时转换,因此在转换器执行转换期间(称为转换时间)输入值必须保持恒定。一个被称为采样保持电路——在大多数情况下,它使用一个电容来存储输入端的模拟电压,并使用一个电子开关或栅极来断开电容与输入端的连接。许多 ADC 集成电路包括内部的采样保持电路模块。图中的 T 为采样周期,其倒数就是采样频率。

混叠

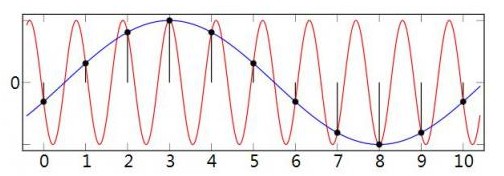

ADC 通过在不连续时间间隔(离散的含义)内对输入值进行采样来工作。假设以高于奈奎斯特速率的频率对输入进行采样(定义为有用信号频率的两倍),则可以重构信号中的所有频率。如果对高于奈奎斯特速率一半的频率进行采样,则会将它们错误地检测为较低频率,这一过程称为混叠。之所以会出现混淆,是因为每个周期对函数进行两次或两次以下的瞬时采样会导致丢失周期,从而出现频率错误地降低的情况。例如,以 1.5 kHz 采样的 2 kHz 正弦波将重构为 500 Hz 正弦波。

为了避免混叠,ADC 的输入必须经过硬件低通滤波,最简单的实现形式为一阶无源 RC 滤波网络,以去除采样率一半以上的频率。这种滤波器被称为抗混叠滤波器,它对于实际的 ADC 系统至关重要,该系统适用于具有更高频率内容的模拟信号。在需要防止混叠的应用程序中,可以使用过采样来大大减少甚至消除混叠。

例如:六种不同采样速率采集的数字序列重建的 4 种波形。其中两种波形在采样率足够情况下未出现混叠。另外两个说明了在较低速率下会失真(混叠增加)。

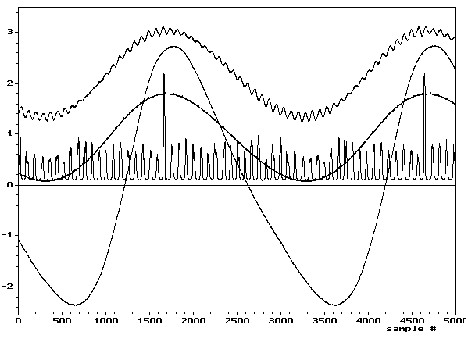

过采样

为了经济起见,通常以所需的最小速率对信号进行采样,结果是引入的量化误差是 白噪声在转换器整个通带上的扩散。如果以远高于奈奎斯特速率的速率采样信号,然后进行数字滤波以将其限制为信号带宽,则会产生以下优点:

过采样可以更轻松地实现模拟抗混叠滤波器

降低的噪声,尤其是在过采样之外还采用噪声整形处理后。

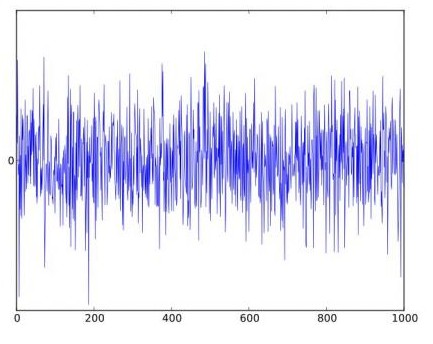

白噪声长啥样?

过采样通常用于音频 ADC 中,与典型晶体管电路的时钟速度(》 1 MHz)相比,所需的采样率(通常为 44.1 或 48 kHz)非常低。在这种情况下,可以以很少的成本或不增加成本就可以大大提高 ADC 的性能。此外,由于任何混叠信号通常也都在频带外,因此使用非常低成本的滤波器通常可以完全消除混叠。下图比较直观,可以看出提高采样频率,可以更为真实的重建原始信号,而采样频率低些,对于信号的细部则无法准确重建。

总结一下

在单片机、DSP 信号处理系统中,我们免不了要对物理信号进行采样,需要运用到模数转换器件,模数转换器万万千,那么要用好 ADC 器件,或者使用单片机、DSP 内置 ADC,了解这些技术指标以及其描述的真实含义,是非常必要的。

责任编辑:pj

-

DSP的ADC前端除了有抗混叠滤波器还有什么??2012-10-14 0

-

无源抗混叠滤波器设计2015-04-23 0

-

关于ADC前端抗混叠滤波器的问题2016-11-17 0

-

抗混叠滤波器设计的3条指导原则2018-09-05 0

-

ADC应用领域中的混叠简介2018-09-06 0

-

Acc的顺序抗混叠滤波器是什么?2018-09-11 0

-

请问抗混叠滤波器的使用场合2018-10-09 0

-

请问如何设计一阶无源抗混叠滤波器2018-11-14 0

-

利用开关电容滤波器实现抗混叠滤波2019-01-02 0

-

ADS1675的delta-sigma (ΔΣ) 是用做抗混叠滤波器吗?2019-05-22 0

-

用于抗混叠应用的开关电容低通滤波器2019-07-08 0

-

抗混叠滤波器:将采样理论应用于ADC设计2020-09-18 0

-

请问如何利用开关电容滤波器实现抗混叠滤波?2021-04-23 0

-

ADC的过采样与抗混叠滤波器2021-08-04 0

-

根据数据表设置了适当的寄存器,LSM6DSL抗混叠滤波器没有起作用的原因?2022-12-15 0

全部0条评论

快来发表一下你的评论吧 !