基于数字信号处理器和和DA转换芯片实现4FTSK调制

描述

1 引言

短波通信是通过电离层反射来实现远程信息传输,因而其通信受地形限制小;其次通信成本低,灵活性强。但它也存在一些缺点,如:信息传输的可靠性差,存在深衰落和多径时延失真等。在一般在短波信道中传输数据,信息的误码率通常在10-2-10-3的数量级,这些严重的衰落以及多径效应造成的码间串扰,限制了通信质量的进一步提高。近年来,由于在短波数据通信系统中,采用了各种有效的抗衰落和抗多径的措施,使系统的误码率差不多提高了两个数量级。其中,时频组合调制技术(即FTSK)是目前广泛采用的抗衰落和抗多径技术之一。针对这种情况,本文提出采用DSP(数字信号处理器)实现4FTSK调制,并取得较好的效果。

2 4FTSK调制方式

在一个或一组二进制符号的持续时间内,用若干个调制频率的组合来传送原二进制数据流,每一个调制频率在不同的时隙内有不同的频率,这种由不同时隙和不同频率所构成的信号,称为“时频调制信号”;在某种意义上又可看成是一种时频编码调制,组成的系统称频率分集接收系统,即按一定的规则在数据符号的不同时隙发射不同频率信号来实现信号传输的调制方式。FTSK又可分为几种调制方式,包括二时二频制,二进制四时四频制,四进制四时四频制、八进制四时四频制以及十六进制相位调制等。

FTSK码组的编码原则是,所编码组既具有强的抗衰落和抗干扰能力,又容易实现同步,也就是要求编出能从信息序列中提取同步信息的正交码组。首先,为了提高抗衰落能力,要求每一个码组的不同时隙中应含有不同的频率。这样,二时二频基本上具有二重频率分集的效果,而四时四频基本上具有四重频率分集的效果;其次,为了加强抗干扰性,任何两个码组的码距应最大,所以首先要选用正交码,即要求所有的码组在同一时隙内含有不同的频率,对于四时四频制而言,在表示四进制信息时,很容易形成正交码,但表示八进制信息时,只能形成部分正交的码组;最后,在码组配置时还应考虑从码组本身能提取同步信息,即要求编码方式是非循环码,且任何两个码组都没有相同的二联码或三联码。

表1 各种调制方式性能比较

由表1可以看出,从性能而言,“四进制四时四频制”是最好的。对于4FTSK调制,我们选用正交编码方式,如表2所示

表2 4FTSK编码方式

3 系统的实现

由于本设计的主要目的是利用软件及简单的硬件实现4FTSK调制,并且力求产生的信号精确,故系统选用了当今比较流行的数字信号处理器(TI公司的TMS320C5402)和一片D/A(CA3338)转换芯片,用汇编语言编程实现调制信号输出。

3.1 TMS320C5402特点

TMS320C5402是TI公司TMS320家族的定点DSP(数字信号处理器)芯片。DSP可广泛应用于雷达信号处理,无线通信,语音信号处理等。实际上,DSP技术在工程应用中,就是要用数字信号处理的方式实现系统的功能。

DSP器件采用了与传统微处理器系统不同的总线结构,同时增加了硬件运算单元,把软件计算变为硬件计算处理,因此极大地提高了系统的数字处理速度。

C5402的CPU通过使用改进的哈佛结构,实现了高度的并行运算能力。同时,多种寻址模式和完善的指令提高了整个系统的性能。C5402主要有以下特点:

增强的哈佛结构,四条地址总线和四条数据总线。

高度并行的先进CPU设计,性能更好的面向应用的硬件逻辑。

为快速算法和高级语言优化设计的专用指令集。

标准化的模块结构,适于快速开发。

先进的IC处理技术,提高了性能,降低了电源消耗。

3.2 CA3338芯片性能

CA3338是HARRIS公司推出采用CMOS工艺制成的高速数模转换器,最高工作频率可达50M。它可以采用单电源+5V供电,并且能产生“轨对轨”的输出。

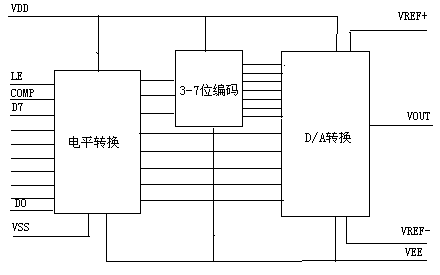

CA3338内部采用改进的R-2R梯形电阻网络,对高三位进行3位-7位的线性热编码来驱动7位加权电阻,这样,减少了由于输出电压值的改变产生的寄生电压。其内部功能框图如图1所示:

图1 CA3338功能框图

LE是片选信号,低电平有效。

D0-D7是数字信号输入端;COMP控制是否对输入信号的电平取反,高电平有效。

VREF+及VREF-是参考电压。

VDD接+5V电源,VSS是数字地,VEE可以接模拟地也可以接负电压。电平转换部分就是将输入电压范围在VDD和VSS之间的数字信号转

换到电压范围为VDD和VEE之间。

VOUT是输出的模拟信号。

3.3系统的硬件组成

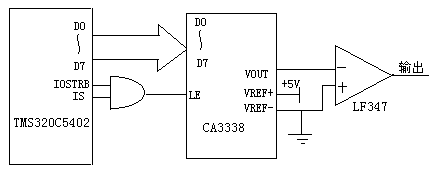

系统的硬件电路框图如图2所示。TMS320C5402的IOSTRB和IS相或后作为CA3338的片选信号,通过数据总线将数据送到CA3338中,D/A转换后的模拟信号经过运算放大器后输出。

图2 硬件框图

3.4系统的软件设计

3.4.1一个周期的正弦波的产生

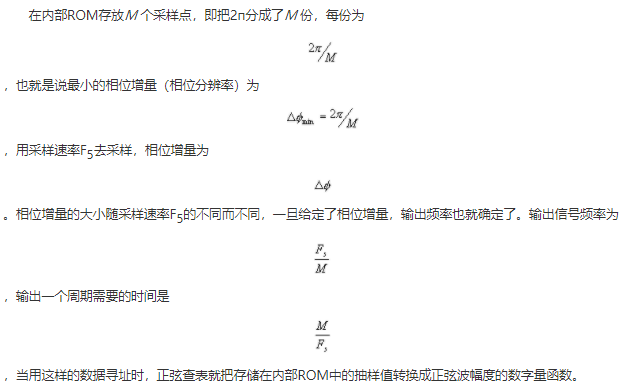

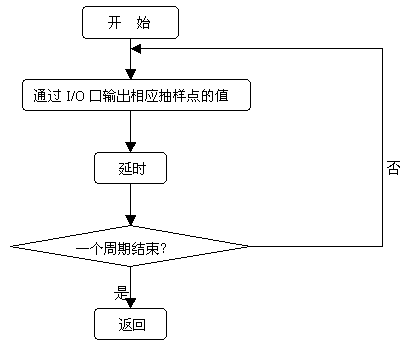

首先,在DSP内部ROM开辟一段存储空间作为一个周期的正弦波抽样点存储器。通过软件对该存储器进行相位-幅值的转换,从而在给定的时间确定相应的输出幅值。流程图如图3所示,具体是这样实现的:

上面讨论可以看出,可以产生的频率范围受采样率和存储器内采样点的个数的影响。在这里,采样率是软件设计的,即利用不同的延时程序实现不同的采样率。根据奈魁斯特抽样定理,一个频谱受限信号要想从抽样信号中无失真的恢复出原连续信号,抽样间隔必须不大于1/2Fm(Fm为最高频率,在这里Fm即为正弦波的频率F)或者说,最低抽样频率为2F。因此,M应该》=2。但M越大,得到的波形越好。通常情况,为了得到比较好的波形,我们取M》=8。在M一定的情况下,提高F5可以提高输出的最高频率。

图3 发送一个频率的正弦波流程图

3.4.2 4FTSK信号的产生及输出

4FTSK信号包含4个频率的波形,因此先根据不同的频率,计算出相应的采样率,编写产生这四个频率正弦波的子程序。在主程序中,判断要调制的码元,决定发送的4个频率的顺序。信号最终是通过I/O口输出到D/A转换芯片中实现从数字量到模拟量的转换。

4 结论

本文采用DSP和DA转换芯片实现4FTSK的调制。由于DSP的运算速度很高,采样率Fs有很宽的动态范围,因此它可以在很宽的频率范围内输出幅度平坦的信号。同时,该系统易于集成、易于调整,输出不同的频率只需要软件设置不同的采样率。这种方式在相对带宽、频率转换时间、相位连续性以及集成化等一系列性能指标方面具有较高的水平,为系统提供了优于模拟信号源的性能。该系统不仅可以实现FTSK调制,也可以通过预置相位累加器的初始值,精确地控制合成信号的相位,实现其他数字调制方式,如DPSK调制等。

责任编辑:gt

-

利用FPGA怎么实现数字信号处理?2019-10-17 0

-

哪位大神关于《数字信号处理与数字信号处理器》的DSP论.....2014-05-27 0

-

数字信号调制芯片2017-07-22 0

-

数字信号处理器的特点2020-12-09 0

-

关于DSP数字信号处理技术 精选资料分享2021-07-28 0

-

使用高速DA芯片实现数模转换的方法2022-01-18 0

-

数字信号处理MATLAB版资料分享2023-09-28 0

-

了解数字信号处理器2009-07-27 438

-

定点数字信号处理器(DSP)技术与应用2010-04-07 515

-

DSP芯片外围电路典型设计(数字信号处理器芯片TMS320F2007-08-15 4284

-

数字信号处理器中D/A功能的实现2009-07-11 1092

-

数字信号处理器(DSP)2010-01-04 3422

-

什么是数字信号处理器以及它的用处2019-08-26 4448

-

数字信号处理器(DSP)简介2022-08-02 15809

-

数字信号处理器概论2023-08-07 690

全部0条评论

快来发表一下你的评论吧 !