数字电路中二进制同步计数器实验原理及过程

模拟技术

2282人已加入

描述

一。实验要求

1.1.实验目的

- 认识二进制同步计数器的定义、工作状态及信号波形;

- 熟悉基于JK触发器实现二进制同步计数器的构成规则。

1.2.实验器材

- VCC

- Ground

- 脉冲电压源

- 上升沿触发JK触发器

- 2输入与门

- 四输入七段数码管

- 四通道示波器

1.3.实验原理

计数模值M和触发器级数k的关系:M=2k。

加法计数器的构成规律:

J0=K0=1

Ji=Ki=Q0•Q1•…。 •Qi-1 i=1、2…。。(k-1)

减法计数器的构成规律:

J0=K0=1

Ji=Ki=Q0‘•Q1’•…。 •Qi-1‘ i=1、2…。。(k-1)

1.4.实验内容、要求及过程

实验要求:

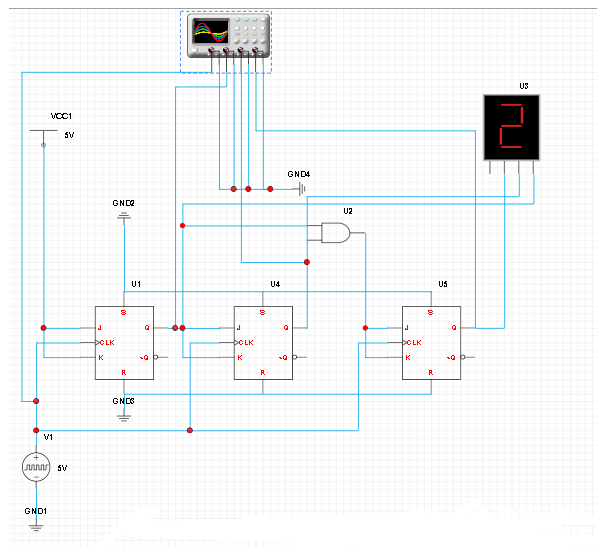

构建图1电路。时钟clk为0~5V,周期1s,高电平时长500ms。

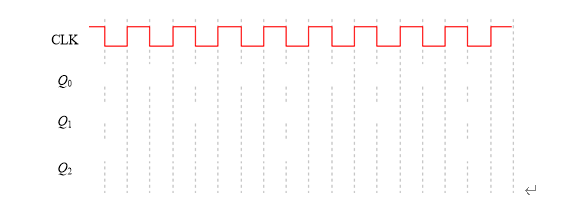

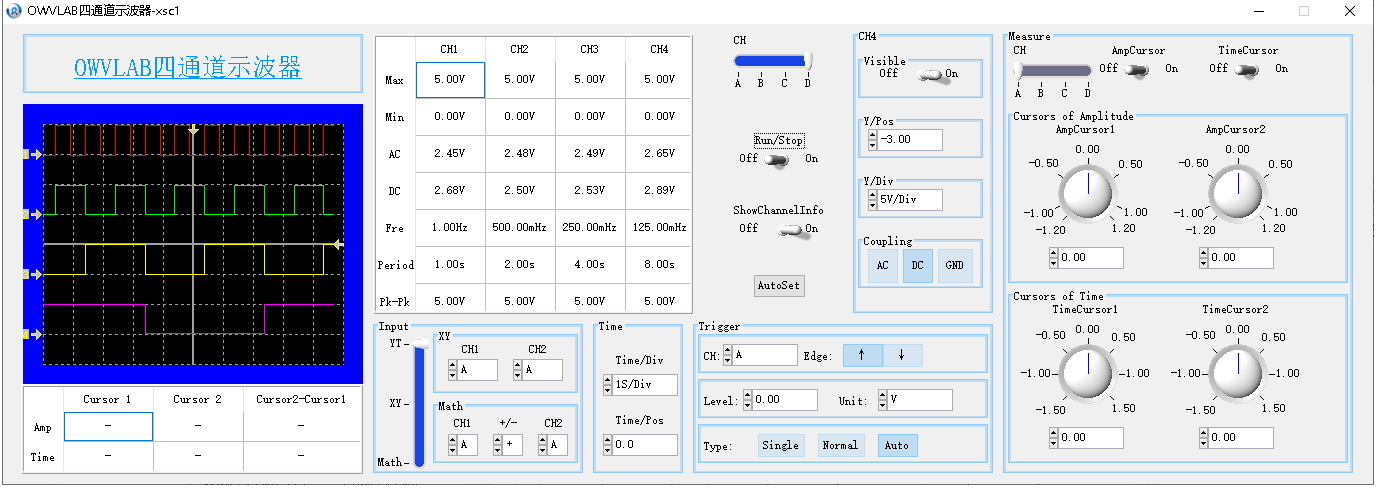

用四通道示波器观察时钟clk及各级触发器输出的Q0、Q1、Q2信号。根据观察,在图2中画出Q0、Q1、Q2的波形(与clk信号的边沿对应好,从Q2Q1Q0=000的状态开始),并观察数码管的显示情况。

二。实验图

三。实验报告内容

由JK触发器构成的二进制计数器有着哪些特点?

计数模值M,触发器级数k:M=2^k

搭建电路完成实验,补充完整图2,说明数码管的显示情况;

数码管从0至7循环显示,仿真后观看数码管即可,点击示波器看到图2波形

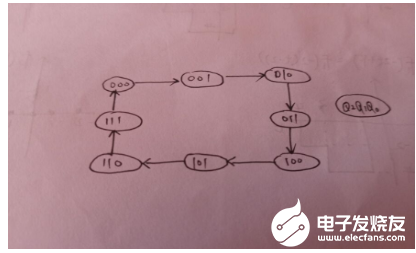

3. 画出图1电路的状态转移图;

4. 如果要构成二进制减法计数器(模8),在图1电路的基础上要做哪些改动?

二进制减法计数器(模8):J1=K1=Q0’,J2=K2=Q0‘Q1’

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

12位二进制计数器2009-09-16 6123

-

TTL二进制同步可逆计数器2009-08-03 621

-

二进制同步计数器74LS161引脚图及功能表(管脚图)2007-11-22 52323

-

电源二进制计数器电路图2009-06-26 1089

-

异步二进制计数器2009-09-30 14014

-

同步二进制计数器2009-09-30 11265

-

什么是二进制计数器,二进制计数器原理是什么?2010-03-08 30400

-

3位二进制计数器2017-11-08 1497

-

二进制加计数器浅析2017-11-24 922

-

二进制与十进制数对照显示实验,十进制,二进制对照2018-09-20 2376

-

数字二进制计数器的设计和实现2022-07-28 1228

-

构建一个4位二进制计数器2022-12-02 3303

-

可预置同步4位二进制计数器;同步复位-74LVC1632023-02-16 294

-

可预置同步4位二进制计数器;同步复位-74HC_HCT163_Q1002023-02-21 202

-

可预置同步4位二进制计数器;同步复位-74HC_HCT1632023-02-21 266

全部0条评论

快来发表一下你的评论吧 !