基于FS2在系统分析仪实现复杂SoPC系统的方案设计

电子说

描述

作者:Judd Heape,Neal Stollon

将可编程逻辑与CPU子系统集成于同一芯片令系统设计者可以在一定范围内决定某些功能的实现方式,AES先进加密标准算法的硬件实现即为这样的特殊应用实例。AES加密是互联网协议安全规范(IPsec) 的基础模块,提供增强无线连接安全性的IEEE802.11i规范也采纳AES为其加密算法,因而传统通讯设备供应商需要增加AES模块以提供更全面的VPN服务。由于AES算法直接面向位操作,所以,它在可编程逻辑上可以得到非常高效的实现。

分析仪及其工作环境

FS2(First Silicon Solutions)公司的在系统分析仪支持基于QuickLogic公司的嵌入式标准产品QuickMIPS的单片系统硬件和软件开发。除了完全支持QuickMIPS片上MIPS处理器的所有调试功能之外,该分析仪还内建可配置逻辑分析监控单元(CLAM),该单元可以从片外追踪并触发QuickMIPS可编程逻辑的1024个指定信号。FS2探测器可通过14针EJTAG调试连接头以及1根10针(或38针)的追踪电缆来连接目标系统。QuickMIPS可编程逻辑中的片上仪器应用模块(OCI)通过FS2追踪电缆与用户指定的内部信号相连,用于追踪和触发。

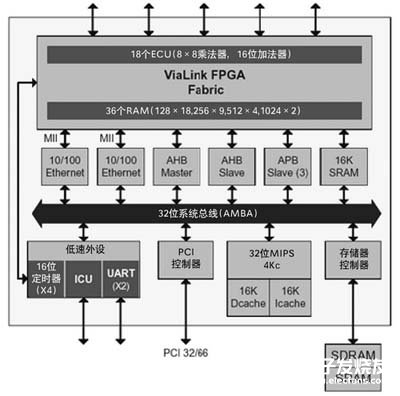

除可编程逻辑之外,QuickMIPS内还集成了32位MIPS 4Kc处理器和一系列片上外设。这些片上外设包括2个以太网接口、2个串口、1个32位66MHz的PCI主从接口、1个SDRAM和SRAM控制器、4个定时器以及1块片上SRAM。所有外设、处理器和可编程逻辑均通过AMBA总线连接(见图1)。AMBA总线为这些连接提供5个片上可用端口,包括先进高性能总线(AHB)主/从接口各1个以及3个先进外围总线(APB)从接口。任何实现于可编程逻辑的电路均可通过上述片上AMBA总线端口实现与处理器以及片上外设的连接,设计者可以根据实际需要使用上述5个端口中的不同组合来连接电路。QuickMIPS的片上MIPS处理器也支持增强JTAG(EJTAG)接口。EJTAG接口除支持处理器实现中止、单步、重启以及软件断点等调试功能之外,还包括指令/数据虚拟地址、硬件断点以及支持外部EJTAG探测仪的TAP端口。

图1 QuickMIPS片上可用资源框图

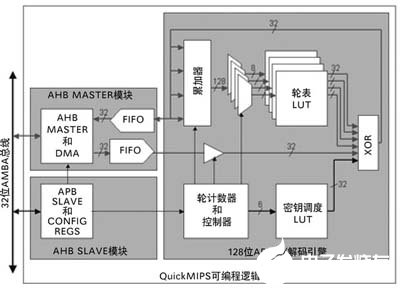

图2 硬/软件交互触发示意图

AES应用实例

软硬件协同AES算法主要由查找表和异或逻辑构成,因此它非常适合用可编程逻辑实现。在本文中,AES的编解码算法由可编程逻辑实现,而密钥调度(key schedule)和轮查找表(round LUT)则由CPU生成。一旦CPU完成了查找表的生成,就可以利用编解码函数将输入的任意大小的明文编码为连续的密文流输出。

基于连续报文流的数据吞吐需要,在可编程逻辑中还建立了一个DMA引擎,用于从/向AES核下载/上传报文,并直接处理与系统存储器之间的通讯。该DMA引擎能够操作连接在QuickMIPS器件上的任何存储器,包括片上SRAM和片外SRAM/SDRAM。使用DMA引擎可以避免无用的等待周期,从而高效运用AES核进行连续的编解码操作。

该DMA引擎使用1个AMBA总线的AHB主控制器,用于连接简单的AES核数据输入/输出接口和相对复杂的AHB主接口。它还包含2个用于AMBA总线与AES模块之间异步数据缓冲的128×32位的FIFO,以保证在AMBA总线受制于CPU的工作频率时,AES仍可独立工作于最佳频率。

存储源地址、目标地址、DMA传输块大小、DMA传输使能和AES编解码模式转换等控制信息的寄存器也可用可编程逻辑实现,CPU可以用它们来设置DMA引擎和配置AES核。这些控制寄存器通过APB从接口连接在AMBA总线上。

除连接DMA和AES的控制寄存器之外,APB接口还可用于在AES核内加载存储了不同查找表数据的RAM模块。这些查找表中的静态模式(static pattera)和密钥调度用于AES算法中不同的轮,它们系统调试

由于硬件和软件的调试方法往往格格不入,如时间难于同步、调试方式迥异,及调试阶段难于交互通讯等,因此,调试由硬/软件模块交互构成的系统非常困难。基于QuickMIPS的FS2硬/软件协同调试方案可以有效解除上述困扰(见图2)。

EJTAG探测仪通常用于监控CPU的执行进程,然而一旦整合系统被分拆为交互操作的硬/软件模块,那么,在缺乏有效硬件监控手段的情况下,硬/软件模块间交换数据进程的调试工作的复杂程度就显著提高了。

在硬/软件协同的AES解决方案中,EJTAG探测仪可用来监控CPU生成密钥调度和复制可编程逻辑中的RAM模块数据的进程,此外,EJTAG还可以监控CPU设置DMA引擎的过程。EJTAG探测仪的强大功能保证了用户对源地址、目标地址和CPU读写可编程逻辑时的数据传输的监控。一旦AES系统的硬件部分实现了,CLAM即可监控CPU通过AMBA总线对可编程逻辑进行的操作。这里,CLAM将监控包括AHB主接口和APB从接口的所有相关AMBA总线信号。被监控的总线调用事件包括:通过APB从接口加载RAM模块中的密钥调度和轮表,并设置DMA地址和控制寄存器;通过AHB主接口以DMA方式将明文从远程AMBA从设备传送到AES核,并将密文从AES核传送到远程AMBA从设备。

一旦可编程逻辑中实现了OCI模块,通过监控AMBA总线信号,任何AMBA总线上的事件均可被CLAM准确甄别、触发和捕获。能够准确捕获AMBA总线信号状态的触发器可以被定义为AMBA总线信号的任意组合。例如将向特定的AMBA地址进行的写操作设为触发事件,就可以捕获加载RAM模块状态;而将触发点置于APB对寄存器空间的选择信号上,则可以捕获DMA地址和控制寄存器的设置状态;最后,对内部AMBA仲裁单元给出的AHB主接口设定触发,就可以捕获DMA传输事件。用户可以根据这些捕获结果来判断AMBA总线的操作是否符合要求。

AES应用模块的调试需要监控以下信号:输入AES核的明文,轮表RAM模块的索引(地址)输入和数据输出,计数器输出的当前轮数和每一轮中的数据状态,密钥调度RAM模块中的数据输出,及128位累加器输出。

通过OCI锁定监控上述信号可以详尽地观察到AES核的操作。由于可以同时对数百个信号以不同追踪深度进行监控,用户可以毫无困难地捕获和观察AES编/解码的所有44个周期。例如,如果大多数AES转换都正确执行,但是在某一个输入报文模式下发现了意外的结果,在这种情况下,CLAM能够配置特定报文进入AES引擎时的触发。虽然在触发产生前后会出现数百个AES转换,但是CLAM可以实时地从中选出所需的那个事件,就无需为此去专门向系统提供一份输入数据了。

交互触发

交互触发是EJTAG调试器与CLAM协同调试解决方案中最重要的特点。交互触发分为2种方式,CLAM的触发事件能够使CPU在执行代码的相应行中断,同时CPU执行中的断点也能够触发CLAM事件。

上述第1种交互触发事件可以应用在软硬件协同AES系统的调试过程中,例如寻找被写入密钥调度RAM的异常数据时。如果已知异常数据正在向RAM中写入,且此数据可以被观测到,并可被CLAM触发,则可以通过触发导致CPU在数据写入的时候暂停执行。由于密钥调度的生成和加载入RAM的过程都由CPU控制,因此可以在代码中找到异常数据进入AES核硬件部分的那个时刻。这样使得用户可以查询到那个时刻的存储器和寄存器中的数据,在调试软件算法的同时观测到硬件上出现的结果。

第2种情况适用于用户打算观测指定软件断点处的可编程逻辑中正在传输的数据时。例如当CPU正在处理要写入RAM的数据表时,用户可能需要在数据传送到硬件之前进行一些字节交换(byte swap)的操作。在调试时,用户可以在源代码中的字节交换部分,或是在结果输出至AMBA总线时设置断点。当字节交换的结果写入硬件部分时,这些数据就可以通过AMBA从接口进行观察。虽然没有设置硬件触发,但是软件中的断点可以使当时的硬件状态被捕捉到。

结语

嵌入式标准产品平台的高速发展需要与之相应的精确周密的调试工具也随之发展。对CPU与可编程逻辑共存的SoPC而言,用于调试CPU时的传统的JTAG方法和FPGA的逻辑分析同样需要,更重要的是有交互触发的硬/软件环境,以便快速地隔离、甄别并调试复杂问题。理想的SoPC系统分析工具应该能够处理上述问题,并且提供监控系统内部总线事件的能力。

为了避免调试工具扰乱系统的正常操作,对系统内部总线事件和FPGA内部信号的监控、追踪和触发绝不能暂停和干预CPU的工作。因此,可以独立或者协同调试CPU与FPGA的工具是目前最有效的SoPC系统分析方法。

在本文中,FS2公司的在系统分析仪和QuickLogic公司的QuickMIPS器件的配合使用,以及软硬件系统AES引擎的实例提供了精彩的案例平台,充分体现了上述这些先进的调试技术对复杂SoPC系统设计分析的重要性。

责任编辑:gt

-

基于MATLAB的系统分析与设计——时频分析2012-02-28 0

-

手机硬件系统分析2013-05-03 0

-

[电路与系统分析:使用MATLAB]2013-06-03 0

-

系统分析方法.ppt2017-10-03 0

-

系统分析方法.zip2017-10-04 0

-

【下载】《电路与系统分析(使用MATLAB)》2018-01-23 0

-

微波系统分析仪测量卫星的端到端群时延测量技术简单设计2019-06-03 0

-

信号与系统分析及MATLAB实现 梁虹编着2020-05-22 0

-

指令系统分析2006-03-21 1035

-

系统分析ppt2008-11-07 693

-

什么是系统分析?2008-11-07 2538

-

基于MATLAB的系统分析与设计时频分析2016-01-15 514

-

基于MATLAB的系统分析与设计信号处理2016-01-15 608

-

系统分析方法2017-12-06 672

-

摩托罗拉R-2600系列通信系统分析仪操作手册2021-04-19 840

全部0条评论

快来发表一下你的评论吧 !