基于32位浮点DSP芯片TMS320C6713实现语音编解码系统的设计

处理器/DSP

描述

作者:齐岽清,赵加祥,袁鑫

本系统使用TI公司浮点型DSP TMS320C6713实现G.723.1等语音编解码,为G.723.1、G.729等常用的低码率语音压缩标准提供运行及测试硬件平台。有别于大多数编解码系统,本设计采用了性能更好的浮点型处理器和20位以上的数模模数转换器,总线带宽提高为16位,并采用主控性更强的HPI 接口。系统设计具有以下优势:(1)数据的传输通过USB口完成,完全支持速度在5.3 Kb/s或6.3 Kb/s的多路编码输出,方便用户使用,并可使用USB独立供电。(2)利用USB控制芯片的GPIF模式与DSP连接,程序简单、修改灵活。采用主频300 MHz、处理速度2 400 MIPS/1 800 MFLOPS的TMS320C6713,可以使每帧数据的处理时间小于37 ms的帧延迟,满足系统运行的实时性。(4)数据的传送工作交由USB控制芯片68013完成,可使DSP从繁琐的数据搬运及USB协议处理工作中独立出来,使更多的资源用于数据处理。(5)采用由主机加载固件的方法,节省数据处理端的硬件与软件资源,而且便于固件的更新升级。(6)采用DSP中的外设接口HPI与主机相连,由主机掌握主控权,既能够使数据访问得到简化还可以通过HPI实现DSP自举。

1 基本概念介绍

1.1 CY7C68013性能特点

CY7C68013(EZ-USB FX2)是Cypress半导体公司的新一代高速USB系列,可以用USB2.0最大数据传输率传输数据。该芯片基于EZ-USB FX芯片开发,集成有发送器、SIE、8051微控制器、存储器和可编程IO接口,是一种完全集成的USB2.0方案。

1.2 G.723.1简介

G.723.1是一种低码率语音压缩标准,是H.324标准系列的一部分,也是VoIP的常用解决方案之一,可在低比特率通信终端(PSTN和无线网络)上进行多媒体通信。使用G.723.1标准能够将8 kHz采样l6 bit的线性PCM语音信号压缩成6.3 Kb/s或5.3 Kb/s的比特流,其压缩比例较高,占用带宽较低,而且具有很好的音质。

2 硬件设计

2.1 TMS320C6713外设接口HPI

TMS320C6713是一款高性能的32位浮点DSP,适用于专业音频信号处理。HPI即主机接口,是TMS320C6713片上集成的外设接口之一。通过HPI 可以方便地实现多处理器系统,外部处理器作为主处理器,DSP作为从处理器。通过HPI 接口,外部主机可以访问DSP除L2控制寄存器、中断选择寄存器、仿真逻辑之外的全部存储器映射空间。

2.2 读写时序

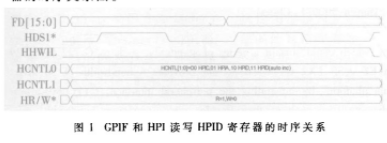

本实验采用CY7C68013和TMS320C6713芯片。在GPIF接口部分,IFCLK设置为48 MHz内部时钟,使用16位宽的数据总线(设置WORDWIDE=1),分配CTL[2:0]控制HPI的时序。使用GPIF Tool生成波形描述符,分别用于HPIC/HPIA/HPID的读写控制。值得注意的是:由于HDS1*/HDS2*/HCS*相关,可以使HCS*有效,HDS2*置“1”,并通过HDS1*控制选通;HHWIL控制传输的是第一半字还是第二半字;HCNTL[1:0]决定哪个寄存器正被访问。由于采用DIN连接器,其传输速率最高可达几十兆赫兹,这也是其传输瓶颈。如果采用手工单独装配的SMA硬件连接器,其硬件连接的速度完全可以满足GPIF和HPI的要求。当然,前者每个引脚的成本不到后者的百分之一。图1为GPIF和HPI读写HPID寄存器的时序关系图。

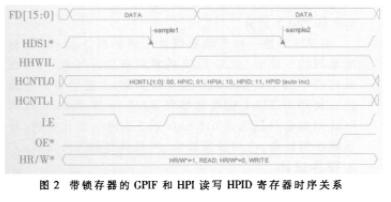

通过FX2固件、利用非GPIF I/O信号引脚可实现更多的信号输出。使用DM74LS573N锁存器,采用数据锁存的办法可以减小由布局布线等原因带来的互感、串联电感、寄生电容等减缓信号传播的影响,在硬件测试阶段能够有效解决传输误码的问题。由于74LS573的传输延迟,系统的可靠性建立在牺牲系统带宽的基础上。改用74LVC16245双向缓冲器,可以实现GPIF主控的数据读、写功能。图2为带锁存器的GPIF和HPI读写HPID寄存器的时序关系图。

2.3 硬件连线

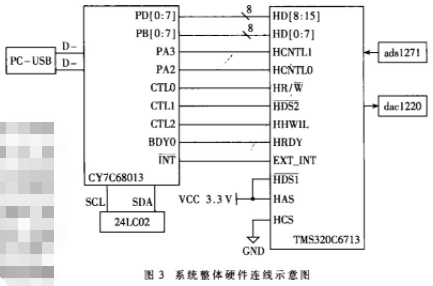

系统整体硬件连线示意图如图3。

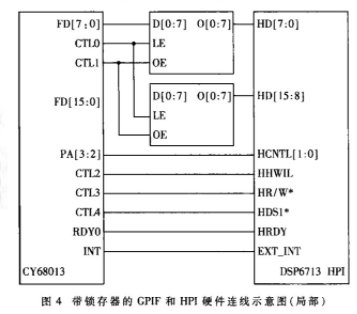

图4为带锁存器的GPIF和HPI硬件连线示意图。

3 软件设计

此方案包括4个方面的程序设计:固件程序、驱动程序、主机应用程序和DSP数据处理程序。

3.1 固件程序

固件程序是指运行在CY7C68013 51内核中的程序,主要包括设备描述符信息、设备功能代码和USB同DSP处理器间的通信控制功能代码。对于使用GPIF的FX2系统,固件还应能够分配FIFO读和写波形到4个FIFO中的任何一个。

3.1.1 固件程序设计

固件程序开发基于KEIL C51,使用Cypress公司提供的固件函数库Ezusb.lib和固件框架以提高开发效率。固件函数库提供了一系列与USB协议有关的函数,固件框架已经实现了初始化、重枚举、电源管理等功能。

固件程序由以下文件组成:

FX2.h 共同的FX2常数、宏、数据类型以及函 数库内库函数的原型框架。

FX2regs.h FX2寄存器的声明及位屏蔽常数

Fw.c 框架源代码

Ti6713HPI2cy13.c 用户函数挂钩的相关定义

Gpif.c 由GPIF_Designer生成,用以匹配HPIC、HPIA、HPID时序

Dscr.a51 USB 描述符表的范例

Ezusb.lib EZ-USB 函数库目标代码

USBJmpTb.OBJ USB中断向量表和GPIF中断源

其中Fw.c、Ti6713HPI2cy13.c和Gpif.c是固件程序的核心内容。

在Fw.c中主要包括任务分配器(TD)函数和设备请求(DR)函数。Ti6713HPI2cy13.c中定义这些关键函数。Gpif.c由GPIF_Designer生成,本设计将GPIF_Designer的4组波形分别定义为:第一半字写、第二半字写、FIFO写和FIFO读。其中前两组波形配合任务分配器函数TD_Poll()完成DSP中寄存器HPIC和HPIA的写,后两组波形配合TD_Poll()完成自增模式下HPID的读写。波形的设计要严格遵守HPI总线访问时序。

在TD_Init()中设置整体状态变量的初始值并规定各种端点资源的使用(包含中断)以及配置外围接口的输入输出。为匹配HPI通信所需数据总线宽度,寄存器EPxFIFOCFG中 WORDWIDE位置1。PORTB配置为FD[7:0],PORTD配置为FD[15:8]。为了达到最大的USB2.0带宽,设计中将AUTOOUT/AUTOIN位置1。主机与主控制器被直接连接,CPU被旁路,OUT FIFO自动从主机提交到FIFO。

TD_Init()定义中的程序片段:

……

EP2CFG=0xA0; //端点2可用、输出、数据流、512 B、

//4倍缓冲模式

SYNCDELAY;

EP4CFG=0x00; //端点4不可用

SYNCDELAY;

EP6CFG=0xE0; //端点2可用、输入、数据流、512 B、4倍缓冲模式

SYNCDELAY;

EP8CFG=0x00; //端点8不可用

SYNCDELAY;

FIFORESET=0x80; //暂不接受主机请求

SYNCDELAY;

FIFORESET=0x02; //将EP2 FIFO恢复为缺省状态

SYNCDELAY;

FIFORESET=0x06; //将EP6 FIFO恢复为缺省状态

SYNCDELAY;

FIFORESET=0x00; //重新开放主机请求

SYNCDELAY;

EP2FIFOCFG=0x01; //

SYNCDELAY;

EP2FIFOCFG=0x11; //数据宽度16 bit、AUTOOUT模式

SYNCDELAY;

EP6FIFOCFG=0x09; //数据宽度16 bit、AUTOIN模式

SYNCDELAY;

……

TD_Poll()中最核心部分在于完成写HPIC寄存器、写HPIA寄存器、以自增模式读写HPID。

(1)写HPIC寄存器。

EP0BCL=0; //激活EP0缓冲器以接收主机的下一个请求

while(EP01STAT & bmEP0BSY);//等待EP0空闲可用

while(!HPI_RDY); //等待HPI准备好接收数据

IOA=bmHPIC; //PA2、PA3选通HPIC

GPIFWFSELECT=0xB9; //选择写入第一个半字的GPIF波形

GPIF_SingleByteWrite(EP0BUF[0],EP0BUF[1]);

//写入一个16 bit半字

其中GPIF_SingleByteWrite()定义为:

void GPIF_SingleByteWrite(BYTE gdatah,BYTE gdatal)

{

while( !(GPIFTRIG & 0x80) ) {;} //轮询GPIFTRIG.7

//Done位查看上一次事务是否完成

XGPIFSGLDATLX=gdatal; //高8位写入XGPIFSGLDATLX

XGPIFSGLDATH=gdatah; //低8位写入XGPIFSGLDATH

}

对于16位模式,把高8位写入XGPIFSGLDATLX,低8位写入XGPIFSGLDATH就可以自动启动一个单向写事务。当这个事务完成时,GPIFTRIG.7 Done置1,触发GPIFdone中断,68013使XGPIFSGLDATLX和XGPIFSGLDATH中的数据出现在16位数据总线FD[15:0]上。

(2)写HPIA寄存器。

与写HPIC基本相同,只是将IOA=bmHPIA,使PA2、PA3选通HPIA。

(3)自增模式下写HPID。

if(GPIFTRIG & 0x80) //检查当前GIPF是否空闲

{

if (!(EP24FIFOFLGS & 0x02 ) ) //检查外围是否有

//数据等待传入EP2,EP2非空

{

IOA=bmHPID_AUTO; //PA2、PA3选通自增模式HPID

while(!HPI_RDY); //等待HPI准备好传输数据

SYNCDELAY;

GPIFTCB1=EP2FIFOBCH;

SYNCDELAY;

GPIFTCB0=EP2FIFOBCL; //将EP2FIFO中字节数设置为TC的值

SYNCDELAY;

GPIFTRIG=GPIF_EP2; //写寄存器GPIFTRIG触发 EP2 OUT事务

SYNCDELAY;

while( !( GPIFTRIG & 0x80 ) ); //等待本次事务处理完毕

SYNCDELAY;

}

}

(4)自增模式下读HPID。

与自增模式下写HPID写过程基本相同。不同点在于:事务计数器的值不是端点6中字节的个数,而是应当由主机方通过控制端点EP0告知FX2;读EP6前要检查EP6 FIFO非满,触发时将GPIFTRIG设置成EP6IN。

3.1.2 固件代码的存储位置

本设计将固件代码存在主机中,设备上电以后由下面要介绍的驱动程序将固件下载到FX2片内RAM后执行,这一过程也就是重枚举。这种方法便于系统的调试和升级,用户可以根据自己的需要将相应驱动下载到PC上,从而使设备呈现出不同的属性功能,并可以进行适当的软升级。这种方法对片外EEPROM或ROM的存储空间要求很低,便于实现,使用灵活。

另外还可以把固件代码固化到一片EEPROM中,上电后FX2通过I2C总线下载到片内RAM后执行;或者把程序固化到一片ROM中充当外部程序存储器,连接到FX2总线上。

3.2 设备驱动程序

设备驱动程序提供用户访问设备的接口。EZ-USB系列芯片都具有通过下载固件和重枚举的方式来动态改变设备特性的能力,这就需要一个特殊的具有下载固件并完成设备重枚举功能的设备驱动程序,也可以叫做固件下载驱动程序。Cypress公司发布的EZ-USB软件开发包中提供了一个固件下载驱动程序的模版,即EZ-LoaderDriver。通过它可以方便地将自己的固件程序嵌入固件下载驱动程序。主要步骤包括:(1)设定固件下载前后两次枚举的不同VID和PID;(2)修改ezloader中source文件的目标名称;(3)修改Dscr.a51中的VID、PID;(4)利用ezloader提供的工具将用Keil编写固件所生成的.hex文件转换成.sys文件;(5)编写与.sys文件相对应的安装信息文件(.inf);(6)修改EEPROM,将VID、PID写入,并设置成C0引导加载模式。

3.3 主机应用程序

为提高开发速度,本设计的主机应用程序在Cypress公司提供的USB Control Pane的基础上加以修改,增添了读取存储和分析音频文件(主要是.wav文件)的功能。

3.4 DSP数据处理程序

将G.723.1公布的低码率语音压缩算法以C与汇编混合编程的方法移植到TMS320C6713,并加以调整优化。

本系统开发旨在为G.723.1以及G.729等常用的低码率语音压缩标准提供运行及测试的硬件平台。DSP系统中的程序采用C与汇编混合编程的方法。实验表明,USB的数据带宽完全可以满足多路音频数据实时处理的要求,并具有良好的稳定性和适应性,能够达到所要求的通信质量,实现较为完善的语音编解码系统。

责任编辑:gt

-

[共享] 卡尔曼滤波算法在TI TMS320C6713 DSP上的实现2011-08-20 0

-

TMS320C6713 AD DA转换2014-06-02 0

-

TMS320C6713程序怎么烧进Flash里面2015-03-16 0

-

跪求TMS320C6713的资料2016-12-08 0

-

TI TMS320c6713浮点处理器与Spartan3an相比用于高速浮点DSP?2019-05-31 0

-

TMS320C6713 DSP芯片与pc机间的数据传输2019-06-05 0

-

如何使用一个TMS320C6713的EMIF口是否可以和多个tms320c6416的HPI口通信?2020-05-27 0

-

如何采用TMS320C6713 DSP芯片设计嵌入式说话人身份识别系统?2021-04-09 0

-

基于TMS320C6713的G.723.1语音编解码的实时实2009-11-27 615

-

基于TMS320C6713及AM29LV800B的上电自举设2010-12-23 622

-

基于TMS320C6713的多路CVSD语音编解码2009-11-16 1825

-

卡尔曼滤波算法在TI TMS320C6713 DSP上的实现2016-06-03 1007

-

TMS320C6713 DSK原理图2016-08-05 998

-

TMS320C6713管脚分类2023-11-16 171

-

通过采用PCI9052接口实现TMS320C6713芯片与PC机间的高速数据传输2020-01-16 2836

全部0条评论

快来发表一下你的评论吧 !