FPGA设计之共阳极的数码管的电路图

电子说

描述

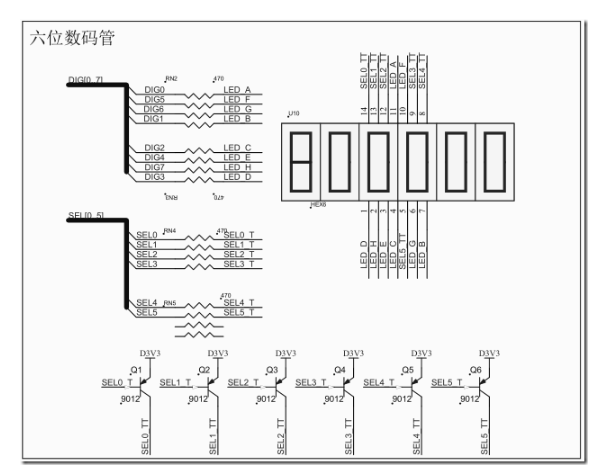

数码管是一种常见的用于显示的电子器件,根据数码管大致可以分为共阴极和共阳极两种,下图所示的是一个共阳极的数码管的电路图(摘自金沙滩工作室的 51 开发板电路图),我的 AX301 开发板与这张图的情况类似,几乎所有的教科书上都会讲到数码管的原理,这里我就不再详述了。

由于多个数码管的段选信号(下图中的 DB0~DB7)是共用的,想要显示多个数字需要用到动态扫描,动态扫描电路需要使用时钟。冒然的使用时钟会使得初学者不知所措,所以在这篇基础的组合逻辑电路中只点亮单个数码管,这样就不必涉及到时钟了。时钟、时序逻辑这些概念则会留到后面的章节中介绍。

由上图可知,所有的引脚都是低电平有效的,如果想要在上图中的 DS6 上显示 8,需要把 LEDS5、DB7 ~ DB10 都置为低电平。

这次我们的实验目的是在数码管上显示一个 8,在查看自己开发板的电路图后得知,需要将 FPGA 的输出管脚 SEL0、DIG0~DIG6 设为低电平(DIG7 为小数点 DP),需要注意的是 SEL0 控制的是最右边的数码管。

我的开发板电路图(摘自 黑金AX301 提供的 PDF 文件):

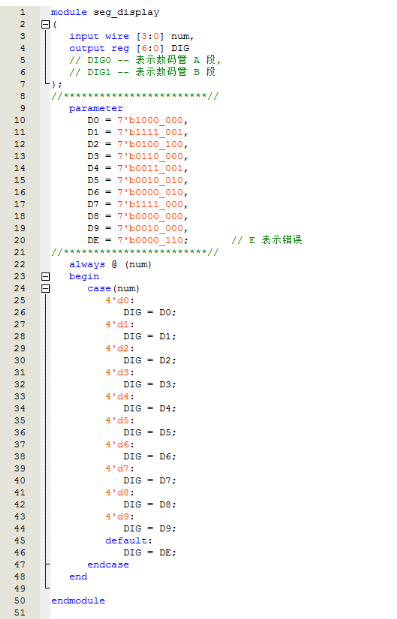

根据上面的总结,新建名为 seg 的工程,为了使我们的代码有一定的通用性,这里用到了参数声明。

数码管显示模块 seg_display 接受输入信号 num 的值,并转化编码用于显示。

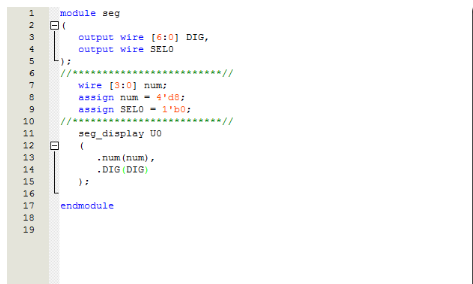

顶层模块 seg(必须和工程同名),在顶层模块中调用了 seg_display 显示模块,并且告诉 seg_display 模块需要在 SEL0 上显示 8,这段代码如下:

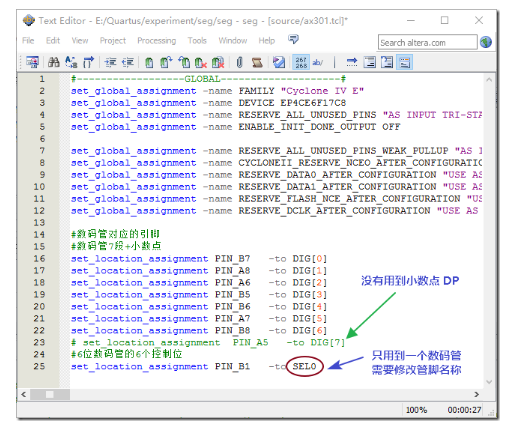

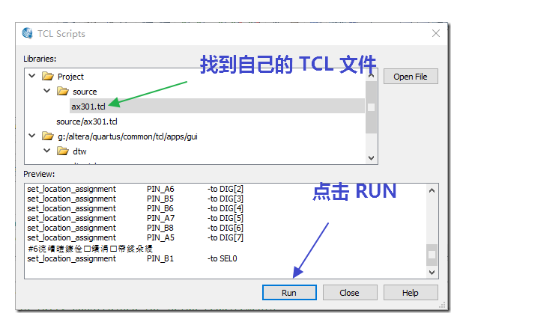

由于工程需要用到的管脚较多,如果手动分配可能会出现错误,这里介绍使用 tcl 脚本来分配管脚的方法。

如图新建一个 TCL 文件:

板子附带的资料有一个厂家写好名为 ax301.tcl 的管脚分配文件,粘贴以下内容并保存为 ax301.tcl。

可以看到,tcl 文件在第 2 行定义了芯片家族,第 3 行定义芯片型号,第 4 行设置不用的管脚为三态……

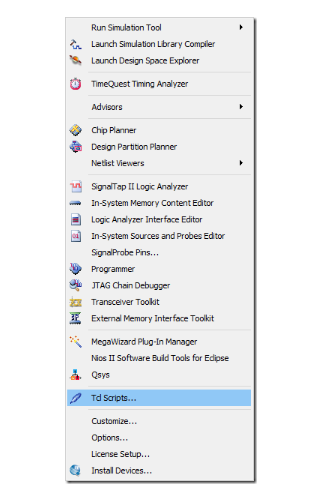

在 Quartus 主窗口下点击 Tools,找到以下选项:

运行 tcl 文件。

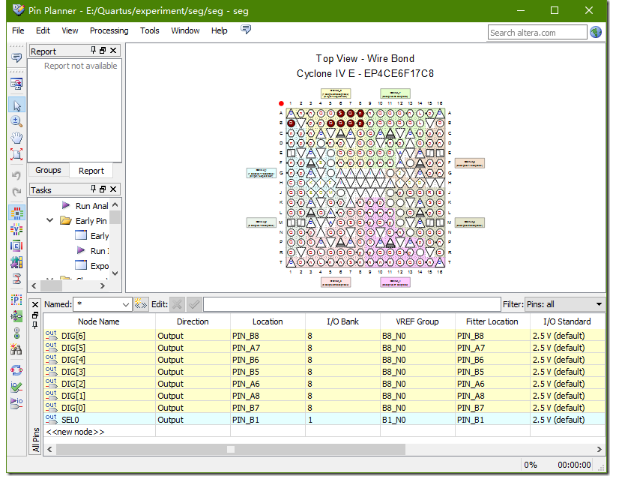

最后编译整个工程,编译结束后查看管脚分配窗口,可以看到所有的管脚都自动分配成功了。

最后下载 sof 文件到您的板子上,看到您期待的数字了吗?(*^__^*) ,此外如需显示其他的数字,只需要修改 seg.v 中 num 的值即可。

-

分辨数码管引脚共阴和共阳极2012-08-20 0

-

共阳极数码管动态显示程序显示问题2015-07-18 0

-

新人求助,仿真数码管如何将共阴极改成共阳极2015-12-04 0

-

转:FPGA学习之六位数码管驱动2017-05-22 0

-

DIY:LED数码管时钟电路设计(原理图+程序)2018-11-20 0

-

led数码管控制灯灭设计实验--FPGA学习2020-10-23 0

-

如何实现单片机P0端口驱动共阳极数码管0-9循环显示2021-07-14 0

-

单片机共阴极数码管编程2021-07-22 0

-

数码管动态显示四位共阳极数码管2021-08-04 0

-

如何用一个共阳极数码管循环显示数值“0~F”?2021-11-10 0

-

数码管循环显示单个数字相关资料下载2021-12-02 0

-

PNP型三极管s9012驱动共阳极数码管的方法2022-01-05 0

-

数码管的结构和功能,如何使用数码管2022-01-10 0

-

为什么一般共阳极数码管更为常用呢2022-01-21 0

-

简单共阳极数码管电路图大全(五款led数码管电路图详解)2018-03-29 142407

全部0条评论

快来发表一下你的评论吧 !