并行I/O口扩展的2种方式实例介绍

电子说

描述

I/O口不能完全用于输入/输出操作,当需要扩展外部存储器时,P0、P2口用作地址总线和数据总线,此时能用的I/O口就只有P1和P3口,如果再使用串行通信,I/O口就不够使用了,需要扩展I/O口

两种方式:

① 采用普通锁存器、三态门等芯片来进行简单的扩展(如74LS373或74LS244等)

② 采用可编程的I/O芯片来扩展(如8255或8155等)

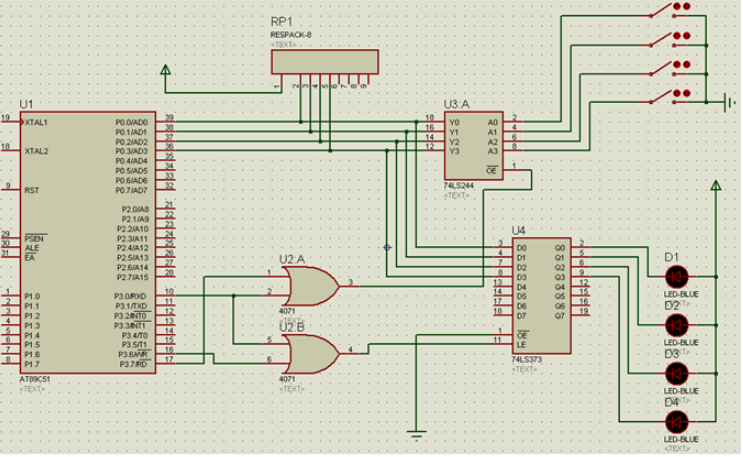

要求:用4个开关控制4个LED的亮灭状态,其中采用74LS244控制开关的输入,采用74LS373控制LED输出

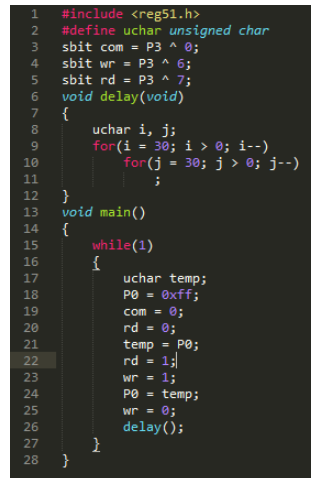

代码:

电路图:

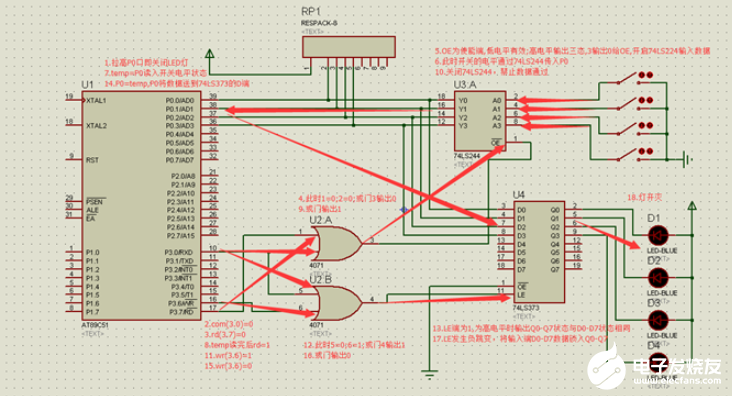

过程分析:

#18 P0=0xff; 通过拉高P0口置为1111 1111,即关闭LED灯;

#19 com=0; 对CD4071 U2.A的1和CD4071 U2.B的5输入一个0;

#20 rd = 0; 对CD4071 U2.A的2输入一个0;

由于CD4071的功能是执行逻辑或运算,1和2分别输入0,则3输出0给74LS244的OE口;

74LS244缓冲驱动器的OE为使能端,低电平是有效的,高电平时输出为三态,此时通过CD4071传给OE低电平,使开关的电平可以通过74LS244传入P0;

开关状态传入P0;

#21 temp = P0; 通过定义的unsigned char temp来存放P0的状态

#22 rd = 1; 对CD4071 U2.A的2输入一个1;

1=0;2=1;此时或门输出为1;

74LS244的OE端高电平时输出为三态,关闭74LS244

#23 wr = 1;对CD4071 U2.B的6输入一个1;

此时5=0;6=1;CD4071 U2.B的7输出一个1;

74LS343的OE为低电平时,用作地址锁存器;LE为高电平时,输出Q0-Q7状态与D0-D7状态相同;当LE发生负跳变(1->0)时,输入端的D0-D7锁入Q0-Q7

#24 P0 = temp; temp中的数据存入P0,传送到74LS343的D端;

#25 wr = 0; 对CD4071 U2.B的6输入一个0;

此时5=0;6=0;CD4071 U2.B的7输出一个0;

LE的状态从1->0,发生负跳变,输出Q0-Q7

LED等接受到开关的情况,发生亮灭。

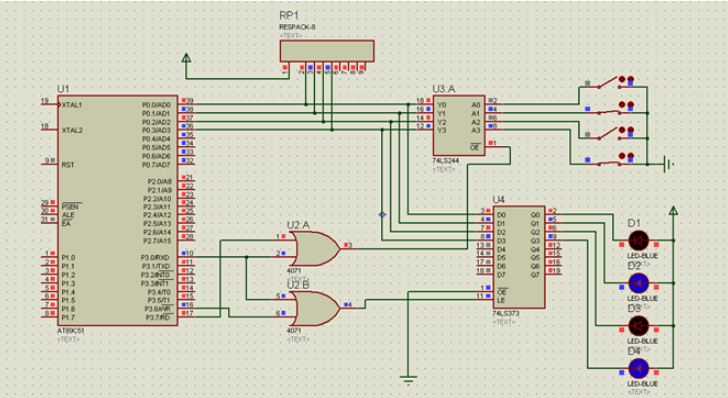

实验结果

-

应用方案:MCU通用I/O引脚扩展2024-01-08 0

-

8255 I/O扩展2013-03-12 0

-

2I/O 口 I2C 通信 4I/O口 SPI2013-11-04 0

-

怎么用8255扩展I/0口?2014-04-03 0

-

I2C总线扩展I/O口通用器件 AT8574兼容PCF8574!2014-05-12 0

-

TMS320VC5410A I/O口的多种扩展与I2C接口模拟2018-12-04 0

-

扩展MCU控制I/O口的方法分享2020-12-25 0

-

一.(四). 直接单片机I/O口驱动:多个I/O口并行工作驱动喇叭:2021-04-28 0

-

51单片机并行I/O口的工作原理是什么2021-11-18 0

-

8051单片机并行I/O口结构2022-01-05 0

-

并行I/O口的相关资料推荐2022-02-08 0

-

串行口的工作方式0介绍2022-02-17 0

-

单片机的并行I/O口与工作模式介绍2022-02-18 0

-

介绍MM编程与I/O编程这两种方式2022-02-24 0

全部0条评论

快来发表一下你的评论吧 !