AXI4读写操作时序及AXI4猝发地址及选择

描述

AXI4读操作

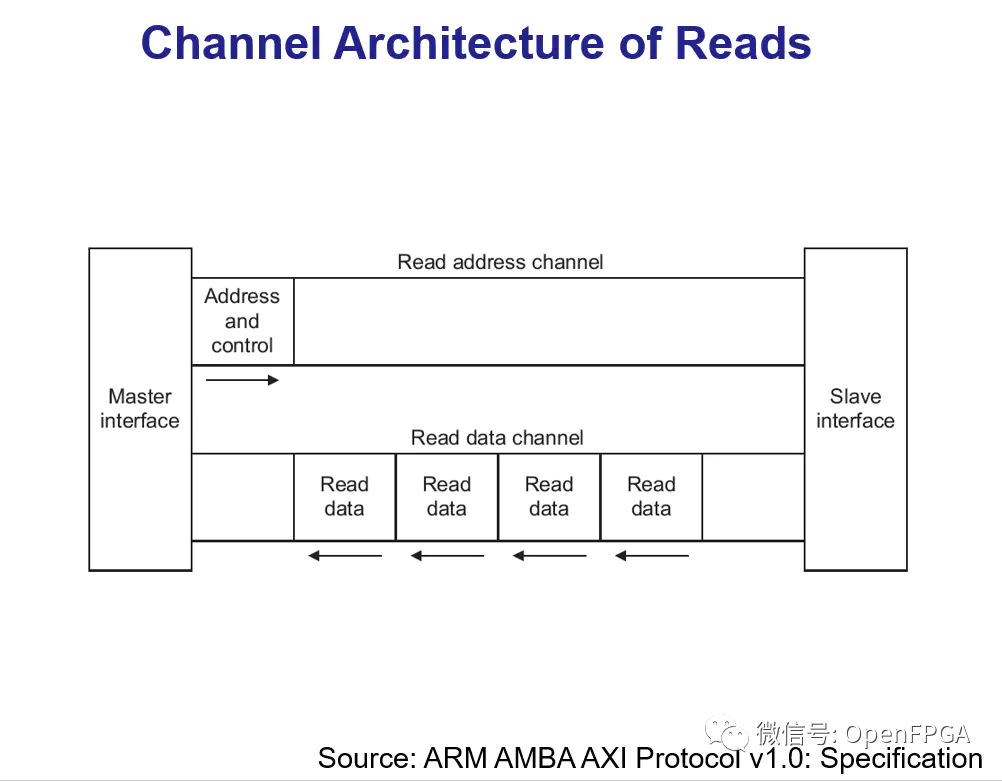

图 4‑15 读通道架构

如上图所示,主设备向从设备通过读地址通道指定读数据地址及控制信号,从设备通过读数据通道将指定地址上的数据传输给主设备。

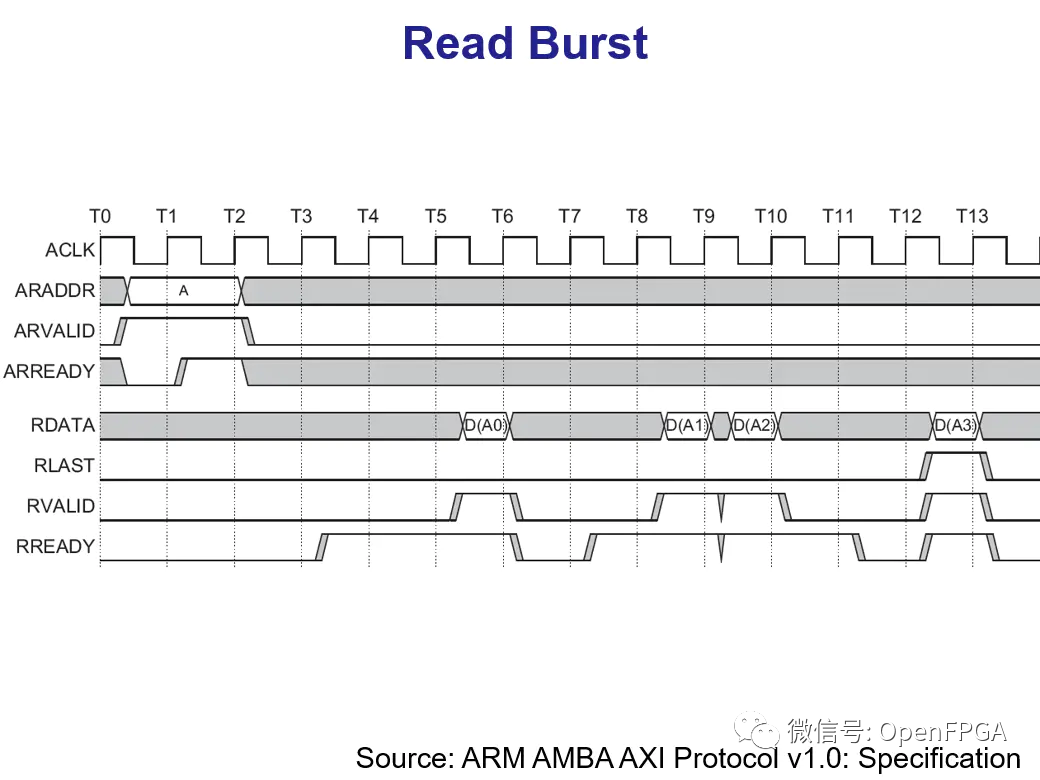

图4‑16 Read Burst 流程

1、当状态机的当前状态为WAIT_START时,master将ARVALID拉高。

2、slave收到ARVALID信号后,将ARREADY拉高,持续到一次burst_len传完为止。master收到ARREADY拉高的信号后,将ARVALID拉低。

3、ARADDR在ARVALID为高时给定对应地址。

4、RREADY信号在收到RVALID信号为高时拉高,保持一个周期,读取出数据。

5、RVALID信号由slave控制,具体控制模式参考slave模块的设计。

6、当一次读取的最后一个数据包读取时将RLAST拉高,表示一次Burst读取完毕。

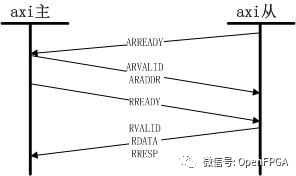

图4‑17 读操作信号依赖

如图可知,读操作的两个channel之间存在如下的依赖关系:必须等到ARVALID和ARREADY同时为High后,RVALID才能拉高。

AXI4写操作:

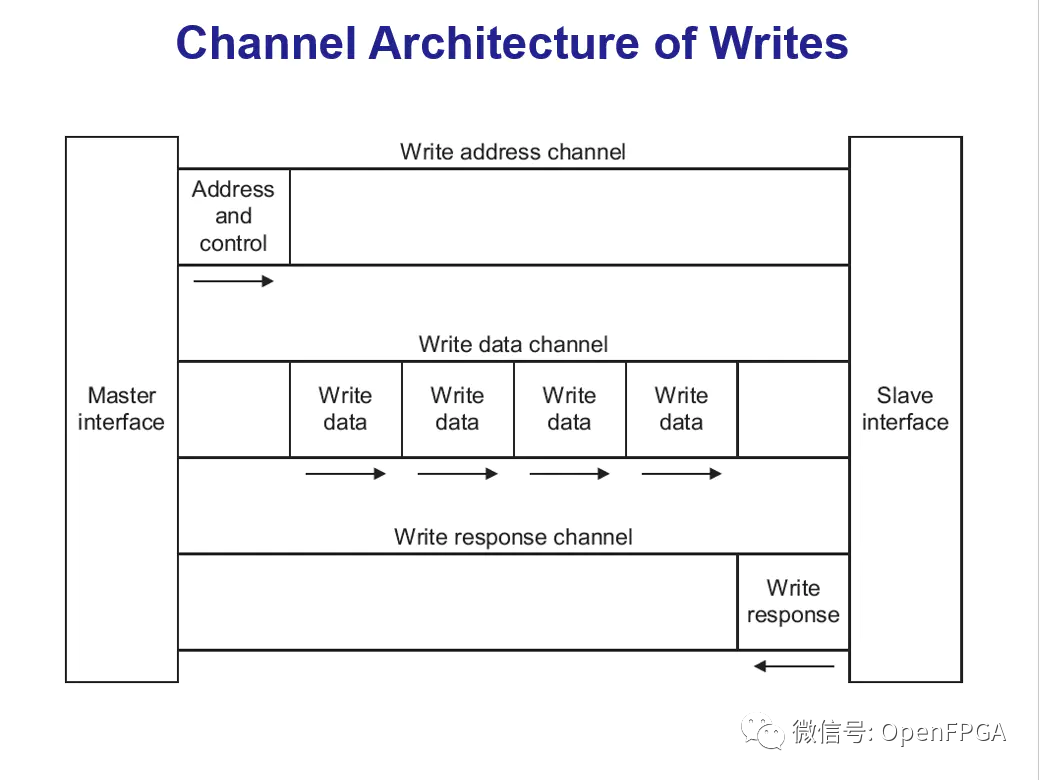

图4‑18 写通道架构

如上图所示,主设备向从设备通过写地址通道指定写数据地址及控制信号,从设备通过写数据通道将指定数据写到从设备的指定地址上。待数据写入完成后,从设备通过写响应通道向主设备传递写响应信号,表明写入完成。

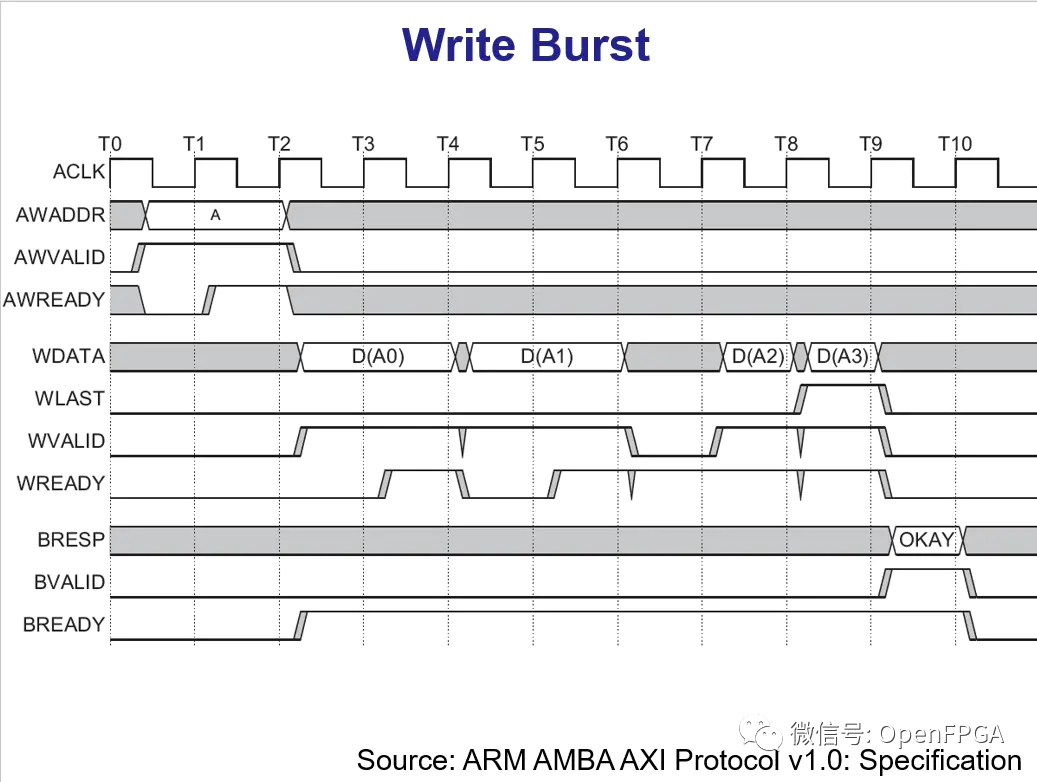

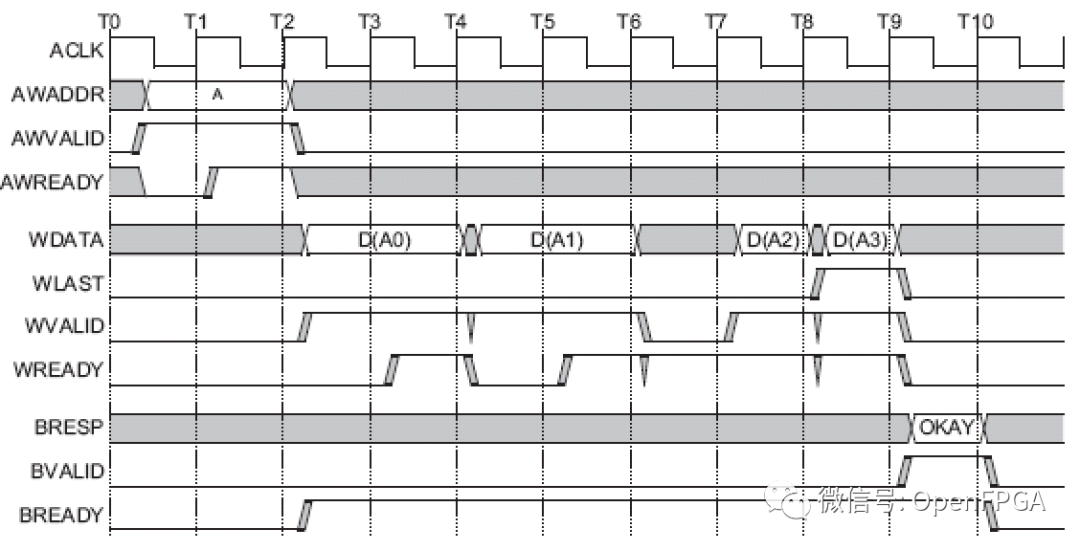

图4‑19 Write Burst 流程

1、当状态机的当前状态为WAIT_START时,master将AWVALID拉高。

2、slave收到AWVALID信号后,将AWREADY拉高,持续到一次burst_len写完为止.master收到AWREADY拉高的信号后,将AWVALID拉低。

3、AWADDR在AWVALID为高时给定对应地址。

4、WREADY信号在收到WVALID信号为高时拉高,保持一个周期,写入数据。

5、WVALID信号由slave控制,具体控制模式参考slave模块说明。

6、当一次写入的最后一个数据包读取时将WLAST拉高,表示一次写入完毕。

7、BRESP和BVALID都由slave控制,当收到WLAST信号时,BVALID拉高。

8、BREADY可以一直拉高,也可以在AWREADY信号拉高后保持拉高。直到BVALID信号拉高时将其拉低即可。

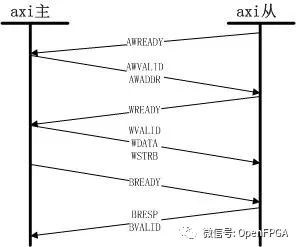

其中写操作的信号依赖关系如下:

图4‑20 写操作依赖

如图可知,ADDR和DATA两个channel之间不存在依赖关系,需要满足的是必须等到WVALID和WREADY同时为High,且最后一次传输完成后,BVALID才能拉高,表明写操作结束。

通道握手信号之间的依赖关系

为了对VALID和READY之间的关系有更深刻理解,下面在展开说明一下。

为了防止发生死锁,必须重视握手信号之间的依赖关系。

任何交易中:

l一个 AXI 模块的VALID 信号不能依赖于另一个模块的READY 信号

lREADY 信号可以等待VALID 信号使能

-------------------注意---------------------------------------------

可以在使能 VALID 信号之后使能READY,也可以在使能VALID 信号之前将

READY 信号使能为默认值,这样设计更高效。.

--------------------------------------------------------------------

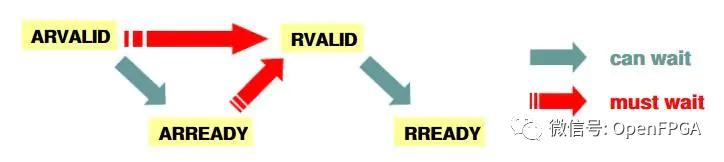

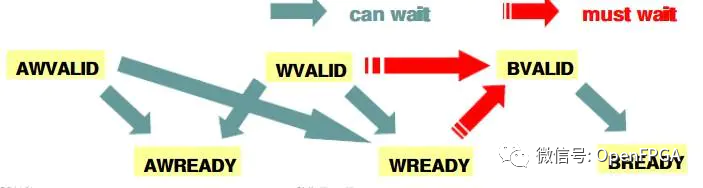

图4‑21和图4‑22为各握手信号之间的依赖关系图。单箭头指向的信号可以在指向它的信号未使能或使能后,它再使能;双箭头向的信号,必须在指向它的信号全都使能后,它再使能。

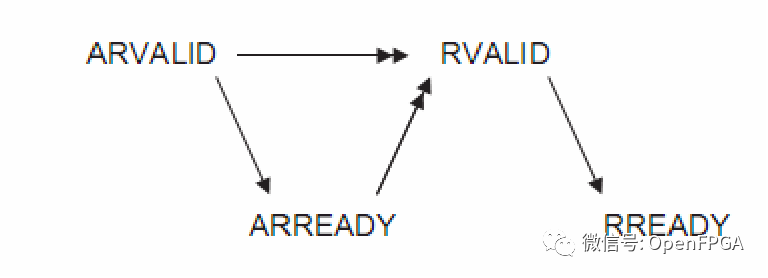

图4‑21中所示,在一次读交易中:

l从设备使能ARREADY 信号之前,可以在等待 ARVALID 信号被使能。

l从设备必须等待ARVALID 和ARREADY信号都有效后,再去使能RVALID 信号以返回读数据

图4‑21 读交易中握手信号的依赖关系

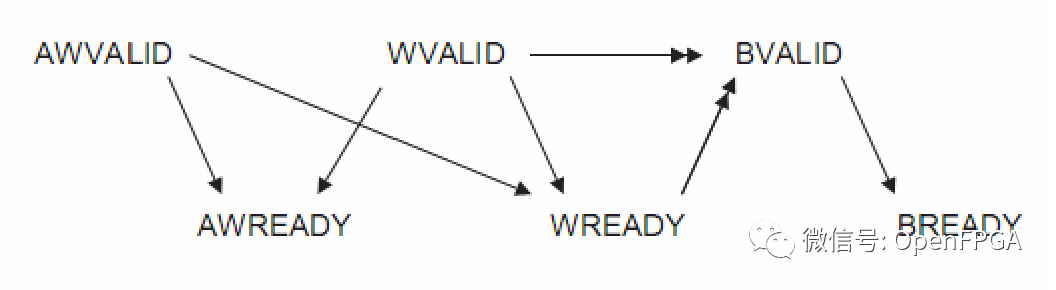

图4‑22中所示,在一次写交易中:

l主设备必须等待从设备使能AWVALID 、WVALID信号之后,主设备再去使能AWREADY 、WREADY信号。

l从设备可以等待使能AWREADY、WVALID信号或者同时使能俩个信号后,再去使能AWREADY。

l从设备可以等待使能AWREADY、WVALID信号或者同时使能俩个信号后,再去使能AWREADY。

l从设备可以等待使能AWREADY、WVALID信号或者同时使能俩个信号后,再去使能AWREADY。

图4‑22 写交易握手信号依赖关系

注意:

在一次写交易中,主设备不必等AWREADY 有效之后去发送WVALID ,这一点是很重要的。如果主设备在发送WVALID 信号之前,必定不会等待使能AWREADY 信号,反过来如果从设备在等待使能WVALID 信号,再去使能AWREADY则这样就会造成死锁状况。

AXI协议中的基本交易

本部分给出基于 AXI协议的基本交易的示例。每个示例都使用了VALID 和READY握手机制。地址信息及数据的传输都是在VALID 和READY 信号同时为高的时候传输。示例下面几部分介绍:

Ø读猝发示例

Ø连续的读猝发示例

Ø写猝发示例

本部分也介绍了交易顺序。

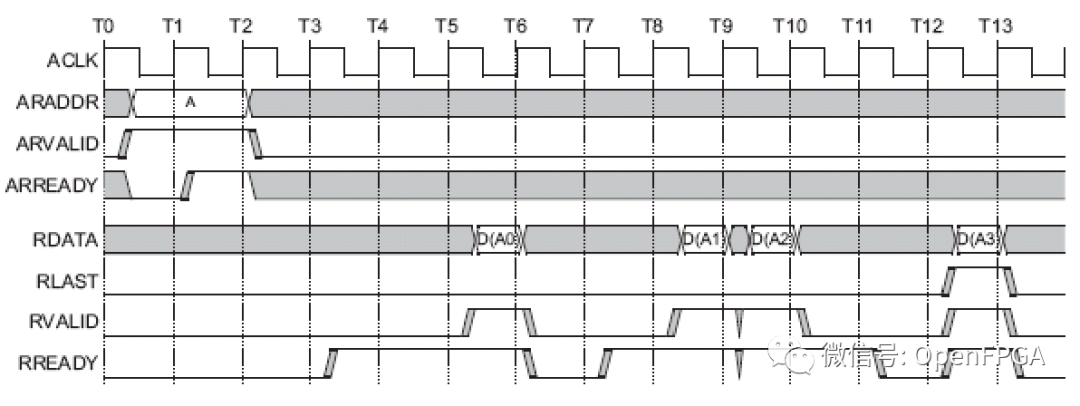

读猝发示例

图4‑23为一个4 拍的读猝发 交易的时序图。在这个例子中,主设备发送地址,一个周期后从设备接收。

主设备在发送地址的同时也发送了一些控制信息,用于记录猝发的类型和长度,为了保持图的清晰性,在此省略这些信号。

地址总线上出现地址之后,在读数据通道上发生数据的传输。从设备一直保持

VALID 信号为低,直到读数据准备好。从设备发送RLAST 信号标志着此次猝发交易中这是最后一个数据的传输。

图4‑23 读猝发交易

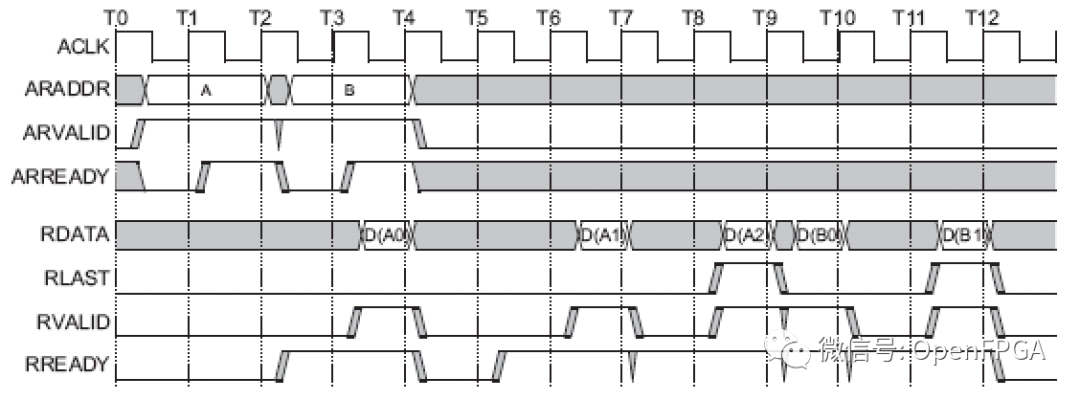

交叠读猝发示例

图4‑24为主设备在从设备接收第一个猝发交易的地址后发送另一个猝发交易的地址的时序图。这样可以保证一个从设备在完成第一个猝发交易的同时可以开始处理第二个猝发 交易的数据。

图4‑24 交叠读猝发交易

写猝发示例

图4‑25为一次写交易的时序图。当主设备发送地址和控制信息到写地址通道之后,交易过程开始。然后主设备通过写数据通道发送每一个写数据,当为最后一个需要发送的数据时,主设备将WLAST 信号置高。当从设备接收完所有的数据时,从设备返回给主设备一个写响应信号标志本次写交易的结束。

图4‑25 写猝发交易

信号描述

定义了AXI协议中使用的信号。虽然总线宽度和交易ID的宽度都是需要具体说明的,但在本章的表中先显示32位的数据总线,一个4位的写入数据选通,和4位的ID域。本章包含以下几个部分:

l全局信号

l写地址通道信号

l写数据通道信号

l写响应通道信号

l读地址通道信号

l读数据通道信号

l低功耗接口信号

全局信号

表4‑12 AXI全局信号

| 信号名 | AXI4 | AXI4-Lit |

| ACLK | 全局时钟。所有的信号在全局时钟的上升沿采样 | |

| ARESETN | 全局复位,低有效。 |

写地址通道信号

表4‑13 写地址通道信号

| 信号名 | 源 | AXI4 | AXI4-Lit |

| AWID | 主 | 写地址ID。这个信号用于写地址信号组的标记。 | 不支持 |

| AWADDR | 主 | 写地址。写地址给出突发数据传输的第一个传输地址。 | |

| AWLEN | 主 | 突发长度。给出突发传输中准确的传输个数。支持INCR和WRAP传输模式。 | 不支持 |

| AWSIZE | 主 | 突发大小。这个信号用于确定突发传输中每个传输的大小。 | 不支持 |

| AWBURST | 主 | 突发类型。该信息与突发大小信息一起,表示在突发过程中,地址如何应用于每个传输。支持INCR和WRAP传输模式。 | 不支持 |

| AWLOCK | 主 | 锁类型。该信号提供了关于传输原子特性的额外信息(普通或互斥访问)。 | 不支持 |

| AWCACHE | 主 | 缓存类型,建议值为0011。 | |

| AWPROT | 主 | 保护类型,建议值为000。 | |

| AWQOS | 主 | QoS标识符,xilinx AXI4不支持。 | 不支持 |

| AWREGION | 主 | 用于每个写操作的地址通道上的域标识符。 | 不支持 |

| AWUSER | 主 | xilinx AXI4不支持。 | 不支持 |

| AWVALID | 主 | 写地址有效信号。为高指示地址有效。 | |

| AWREADY | 从 | 写地址准备信号。为高表示从设备空闲,准备接收地址;为低表示从设备忙。 |

写数据通道信号

表4‑14 写数据通道信号

| 信号名 | 源 | AXI4 | AXI-Lite |

| WDATA | 主 | 写数据,32位到1024位宽 | 只支持32位宽 |

| WSTRB | 主 | 写字节选通,用于表示更新存储器的字节通道,对于数据总线的每8位数据有一位写选通信号。 | 从设备端可选择忽略。 |

| WLAST | 主 | 写最后一个数据指示信号。表示突发传输中的最后一个数据。 | 不支持 |

| WUSER | 主 | xilinx AXI4不支持。 | 不支持 |

| WVALID | 主 | 写有效。为高指示数据有效。 | |

| WREADY | 从 | 写准备。为高表示从设备空闲,准备接收数据;为低表示从设备忙。 |

写响应通道信号

表4‑15 写响应通道信号

| 信号名 | 源 | AXI4 | AXI-Lite |

| BID | 从 | 响应ID。写响应识别标记,BID值必须匹配AWID值。 | 不支持 |

| BRESP | 从 | 写响应。该信号表示写状态,可允许相应的表示为OKAYEXOKAYSLVERRDECERR。 | EXOKAY状态不支持 |

| BUSER | 从 | xilinx AXI4不支持。 | 不支持 |

| BVALID | 从 | 写响应有效。为高指示响应数据有效。 | |

| BREADY | 主 | 写响应准备。为高表示主设备空闲,准备接收写响应;为低表示主设备忙。 |

读地址通道信号

表4‑16 读地址通道信号

| 信号名 | 源 | AXI4 | AXI-Lite |

| ARID | 主 | 读地址ID。这个信号用于读地址信号组的标记。 | 不支持 |

| ARADDR | 主 | 读地址。读地址给出突发数据传输的第一个传输地址。 | |

| ARLEN | 主 | 突发长度。给出突发传输中准确的传输个数。支持INCR和WRAP传输模式。 | 不支持 |

| ARSIZE | 主 | 突发大小。这个信号用于确定突发传输中每个传输的大小。 | 不支持 |

| ARBURST | 主 | 突发类型。该信息与突发大小信息一起,表示在突发过程中,地址如何应用于每个传输。支持INCR和WRAP传输模式。 | 不支持 |

| ARLOCK | 主 | 锁类型。该信号提供了关于传输原子特性的额外信息(普通或互斥访问)。 | 不支持 |

| ARCACHE | 主 | 缓存类型,建议值为0011。 | |

| ARPROT | 主 | 保护类型,建议值为000。 | |

| ARQOS | 主 | QoS标识符,xilinx AXI4不支持。 | 不支持 |

| ARREGION | 主 | 用于每个读操作的地址通道上的域标识符。 | 不支持 |

| ARUSER | 主 | xilinx AXI4不支持。 | 不支持 |

| ARVALID | 主 | 读地址有效信号。为高指示地址有效。 | |

| ARREADY | 从 | 读地址准备信号。为高表示从设备空闲,准备接收地址;为低表示从设备忙。 |

读数据通道信号

表4‑17 读数据通道信号

| 信号名 | 源 | AXI4 | AXI-Lite |

| RID | 从 | 读ID标记,该信号是读数据信号组标记,由从设备产生RID,RID必须和读交易中的ARID匹配。 | 不支持 |

| RDATA | 从 | 读数据。32位到1024位宽 | 只支持32位宽 |

| RRESP | 从 | 读响应。该信号表示读状态,可允许相应的表示为OKAYEXOKAYSLVERRDECERR。 | EXOKAY状态不支持 |

| RLAST | 从 | 读最后一个数据指示信号。表示突发传输中的最后一个数据。 | 不支持 |

| RUSER | 从 | xilinx AXI4不支持。 | 不支持 |

| RVALID | 从 | 读有效。为高指示数据有效。 | |

| RREADY | 主 | 读准备。为高表示主设备空闲,准备接收数据;为低表示主设备忙。 |

AXI4-Stream信号

| 信号名 | 源 | 默认值 | 功能 |

| TVALID | No | N/A | Stream读写数据有效。为高指示数据有效。 |

| TREADY | Yes | 1 | Stream读写读准备。为高表示对端设备空闲,准备接收数据;为低表示对端设备忙。 |

| TDATA | Yes | 0 | Stream读写数据,8到4096位宽。 |

| TSTRB | Yes | 同TKEEP,否则为1 | 字节选通信号。用于表示更新存储器的字节通道,对于数据总线的每8位数据有一位选通信号。 |

| TKEEP | Yes | 1 | 字节选通信号。TKEEP未被确认的那些相关的字节是空字节,可以从数据流中去除。 |

| TLAST | Yes | 0 | 表明包的边界。 |

| TID | Yes | 0 | 数据流标识符。 |

| TDEST | Yes | 0 | 数据流路由信息。 |

| TUSER | Yes | 0 | 用户定义的边带信息,这些信息能伴随数据流进行发送。 |

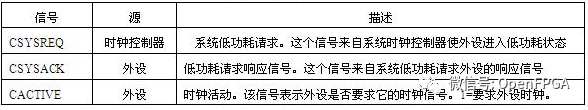

低功耗接口信号

表4‑18 低功耗接口信号

AXI4猝发地址及选择

地址选择

主要描述AXI猝发类型、在一次猝发过程中如何计算地址以及字节传输的通道。包含章节如下:

●关于地址选择

●猝发长度

●猝发大小

●猝发类型

●猝发地址

关于地址选择

AXI协议是基于猝发方式,主设备开始每次的猝发,是通过发送传输所需的控制信息和传输过程中所需的首字节地址的方式,随着猝发交易进行,从设备负责计算接下来的传输所需要的地址。

猝发数不能超过4KB临界值,这是为了防止猝发长度在从设备之间出现交叉现象,同时也限制了从设备需要地址增量的大小。

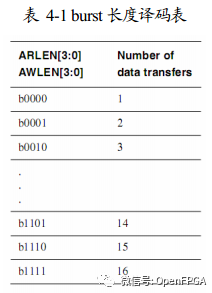

猝发长度

AWLEN 或ARLEN信号说明每次猝发传输开始时,数据传输的个数,如下图所示,每猝发可以传输长1-16个数据。

图4‑26 每猝发可以传输长1-16个数据

对于循回猝发方式来讲,猝发的长度必须是2,4,8,或16。

每次交易进行时,必须通过设置AWLEN 或ARLEN信号来确定传输长度,任何器件都不能通过尽早地终止猝发的方式去减少数据传输个数。在一次写猝发的过程中,主设备通过禁止写选通信号的方式终止进一步的写操作,但是它必须完成本次猝发中剩下数据传输。在一次读猝发过程中,主设备能丢弃进一步的读到数据,但是它必须完成在本次猝发中剩下的数据传输。

-------------------注意---------------------------------------------

当访问一个读敏感设备例如FIFO时,抛弃不需要的读数据会导致丢失数据。主设备不会来访问这样一种设备,它使用的猝发长度比自身需要的还长。--------------------------------------------------------------------

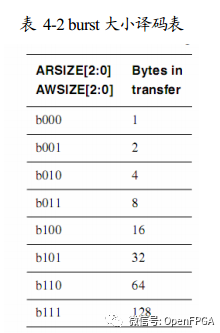

猝发大小

下图中显示, 通过ARSIZE 或AWSIZE信号设定了,在一次猝发中,每一时钟节拍内传输数据字节的最大字节数,或数据传输的最大字节数。

图4‑27 burst大小译码表

AXI协议通过传输地址来决定使用哪一个数据总线上的字节通道进行传输。

对于地址递增或地址循回的猝发,并且要求传输数据的宽度比数据总线上的要窄,这中猝发过程中,每次数据传输,使用不同的字节通道,这些通道对应于猝发中每一个时钟节拍。一个固定格式的猝发,其地址保持不变,每拍数据传输都使用相同的字节通道。

任何数据传输的宽度都不能超过交易中期间的数据总线宽度。

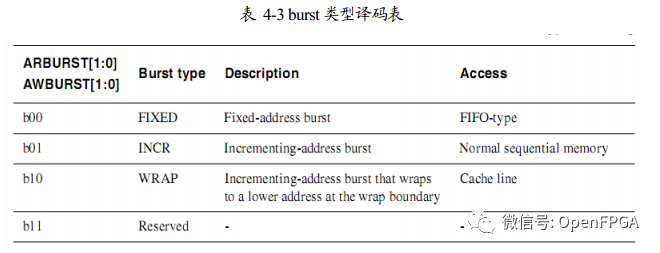

猝发类型

AXI 协议定义了三种猝发类型:

●地址固定的猝发

●地址递增的猝发

●地址循回的猝发

下图显示了如何通过ARBURST 或 AWBURST信号选择猝发类型。

图4‑28 burst类型译码表

地址固定的猝发

在固定猝发类型中,猝发过程中,每次传输地址保持一样。如当加载或者清空一个FIFO外设时,使用这种类型可以重复访问同一个位置。

地址递增的猝发

在地址递增的猝发类型中,猝发中每次传输所需的地址是通过增加前一个传输地址来得到。增加的值取决于传输量的大小。例如:一次猝发中,每次传输所需的地址为四个字节,那么这个地址就是有前一个地址值加四得到的。

地址循回的猝发

地址循回的猝发类型类似于地址递增猝发类型,在地址递增猝发类型中,每次传输所需的地址值是前一次传输地址的递增,而在地址循回猝发类型中,当到达循回的边界时,地址再次回到低地址。循回的边界是指,每次猝发的大小乘以该猝发过程的传输总量。

对于地址循回的猝发有两个限制:

●起始地址必须与数据的大小对齐

●猝发的长度必须为 2,4,8 或16

猝发地址

这一节提供一些简单的公式,在猝发过程中,用于确定地址和传输字节通道。公式中使用到的变量如下:

Start_Address 主设备发起的起始地址

Number_Bytes 每次数据传输中允许的最大的字节数

Data_Bus_Bytes 数据总线上的字节通道数

Aligned_Address 与起始地址对齐的类型

Burst_Length 一次猝发中数据传输的总量

Address_N 猝发中传输N的地址,N是2-16之间的一个整数。

Wrap_Boundary 一次循回猝发中的最低地址

Lower_Byte_Lane 一次传输中最低地址对应的字节通道

Upper_Byte_Lane 一次传输中最高地址对应的字节通道

INT(x) x四舍五入后的值

使用如下公式确定猝发过程中的传输地址 :

● Start_Address = ADDR

● Number_Bytes=2SIZE

● Burst_Length= LEN+1

●Aligned_Address=(INT(Start_Address / Number_Bytes))x Number_Bytes

使用如下公式确定猝发中首次传输所需的地址

●Address_1 = Start_Address .

使用如下公式确定猝发中首次传输后任何传输所需的地址

●Address_N = Aligned_Address+(N–1) x Number_Bytes.

对于循回猝发方式,Wrap_Boundary这个变量用于记录循回的边界:

●Wrap_Boundary =(INT (Start_Address /( Number_Bytesx Burst_Length)))

x(Number_Bytesx Burst_Length).

如果Address_N = Wrap_Boundary +(Number_Bytesx Burst_Length),使用以下公式:

●Address_N = Wrap_Boundary .

计算完循回边界后使用如下公式:

●Address_N = Start_Address +((N–1)x Number_Bytes) - ( Number_Bytesx Burst_Length).

通过使用以下方程可以确定一次猝发中,哪个字节通道用于首次传输

●Lower_Byte_Lane=Start_Address-(INT(Start_Address/ Data_Bus_Bytes))

x Data_Bus_Bytes

●Upper_Byte_Lane=Aligned_Address+(Number_Bytes-1)-(INT ( Start_Address / Data_Bus_Bytes)) x Data_Bus_Bytes.

使用如下公式可以确定一次猝发中,首次传输之后,所有传输都使用了哪些字节通道

●Lower_Byte_Lane= Address_N –(INT ( Address_N / Data_Bus_Bytes)) x Data_Bus_Bytes

●Upper_Byte_Lane= Lower_Byte_Lane+ Number_Bytes–1.

传输的数据公式如下:

●DATA[(8xUpper_Byte_Lane)+7:(8xLower_Byte_Lane)].

-

PCIE项目中AXI4 IP核例化详解2019-12-13 0

-

请问microblaze如何通过串口读写FPGA内部axi4总线上的寄存器?2020-12-23 0

-

AXI4协议的读写通道结构2021-01-08 0

-

看看在SpinalHDL中AXI4总线互联IP的设计2022-08-02 0

-

看看Axi4写通道decoder的设计2022-08-03 0

-

SoC Designer AXI4协议包的用户指南2023-08-10 0

-

AMBA 4 AXI4、AXI4-Lite和AXI4-流协议断言用户指南2023-08-10 0

-

AXI4接口协议的基础知识2020-09-23 5539

-

一文详解ZYNQ中的DMA与AXI4总线2020-09-24 4403

-

ZYNQ中DMA与AXI4总线2020-11-02 3936

-

深入AXI4总线一握手机制2021-03-17 712

-

AXI4 、 AXI4-Lite 、AXI4-Stream接口2022-07-04 6102

-

AXI3与AXI4写响应的依赖区别2023-03-30 720

-

Xilinx FPGA AXI4总线(一)介绍【AXI4】【AXI4-Lite】【AXI-Stream】2023-06-21 1874

-

漫谈AMBA总线-AXI4协议的基本介绍2024-01-17 378

全部0条评论

快来发表一下你的评论吧 !