FPGA时序约束案例:伪路径约束介绍

电子说

描述

伪路径约束

在本章节的“2 约束主时钟”一节中,我们看到在不加时序约束时,Timing Report会提示很多的error,其中就有跨时钟域的error,我们可以直接在上面右键,然后设置两个时钟的伪路径。

这样会在xdc中自动生成如下约束:

set_false_path -from [get_clocks -of_objects [get_pins clk_gen_i0/clk_core_i0/inst/mmcm_adv_inst/CLKOUT0]] -to [get_clocks -of_objects [get_pins clk_gen_i0/clk_core_i0/inst/mmcm_adv_inst/CLKOUT1]]

其实这两个时钟我们已经在前面通过generated指令创建过了,因此get_pins那一长串就没必要重复写了,所以我们可以手动添加这两个时钟的伪路径如下:

set_false_path -from [get_clocks clk_rx] -to [get_clocks clk_tx]

伪路径的设置是单向的,如果两个时钟直接存在相互的数据的传输,则还需要添加从clk_tx到clk_rx的路径,这个工程中只有从rx到tx的数据传输,因此这一条就可以了。

在伪路径一节中,我们讲到过异步复位也需要添加伪路径,rst_pin的复位输入在本工程中就是当做异步复位使用,因此还需要添加一句:

set_false_path -from [get_ports rst_pin]

对于clk_samp和clk2,它们之间存在数据交换,但我们在前面已经约束过asynchronous了,这里就可以不用重复约束了。

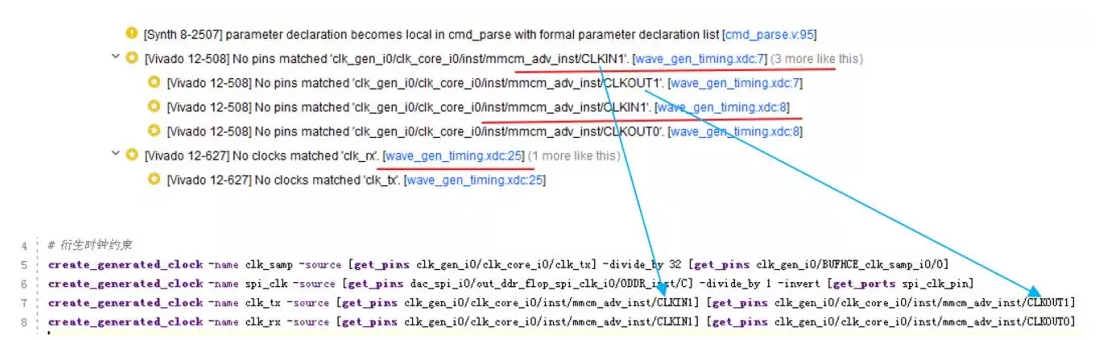

这里需要提示一点,添加了上面这些约束后,综合时会提示xdc文件的的warning。

但这可能是Vivado的综合过程中,读取到该约束文件时,内部电路并未全都建好,就出现了没有发现clk_gen_i0/clk_core_i0/inst/mmcm_adv_inst/CLKIN1等端口的情况,有如下几点证明:

若把该xdc文件,设置为仅在Implementation中使用,则不会提示该warning

在Implementation完成后,无论是Timing Report还是通过tcl的report_clocks指令,都可以看到这几个时钟已经被正确约束。

编辑:hfy

-

FPGA时序约束OFFSET2015-09-05 0

-

FPGA时序约束的几种方法2016-06-02 0

-

时序约束之时序例外约束2018-09-21 0

-

FPGA时序约束--基础理论篇2023-11-15 0

-

FPGA时序约束方法2015-12-14 769

-

基于FPGA 和 SoC创建时序和布局约束以及其使用2017-11-17 2501

-

FPGA约束的详细介绍2018-06-25 6453

-

FPGA设计之时序约束2022-03-18 1384

-

FPGA的IO口时序约束分析2022-09-27 1477

-

FPGA主时钟约束详解 Vivado添加时序约束方法2023-06-06 7423

-

FPGA时序约束之衍生时钟约束和时钟分组约束2023-06-12 1504

-

FPGA时序约束之伪路径和多周期路径2023-06-12 1066

-

FPGA时序约束之时序路径和时序模型2023-08-14 535

-

FPGA I/O口时序约束讲解2023-08-14 990

全部0条评论

快来发表一下你的评论吧 !